10191F

## DESCRIPTION

The 10191 is a Hex ECL to MST (IBM 370) translator. With a standard 10,000 series logic level on the input, the output responds with an identical MST logic level at the output.

In addition, the translators have a common enable line which drives all six outputs to the low state when an ECL logic "1" level is present on the line.

The 10191 is a companion device to the 10190 which is an MST to ECL translator. With these two devices, a complete, high-speed interface is available to communicate between a standard 10,000 series ECL system and a standard MST system.

## **FEATURES**

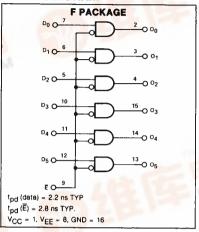

- · High speed; propagation delay = 2.2ns TYP

- · Six translators per package

- · 90 OHM output drive capability

- · Common enable input

- · High impedance inputs with 50K pulldown resistors

- · Open emitter outputs

# **TRUTH TABLE**

| Ē      | Dn | On |  |

|--------|----|----|--|

| 0      | 0  | 0  |  |

| 0      | 1  | 1  |  |

| D=\1/6 | X  | 0  |  |

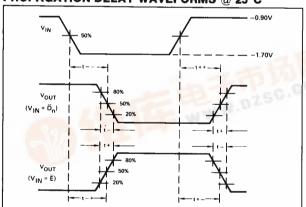

# PROPAGATION DELAY WAVEFORMS @ 25°C

#### NOTES:

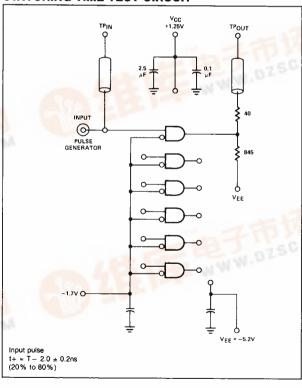

- 1. Each ECL 10,000 series device has been designed to meet the DC specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Voltage levels will shift approximately 4 mV with an air flow of 200 linear fpm. Outputs are terminated through a 900 to gnl and a 8450 to V<sub>EE</sub>.

2. For AC tests, all input and output cables to the scope are equal lengths of 50-ohm coaxial

- 2. For AC tests, all input and output cables to the scope are equal lengths of 50-ohm coaxial cable. Wire lengths should be <¼ inch from TP<sub>in</sub> to input pin and TP<sub>out</sub> to output pin. A 50-ohm termination to ground is located in each scope input. Unused outputs are connected to a 90-ohm registry to ground and exist to the coaxial.

- nected to a 90-ohm resistor to ground and a 845Ω to VEE.

3. Test procedures are shown for only one input or set of input conditions. Other inputs are tested in the same manner.

# **LOGIC DIAGRAM**

# **SWITCHING TIME TEST CIRCUIT**