#### 查询AMC1210IRHAR供应商

#### 捷多邦,专业PCB打样工厂,24小时加急出货

AMC1210

CLK

RST

INT

ACK

CS

MO

M1

AD0

AD7

Interface

Module

WWW.DZSC.

SBAS372A-APRIL 2006-REVISED OCTOBER 2006

# Quad Digital Filter for 2nd-Order Delta-Sigma Modulator

#### **FEATURES**

- Four Independently-Programmable Digital Filters

- Four Window Comparators

- Three Parallel and One Serial Interface

- Comprehensive Interrupt System

- Programmable Input Configuration

- Carrier Frequency Generator for Resolver Applications

Resolver

-0000

ADS1203

ADS1205

ADS1205

ADS1204

0000

PWM1

PWM2

IN1

Input

CLK1

IN2

CLK

IN3

IN4

CLK4

ISO

721

FILTER MODULE 1

Comparato

Filter

Sinc Filter

Integrato

Time Measure

**FILTER**

MODULE 2

FILTER

MODULE 3

FILTER

MODULE 4

## **APPLICATIONS**

Current

Shunt

Resisto

- Current Measurement

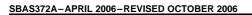

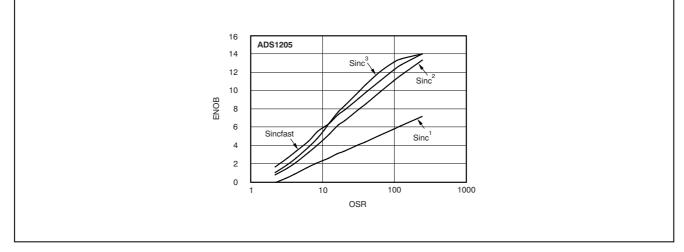

- Resolver Decoding

## DESCRIPTION

AMC1210

**Control Module**

Signal

Generator

Interrupt

Unit

Register

Map

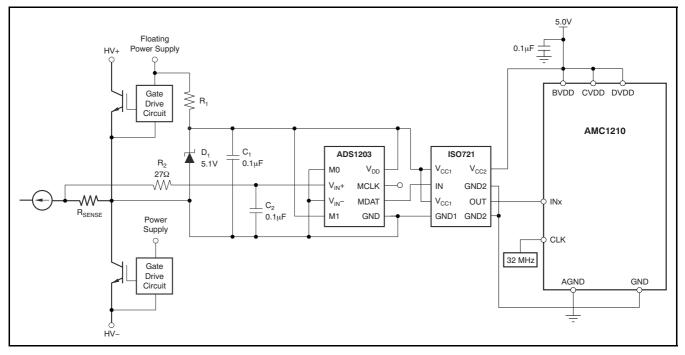

The AMC1210 is a four-channel digital filter designed specifically for current measurement and resolver position decoding in motor control applications. Each input can receive an independent delta-sigma ( $\Delta\Sigma$ ) modulator bit stream. The bit streams are processed by four individually-programmable digital decimation filters. The AMC1210 also offers a flexible interface and a comprehensive interrupt unit, allowing customized digital functionality and immediate digital threshold comparisons for over-current monitoring.

#### SBAS372A-APRIL 2006-REVISED OCTOBER 2006

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

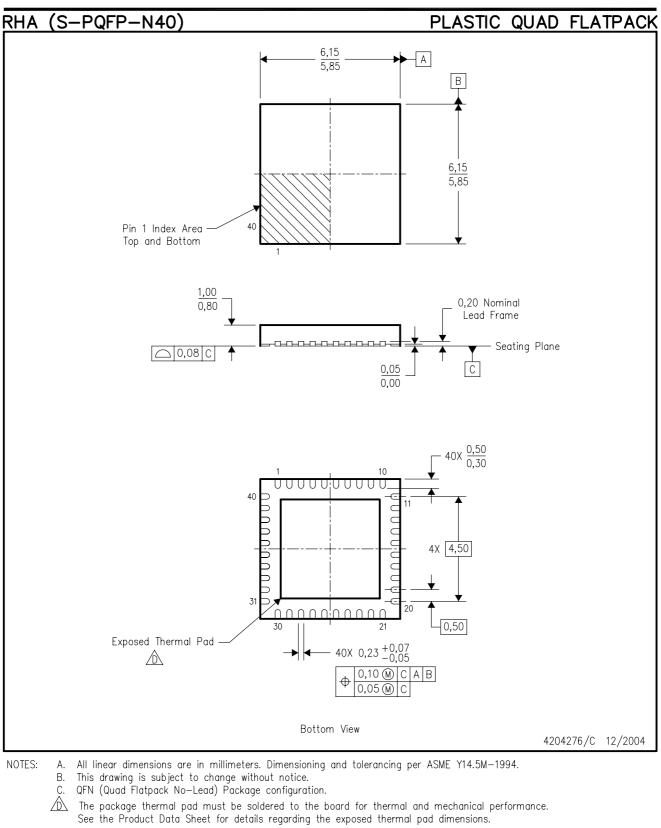

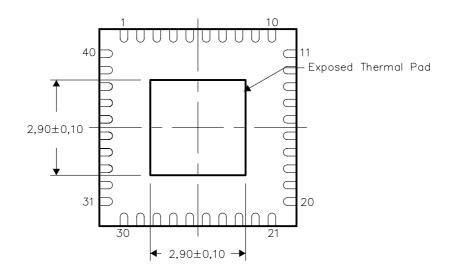

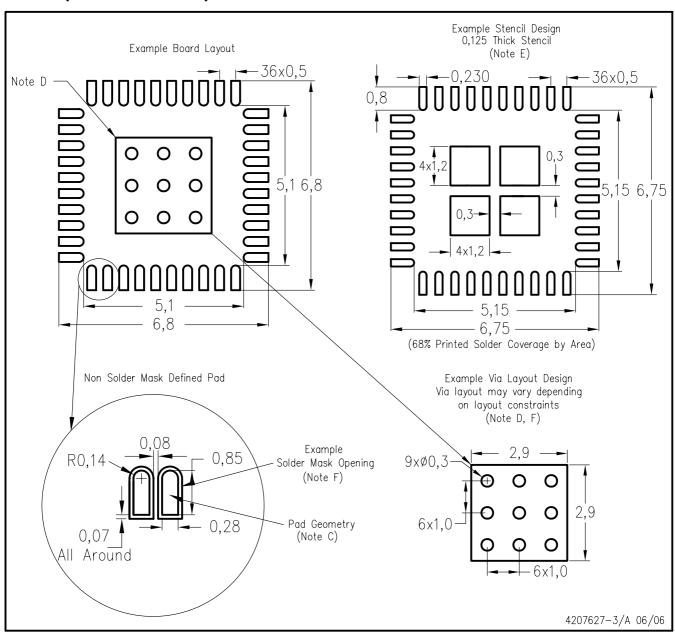

#### **ORDERING INFORMATION**<sup>(1)</sup>

| PRODUCT    | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |

|------------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|---------------------------------|

| AMC1210    | QFN-40       | RHA                   | –40°C to +125°C                   | AMC12101           | AMC1210IRHAT       | Tape and Reel, 250              |

| AIVIC 1210 | QFN-40       | КПА                   | -40 C 10 +125 C                   | AMC1210I           | AMC1210IRHAR       | Tape and Reel, 2500             |

(1) For the most current specifications and package information, see the Package Option Addendum located at the end of this data sheet or refer to our web site at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                              | AMC1210                       | UNIT |  |

|--------------------------------------------------------------|-------------------------------|------|--|

| Supply voltage, all supplies (AVDD, BVDD, CVDD, DVDD) to GND | -0.3 to +6                    | V    |  |

| Digital input to GND                                         | GND - 0.3 to BVDD + 0.3       | V    |  |

| Ground voltage difference, AGND to GND                       | ±0.3                          | V    |  |

| Input current to any pin except supply                       | -10 to +10                    | mA   |  |

| Power dissipation                                            | See Dissipation Ratings Table |      |  |

| Operating virtual junction temperature range, T <sub>J</sub> | -40 to +150                   | °C   |  |

| Operating free-air temperature range, T <sub>A</sub>         | -40 to +125                   | °C   |  |

| Storage temperature range, T <sub>STG</sub>                  | -65 to +150                   | °C   |  |

| Lead temperature, 1,6mm (1/16-inch) from case for 10 seconds | +260                          | °C   |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under the Electrical Characteristics is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

## **DISSIPATION RATINGS**

| PACKAGE            | T <sub>A</sub> ≤ +25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = +25°C | T <sub>A</sub> = +70°C<br>POWER RATING | T <sub>A</sub> = +85°C<br>POWER RATING | T <sub>A</sub> = +125°C<br>POWER RATING |

|--------------------|----------------------------------------|-------------------------------------------------|----------------------------------------|----------------------------------------|-----------------------------------------|

| RHA <sup>(1)</sup> | 3787mW                                 | 30.3mW/°C                                       | 2424mW                                 | 1969mW                                 | 758mW                                   |

(1) The thermal resistance (junction-to-ambient) of the RHA package is 32°C/W.

## **ELECTRICAL CHARACTERISTICS**

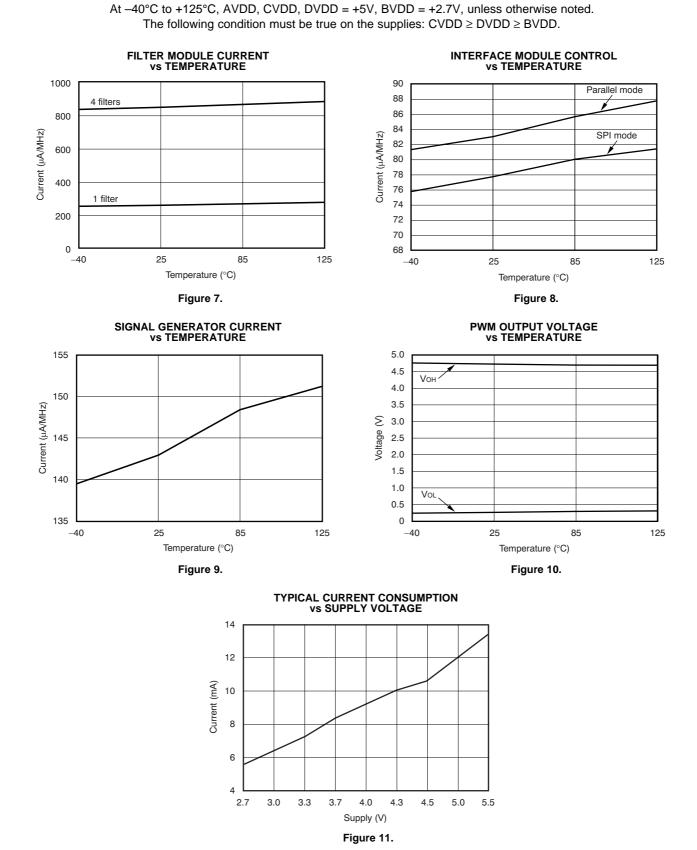

At -40°C to +125°C, AVDD, CVDD, DVDD = 5V, BVDD = 2.7V, unless otherwise noted. The following condition must be true on the supplies:  $CVDD \ge DVDD \ge BVDD$ .

|                                          |                                         | Α    | MC1210 |     |        |

|------------------------------------------|-----------------------------------------|------|--------|-----|--------|

| PARAMETER                                | TEST CONDITIONS                         | MIN  | TYP    | MAX | UNIT   |

| DIGITAL INPUT/OUTPUT                     |                                         |      | L      |     |        |

| Logic levels:                            |                                         |      |        |     |        |

| V <sub>OH</sub>                          | BVDD = 2.7                              | 2.4  |        |     | V      |

|                                          | BVDD = 5.0                              | 4.44 |        |     | V      |

| V <sub>OL</sub>                          | BVDD = 2.7                              |      |        | 0.4 | V      |

|                                          | BVDD = 5.0                              |      |        | 0.5 | V      |

| System clock frequency                   | Pin 'CLK'                               |      |        | 90  | MHz    |

| Modulator clock frequency                | Pins CLK1, CLK2, CLK3, CLK4<br>Mode = 0 |      |        | 22  | MHz    |

| SPI interface clock frequency            | Pin WR, option 1                        |      |        | 25  | MHz    |

| SPI interface clock frequency            | Pin WR, option 2                        |      |        | 40  | MHz    |

| Parallel interface read/write frequency  | Pin CS                                  |      |        | 22  | MHz    |

| POWER SUPPLY REQUIREMENTS                |                                         |      | L      |     |        |

| Power-supply voltage, pin AVDD           |                                         | 4.5  |        | 5.5 |        |

| Power-supply voltage, pins CVDD and DVDD | $CVDD \ge DVDD \ge BVDD$                | 3.3  |        | 5.5 | V      |

| Power-supply voltage, pin DVDD           | $CVDD \ge DVDD \ge BVDD$                | 2.7  |        | 5.5 | V      |

| Total power <sup>(1)</sup>               | All supplies = 5V                       |      | 24.5   |     | mW     |

| Power-supply current                     | One filter module <sup>(2)</sup>        |      | 260    |     | μA/MHz |

| Power-supply current                     | Four filter modules <sup>(2)</sup>      |      | 850    |     | μA/MHz |

|                                          | SPI interface                           |      | 78     |     | μA/MHz |

|                                          | Parallel interface <sup>(3)</sup>       |      | 83     |     | μA/MHz |

|                                          | Signal generator                        |      | 140    |     | μA/MHz |

| SIGNAL GENERATOR OUTPUT                  | · · ·                                   |      |        |     |        |

| V <sub>OH</sub>                          | $R_{LOAD} = 50\Omega$ , bit HPE = 1     | 4.60 | 4.73   |     | V      |

| V <sub>OL</sub>                          | $R_{LOAD} = 50\Omega$ , bit HPE = 1     |      | 0.26   | 0.4 | V      |

| V <sub>OH</sub>                          | $R_{LOAD} = 500\Omega$ , bit HPE = 0    | 4.60 | 4.73   |     | V      |

| V <sub>OL</sub>                          | $R_{LOAD} = 500\Omega$ , bit HPE = 0    |      | 0.26   | 0.4 | V      |

Power consumption with two filter modules functioning, both set to Sinc<sup>3</sup>, SOSR = 256.

The filter module is configured with the comparator unit filter set to Sinc<sup>3</sup>, COSR = 32 and the sinc unit filter set to Sinc<sup>3</sup> structure and SOSR = 256.

(3) All three modes.

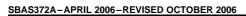

## **DEVICE INFORMATION (continued)** Table 1. TERMINAL FUNCTIONS

| TER | MINAL |               |                                                       |  |  |

|-----|-------|---------------|-------------------------------------------------------|--|--|

| NO. | NAME  | I/O           | DESCRIPTION                                           |  |  |

| 1   | CVDD  |               | Modulator side supply <sup>(1)</sup>                  |  |  |

| 2   | IN1   | Input         | Data input from Modulator 1                           |  |  |

| 3   | CLK1  | Bidirectional | Clock from/to Modulator 1                             |  |  |

| 4   | IN2   | Input         | Data input from Modulator 2                           |  |  |

| 5   | CLK2  | Bidirectional | Clock from/to Modulator 2                             |  |  |

| 6   | IN3   | Input         | Data input from Modulator 3                           |  |  |

| 7   | CLK3  | Bidirectional | Clock from/to Modulator 3                             |  |  |

| 8   | IN4   | Input         | Data input from Modulator 4                           |  |  |

| 9   | CLK4  | Bidirectional | Clock from/to Modulator 4                             |  |  |

| 10  | AVDD  |               | Signal generator supply                               |  |  |

| 11  | PWM1  | Output        | Signal generator output                               |  |  |

| 12  | PWM2  | Output        | Signal generator output (inverted)                    |  |  |

| 13  | AGND  |               | Signal generator ground                               |  |  |

| 14  | DVDD  |               | Core supply                                           |  |  |

| 15  | GND   |               | Ground                                                |  |  |

| 16  | CLK   | Input         | System clock                                          |  |  |

| 17  | SH1   | Input         | First asynchronous sample-and-hold                    |  |  |

| 18  | SH2   | Input         | Second asynchronous sample-and-hold                   |  |  |

| 19  | ACK   | Output        | Acknowledge signal                                    |  |  |

| 20  | INT   | Output        | Interrupt signal                                      |  |  |

| 21  | AD7   | Bidirectional | Data bus bit 7 (most significant bit)                 |  |  |

| 22  | AD6   | Bidirectional | Data bus bit 6                                        |  |  |

| 23  | AD5   | Bidirectional | Data bus bit 5                                        |  |  |

| 24  | AD4   | Bidirectional | Data bus bit 4                                        |  |  |

| 25  | AD3   | Bidirectional | Data bus bit 3                                        |  |  |

| 26  | AD2   | Bidirectional | Data bus bit 2                                        |  |  |

| 27  | AD1   | Bidirectional | Data bus bit 1                                        |  |  |

| 28  | AD0   | Bidirectional | Data bus bit 0 (least significant bit) <sup>(2)</sup> |  |  |

| 29  | GND   |               | Ground                                                |  |  |

| 30  | BVDD  |               | Controller side supply <sup>(3)</sup>                 |  |  |

| 31  | WR    | Input         | Write signal <sup>(2)</sup>                           |  |  |

| 32  | RD    | Input         | Read signal <sup>(2)</sup>                            |  |  |

| 33  | CS    | Input         | Chip select signal <sup>(2)</sup>                     |  |  |

| 34  | ALE   | Input         | Address latch enable <sup>(2)</sup>                   |  |  |

| 35  | MO    | Input         | First mode pin                                        |  |  |

| 36  | M1    | Input         | Second mode pin                                       |  |  |

| 37  | RST   | Input         | Active-low asynchronous reset                         |  |  |

| 38  | TE    | Input         | For factory test only; must be tied to ground         |  |  |

| 39  | DVDD  |               | Core supply                                           |  |  |

| 40  | GND   |               | Ground                                                |  |  |

The pins for the modulator side are 1 to 9.

Functionality is dependent on device setup. To see a list of pin functions/names in each mode, see Table 3.

The pins for the controller side are 16 to 38.

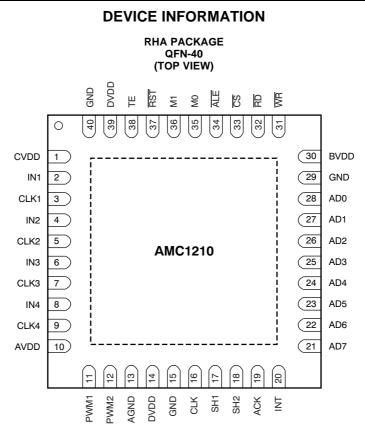

## MODULATOR INPUT MODES

## **TIMING CHARACTERISTICS**

Over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+125^{\circ}$ C, DVDD = +5V, CVDD = +5V, BVDD = +2.7V, unless otherwise noted.

|                  | PARAMETER                                               | MIN                  | MAX                   | UNIT |

|------------------|---------------------------------------------------------|----------------------|-----------------------|------|

| t <sub>w1</sub>  | Mode 0 clock period CLKx                                | 45                   | 1/64th of CLK period  | ns   |

| t <sub>w2</sub>  | Mode 0 clock high time CLKx                             | 10                   | t <sub>w1</sub> –10   | ns   |

| t <sub>su1</sub> | Setup time from data valid to CLKx high                 | 5                    |                       | ns   |

| t <sub>h1</sub>  | Hold time from CLKx high to data invalid                | 5                    |                       | ns   |

| t <sub>w3</sub>  | Mode 1 clock period CLKx                                | 90                   | 1/128th of CLK period | ns   |

| t <sub>w4</sub>  | Mode 1 clock high time CLKx                             | 20                   | t <sub>w3</sub> –10   | ns   |

| t <sub>su2</sub> | Setup time from data valid to CLKx high or low          | 5                    |                       | ns   |

| t <sub>h2</sub>  | Hold time from CLKx high or low to data invalid         | 5                    |                       | ns   |

| t <sub>w5</sub>  | Mode 2 data width INx                                   | 45                   |                       | ns   |

| t <sub>w6</sub>  | Mode 2 data pulse width INx                             | 22                   |                       | ns   |

| t <sub>w7</sub>  | Mode 3 clock period CLKx                                | 22                   | 1/32nd of CLK period  | ns   |

| t <sub>w8</sub>  | Mode 3 clock high time CLKx                             | 5                    | t <sub>w7</sub> –5    | ns   |

| t <sub>su3</sub> | Setup time from data valid to any CLKx high             | 5                    |                       | ns   |

| t <sub>h3</sub>  | Hold time from any CLKx high to data invalid            | 5                    |                       | ns   |

| t <sub>w9</sub>  | System clock period CLK                                 | 11                   | 10 <sup>6</sup>       | ns   |

| t <sub>w10</sub> | System clock high time CLK                              | 3                    | t <sub>w9</sub> –3    | ns   |

| t <sub>w11</sub> | Mode 3 generated clock period CLK <sub>x</sub>          | t <sub>w9</sub>      | tw9 x MD control bits | ns   |

| t <sub>w12</sub> | Mode 3 generated high time CLKx                         | t <sub>w10</sub> - 2 | t <sub>w10</sub> +2   | ns   |

| t <sub>d1</sub>  | Delay from system clock CLK high to generated CLKx high | 0                    | 3                     | ns   |

| t <sub>d2</sub>  | Delay from system clock CLK low to generated CLKx low   | 0                    | 3                     | ns   |

| t <sub>su4</sub> | Setup time from data valid to any CLKx high             | 5                    |                       | ns   |

| t <sub>h4</sub>  | Hold time from any CLKx high to data invalid            | 5                    |                       | ns   |

## Figure 1. Modulator Input Mode Timing

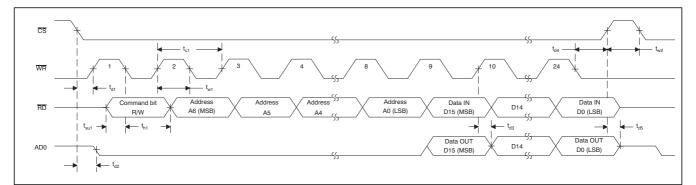

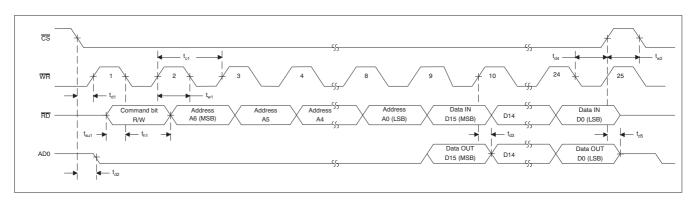

## SPI INTERFACE MODES

## TIMING CHARACTERISTICS<sup>(1)</sup>

Over recommended operating free-air temperature range at -40°C to +125°C, DVDD = +5V, BVDD = +2.7V, unless otherwise noted.

|                  |                                                                        | Opt     | ion 1 | Opt |     |      |

|------------------|------------------------------------------------------------------------|---------|-------|-----|-----|------|

|                  | PARAMETER                                                              | MIN MAX |       | MIN | MAX | UNIT |

| t <sub>c1</sub>  | WR period                                                              | 40      |       | 25  |     | ns   |

| t <sub>w1</sub>  | WR HIGH or LOW time                                                    | 10      |       | 10  |     | ns   |

| t <sub>d1</sub>  | Delay time from $\overline{CS}$ falling to $\overline{WR}$ rising edge | 0       |       | 0   |     | ns   |

| t <sub>d2</sub>  | Delay time from $\overline{CS}$ falling to ADO not tristate            |         | 10    |     | 10  | ns   |

| t <sub>su1</sub> | Data setup time                                                        | 5       |       | 5   |     | ns   |

| t <sub>h1</sub>  | Input data hold time                                                   | 5       |       | 5   |     | ns   |

| t <sub>d3</sub>  | Output data delay time                                                 |         | 24    |     | 24  | ns   |

| t <sub>d4</sub>  | Enable lag time                                                        | 10      |       | 10  |     | ns   |

| t <sub>d5</sub>  | ADO disable time                                                       |         | 10    |     | 10  | ns   |

| t <sub>w2</sub>  | Sequential transfer delay                                              | 15      |       | 15  |     | ns   |

(1) All input signals are specified with  $t_R = t_F = 5$ ns (10% to 90% of BVDD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

Figure 2. SPI Interface Option 1—SPI Normal Interface

Figure 3. SPI Interface Option 2—SPI Fast Interface (> 25MHz)

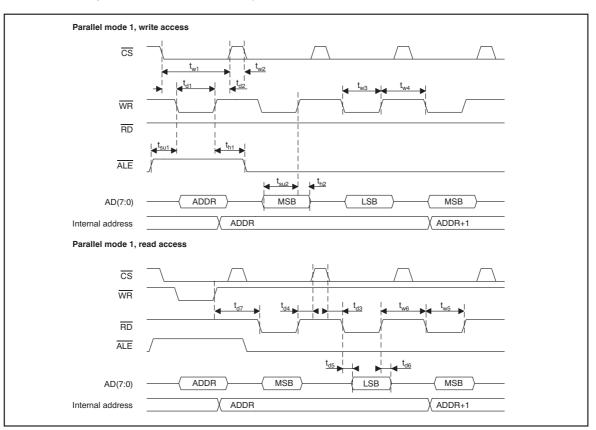

## **PARALLEL MODE 1**

## TIMING CHARACTERISTICS<sup>(1)</sup>

Over recommended operating free-air temperature range at -40°C to +125°C, DVDD = +5V, BVDD = +2.7V, unless otherwise noted.

|                  | PARAMETER <sup>(2)</sup>                                     | MIN | MAX | UNIT |

|------------------|--------------------------------------------------------------|-----|-----|------|

| t <sub>w1</sub>  | CS low width                                                 | 40  |     | ns   |

| t <sub>w2</sub>  | CS high width                                                | 5   |     | ns   |

| t <sub>d1</sub>  | Delay time from CS low to WR low                             | 3   |     | ns   |

| t <sub>d2</sub>  | Delay time from $\overline{WR}$ high to $\overline{CS}$ high | 5   |     | ns   |

| t <sub>w3</sub>  | WR low width                                                 | 10  |     | ns   |

| t <sub>w4</sub>  | WR high width                                                | 10  |     | ns   |

| t <sub>su1</sub> | Setup time from ALE high to WR low                           | 0   |     | ns   |

| t <sub>h1</sub>  | Hold time from WR high to ALE low                            | 2   |     | ns   |

| t <sub>su2</sub> | Setup time from address valid to WR high                     | 6   |     | ns   |

| t <sub>h2</sub>  | Hold time from WR high to address invalid                    | 5   |     | ns   |

| t <sub>d3</sub>  | Delay time from CS low to RD low                             | 0   |     | ns   |

| t <sub>d4</sub>  | Delay time from RD high to CS high                           | 6   |     | ns   |

| t <sub>w5</sub>  | RD low width                                                 | 30  |     | ns   |

| t <sub>w6</sub>  | RD high width                                                | 13  |     | ns   |

| t <sub>d5</sub>  | Delay time from RD low to data valid                         |     | 30  | ns   |

| t <sub>d6</sub>  | Delay time from RD high to databus in tristate               | 0   | 10  | ns   |

| t <sub>d7</sub>  | Delay time from WR high to RD low                            | 10  |     | ns   |

(1) All input signals are specified with  $t_R = t_F = 5ns (10\% \text{ to } 90\% \text{ of BVDD})$  and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . (2)  $t_{w2}$  is obsolete if  $\overline{CS}$  stays low between the  $\overline{WR}$  and  $\overline{RD}$  pulses.

## Figure 4. Parallel Mode 1 Timing

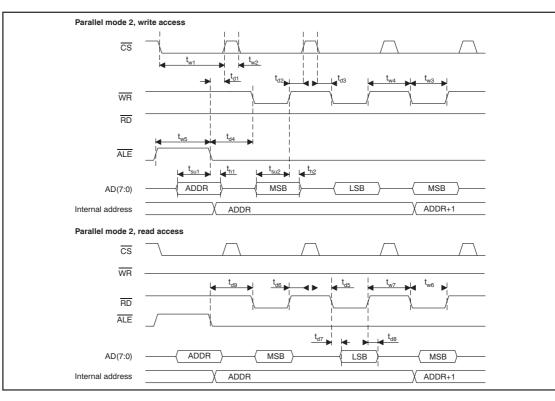

## PARALLEL MODE 2

## TIMING CHARACTERISTICS<sup>(1)</sup>

Over recommended operating free-air temperature range at -40°C to +125°C, DVDD = +5V, BVDD = +2.7V, unless otherwise noted.

|                  | PARAMETER <sup>(2)</sup>                                     | MIN | MAX | UNIT |

|------------------|--------------------------------------------------------------|-----|-----|------|

| t <sub>w1</sub>  | CS low width                                                 | 40  |     | ns   |

| t <sub>w2</sub>  | CS high width                                                | 5   |     | ns   |

| t <sub>d1</sub>  | Delay time from ALE low to CS high                           | 5   |     | ns   |

| t <sub>d2</sub>  | Delay time from $\overline{WR}$ high to $\overline{CS}$ high | 5   |     | ns   |

| t <sub>d3</sub>  | Delay time from $\overline{CS}$ low to $\overline{WR}$ low   | 3   |     | ns   |

| t <sub>w3</sub>  | WR low width                                                 | 10  |     | ns   |

| t <sub>w4</sub>  | WR high width                                                | 10  |     | ns   |

| t <sub>w5</sub>  | ALE high width                                               | 10  |     | ns   |

| t <sub>d4</sub>  | Delay time from ALE low to WR low                            | 10  |     | ns   |

| t <sub>su1</sub> | Setup time from address valid to ALE low                     | 6   |     | ns   |

| t <sub>h1</sub>  | Hold time from ALE low to address invalid                    | 5   |     | ns   |

| t <sub>d5</sub>  | Delay time from CS low to RD low                             | 0   |     | ns   |

| t <sub>su2</sub> | Setup time from data valid to WR high                        | 6   |     | ns   |

| t <sub>h2</sub>  | Hold time from WR high to data invalid                       | 5   |     | ns   |

| t <sub>d6</sub>  | Delay time from RD high to CS high                           | 6   |     | ns   |

| t <sub>w6</sub>  | RD low width                                                 | 30  |     | ns   |

| t <sub>w7</sub>  | RD high width                                                | 13  |     | ns   |

| t <sub>d7</sub>  | Delay time from RD low to data valid                         |     | 30  | ns   |

| t <sub>d8</sub>  | Delay time from RD high to databus in tristate               | 0   | 10  | ns   |

| t <sub>d9</sub>  | Delay time from ALE low to RD low                            | 10  |     | ns   |

(1) All input signals are specified with  $t_R = t_F = 5ns (10\% \text{ to } 90\% \text{ of BVDD})$  and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . (2)  $t_{w2}$  is obsolete if  $\overline{CS}$  stays low between the  $\overline{WR}$ ,  $\overline{RD}$  and  $\overline{ALE}$  pulses.

## Figure 5. Parallel Mode 2 Timing

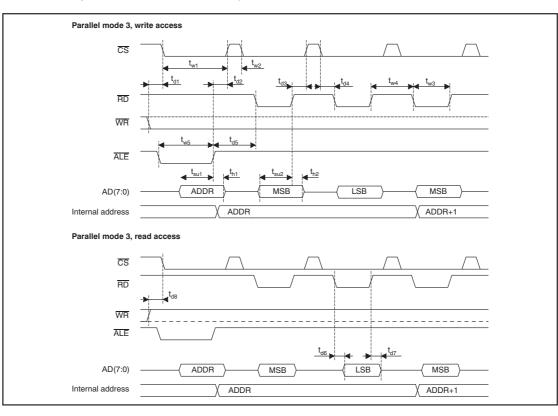

## PARALLEL MODE 3

## TIMING CHARACTERISTICS<sup>(1)</sup>

Over recommended operating free-air temperature range at -40°C to +125°C, DVDD = +5V, BVDD = +2.7V, unless otherwise noted.

|                  | PARAMETER <sup>(2)</sup>                                    | MIN MA | X UNIT |

|------------------|-------------------------------------------------------------|--------|--------|

| t <sub>w1</sub>  | CS low width                                                | 40     | ns     |

| t <sub>w2</sub>  | CS high width                                               | 5      | ns     |

| t <sub>d1</sub>  | Delay time from WR low to CS low                            | 5      | ns     |

| t <sub>d2</sub>  | Delay time from ALE high to CS high                         | 5      | ns     |

| t <sub>d3</sub>  | Delay time from RD high to CS high                          | 5      | ns     |

| t <sub>d4</sub>  | Delay time from CS low to RD low                            | 3      | ns     |

| t <sub>w3</sub>  | RD low width                                                | 10     | ns     |

| t <sub>w4</sub>  | RD high width                                               | 30     | ns     |

| t <sub>w5</sub>  | ALE low width                                               | 6      | ns     |

| t <sub>d5</sub>  | Delay time from ALE high to RD low                          | 10     | ns     |

| t <sub>su1</sub> | Setup time from address valid to ALE high                   | 5      | ns     |

| t <sub>h1</sub>  | Hold time from ALE high to address invalid                  | 5      | ns     |

| t <sub>su2</sub> | Setup time from data valid to RD high                       | 5      | ns     |

| t <sub>h2</sub>  | Hold time from RD high to data invalid                      | 5      | ns     |

| t <sub>d6</sub>  | Delay time from RD low to data valid                        |        | 30 ns  |

| t <sub>d7</sub>  | Delay time from RD high to databus in tristate              | 0      | 10 ns  |

| t <sub>d8</sub>  | Delay time from $\overline{WR}$ high to $\overline{CS}$ low | 5      | ns     |

(1) All input signals are specified with  $t_R = t_F = 5ns (10\% \text{ to } 90\% \text{ of BVDD})$  and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . (2)  $t_{w2}$  is obsolete if  $\overline{CS}$  stays low between the  $\overline{RD}$  and  $\overline{ALE}$  pulses.

## Figure 6. Parallel Mode 3 Timing

SBAS372A-APRIL 2006-REVISED OCTOBER 2006

## TYPICAL CHARACTERISTICS

Submit Documentation Feedback

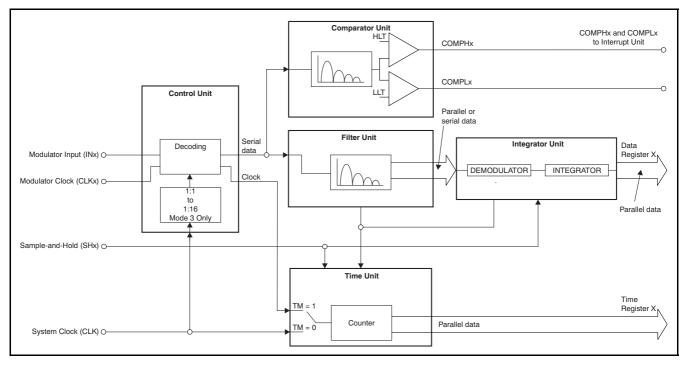

## THEORY OF OPERATION

#### Overview

The AMC1210 is a flexible digital filter device specifically designed for motor control applications. It incorporates four independent digital filters into a digital processing block, allowing communication via SPI bus or 8-bit, multiplexed parallel I/O. Each datastream input can be clocked in using an external clock or a clock provided by a delta-sigma modulator. A time measurement unit allows software monitoring of the sample speed and data acquisition, and a comprehensive control and interrupt unit allows real-time monitoring of the AMC1210 status. A digital comparator unit is provided to alert programmable peak conditions on the different datastreams. When used in current measurement applications, the digital comparator unit can alert a system to over- or under-current situations.

#### Interface Module

The AMC1210 can communicate with digital signal processors (DSPs) or microcontrollers ( $\mu$ Cs) in four different interface modes: one serial mode and three 8-bit, multiplexed parallel modes. The serial mode is a standard SPI mode, normally with a 24-bit transfer. The multiplexed parallel modes are designed to work together with a wide range of controllers. Mode pins M0 and M1 determine the mode selection. Table 2 shows the digital interface configuration.

|                 | •      | •      |

|-----------------|--------|--------|

| INTERFACE MODES | PIN M1 | PIN M0 |

| SPI             | 0      | 0      |

| Parallel Mode 1 | 0      | 1      |

| Parallel Mode 2 | 1      | 0      |

| Parallel Mode 3 | 1      | 1      |

Table 2. Digital Interface Configuration

The digital interface pins perform different functions depending on the interface mode. Table 3 shows the pin operations in different modes.

| PIN | SPI MODE     | PARALLEL MODE 1     | PARALLEL MODE 2      | PARALLEL MODE 3 |

|-----|--------------|---------------------|----------------------|-----------------|

| M1  | 0            | 0                   | 1                    | 1               |

| M0  | 0            | 1                   | 0                    | 1               |

| ALE | -            | Address/Data Select | Address Latch Enable | Address Valid   |

| CS  | Frame sync   | Chip Select         | Chip Select          | Chip Select     |

| RD  | SPI Data In  | Read                | Read                 | Strobe          |

| WR  | SPI Clock    | Write               | Write                | Read/Write      |

| AD0 | SPI Data Out | Databus 0 (LSB)     | Databus 0 (LSB)      | Databus 0 (LSB) |

| AD1 | -            | Databus 1           | Databus 1            | Databus 1       |

| AD2 | -            | Databus 2           | Databus 2            | Databus 2       |

| AD3 | -            | Databus 3           | Databus 3            | Databus 3       |

| AD4 | -            | Databus 4           | Databus 4            | Databus 4       |

| AD5 | -            | Databus 5           | Databus 5            | Databus 5       |

| AD6 | -            | Databus 6           | Databus 6            | Databus 6       |

| AD7 | -            | Databus 7 (MSB)     | Databus 7 (MSB)      | Databus 7 (MSB) |

| Table 3. Pin Functions in Different Communication Modes |

|---------------------------------------------------------|

|---------------------------------------------------------|

## Clock Setup

The clock pin CLK controls the timing of several functions. Table 4 shows the units and features that use the CLK signal for timing.

| MODULE/UNIT                | FEATURE                                 | CLOCK FUNCTION                                                          |  |  |  |  |

|----------------------------|-----------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Interface/Signal Generator | Signal generator                        | Determines output data rate                                             |  |  |  |  |

| Filter/Input Control       | Manchester Decoder in control unit      | Allows decoding of Manchester data                                      |  |  |  |  |

|                            | CLKx signal in control unit             | Provides timing for CLKx pin when bit CD in the control parameter = '1' |  |  |  |  |

|                            | Clock dividers for CLKx in control unit | Divides CLKx speed                                                      |  |  |  |  |

|                            | Modulator failure detection             | Allows AMC1210 to monitor input clock CLKx                              |  |  |  |  |

| Filter/Time Measurement    | Time measurement                        | TMU counts number of CLK cycles when TM = 0                             |  |  |  |  |

| Table 4. CLK Pin Functi | ons |

|-------------------------|-----|

|-------------------------|-----|

If none of the features in this table are needed, the CLK pin should be connected to GND to avoid any increased current consumption.

#### SPI Mode

The SPI interface runs fully asynchronously to the rest of the system. The four signals of the SPI interface are  $\overline{WR}$ ,  $\overline{RD}$ , AD0 and  $\overline{CS}$ . The maximum speed of the SPI interface is 40MHz. When the select signal  $\overline{CS}$  is high, the entire SPI interface is in reset state, except the Address and the Data Register. The SPI clock  $\overline{WR}$  and the serial data input  $\overline{RD}$  are disabled when  $\overline{CS}$  is high. The incoming data is strobed by the SPI interface on the falling edge of the  $\overline{WR}$ . Outgoing data is put on the output AD0 on the rising edge of the  $\overline{WR}$  (see SPI Interface Modes). For a transmission of one 16-bit data word, 24 bits are required. The first incoming bit to the AMC1210 determines if the entire transmission is a read or a write operation. A high bit indicates a read operation, and a low bit indicates a write operation. There are seven address bits. The 16 data bits are transmitted or received after the address bits, according to the sequence shown in Table 5.

#### Table 5. SPI Write 24-Bit Word Format

| A24 | A23 | A22 | A21 | A20 | A19  | A18 | A17 | A16 | MSB<br>A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | LSB<br>A0 |

|-----|-----|-----|-----|-----|------|-----|-----|-----|------------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----------|

| R/W |     |     |     | Add | ress |     |     |     |            |     |     |     |     |     |    | Da | ta |    |    |    |    |    |    |           |

## **SPI Option 1**

In SPI option 1, one 16-bit transfer is accomplished in the following manner:

- 1. On the first falling edge of  $\overline{WR}$ , the read/write bit is strobed.

- 2. On the second falling edge of  $\overline{WR}$ , the MSB of the address (bit 6) is strobed.

- 3. On the eighth falling edge of WR, the LSB of the address (bit 0) is strobed and the corresponding data of the register map is read.

- 4. On the ninth rising edge (MSB), the data read from the register map is latched into a shift register and shifted one position each rising edge of the WR. At speeds below 25MHz, it is recommended to perform a read on the next falling edge (Option 1). This data is always sent out, even when a write operation is performed.

- 5. On the 24th falling edge of WR (LSB), the last data bit is shifted in from RD and a write pulse is generated to write the data into the register map, if a write operation was performed.

Figure 2 and Figure 3 provide detailed timing information for the SPI modes.

#### SBAS372A-APRIL 2006-REVISED OCTOBER 2006

During continuous read or write, the address increments after each read or write. When the address reaches 7Fh, the address counter starts over from 0. The data is written into the register map on the 16th  $\overline{\text{WR}}$  of a data word. If the  $\overline{\text{CS}}$  is inactive before the 16th  $\overline{\text{WR}}$  in a data word, the data is not written into the register map; the data is lost. Figure 12 shows a typical example of this functionality.

| CS  |                                                                                             |

|-----|---------------------------------------------------------------------------------------------|

| WR  | /8 SPICLKs/8 SPICLKs/8 SPICLKs/8 SPICLKs/8 SPICLKs/8 SPICLKs/8 SPICLKs/8 SPICLKs/8 SPICLKs/ |

| RD  | Address 1st Data to write 2nd Data to write 3rd Data to write 4th Data to write             |

| AD0 | Don't care 1st read Data 2nd read Data 3rd read Data 4th read Data                          |

Figure 12. Typical Serial Communication Operation

#### SPI Option 2

SPI option 2 is recommended for use when the clock speed is greater than 25MHz. The only difference between option 1 and 2 is the edge from which the output data is strobed. In option 2, the user should read the data on the rising edge after the data from the register map is latched (one half clock cycle after Option 1). In this case, an extra clock cycle is needed (25 clock cycles instead of 24). See the timing diagram in Figure 3.

### Parallel Mode 1

In Parallel Mode 1, the host port uses  $\overline{WR}$  and  $\overline{RD}$  for independent write and read access to the AMC1210. The current cycle is processed only when the  $\overline{CS}$  input of the AMC1210 is low.  $\overline{RD}$  indicates to the AMC1210 that the host processor has requested a data transfer. The AMC1210 then outputs data to the host.

To configure the registers in the AMC1210, the host process issues a  $\overline{WR}$  signal to indicate that valid data is available on the bus. The data is latched into the AMC1210 with the rising edge of the  $\overline{WR}$ . The address for the AMC1210 must be valid at the first rising edge of  $\overline{WR}$ . To indicate that an address is issued, the signal  $\overline{ALE}$  must be set to high before the  $\overline{WR}$  signal is set to low. The  $\overline{CS}$  signal can stay low between two consecutive writes or reads.

Figure 4 provides a detailed timing diagram of Parallel Mode 1.

#### Parallel Mode 2

In Parallel Mode 2, the host port uses  $\overline{WR}$  and  $\overline{RD}$  for independent write and read access to the AMC1210. The current cycle is processed only when the  $\overline{CS}$  input of the AMC1210 is low.  $\overline{RD}$  indicates to the AMC1210 that the host processor has requested a data transfer. The AMC1210 then outputs data to the host.

To configure the AMC1210 registers, the host process issues a  $\overline{WR}$  signal to indicate that valid data is available on the bus. With the rising edge of  $\overline{WR}$ , the data is latched into the AMC1210. The address is latched into AMC1210 when the signal ALE is set to low. The  $\overline{CS}$  signal can stay low between two consecutive writes or reads.

Figure 5 provides a detailed timing diagram of Parallel Mode 2.

### Parallel Mode 3

In Parallel Mode 3, the host port uses  $\overline{RD}$  and  $\overline{WR}$  for write and read access to the AMC1210. The current cycle is processed only when the  $\overline{CS}$  input of the AMC1210 is low.  $\overline{WR}$  indicates to the AMC1210 that the host processor has initiated a read or write transfer. If  $\overline{WR}$  is high, the AMC1210 outputs data to the host when  $\overline{RD}$  is also low.

To configure the registers in the AMC1210, the host process issues a  $\overline{RD}$  signal together with  $\overline{WR}$  low to indicate that valid data is available on the bus. With the rising edge of the  $\overline{RD}$  signal, the data is latched into the AMC1210. The address is latched into AMC1210 when the signal  $\overline{ALE}$  is set high. The  $\overline{CS}$  signal can stay low between two consecutive writes or reads.

Figure 6 provides a detailed timing diagram of Parallel Mode 3.

In all parallel modes, each address can be accessed sequentially without writing a new address to the AMC1210. When an address is set by the user, a pointer is also set to that address. After each successive read or write operation, the address is incremented by one in the register map.

## **FILTER MODULE**

The filter module consists of the control block unit, the comparator filter unit, the sinc filter unit, a time measurement unit and a demodulator/integrator unit. Each unit can be individually programmed for several different modes of operation. Figure 13 shows a block diagram of one filter module. The four filter modules are identical and are able to be configured independently.

Figure 13. AMC1210 Filter Module

## FILTER MODULE (continued)

## **Control Unit**

The control unit translates the modulator input data and the corresponding clock so that it can be used by the AMC1210. Four input options are available, depending on the mode of the modulator. These options are selected through the bits MOD1 and MOD0 in the Control Parameter Register. Table 6 describes each input mode. A detailed diagram of the timing of each of these modes can be found in the Timing Characteristics section; see Figure 1.

#### Table 6. Interface Modes

| MODULATOR MODE | MOD1 | MOD0 | DESCRIPTION                                                                                                                                        |

|----------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | 0    | 0    | The modulator clock is running with the modulator data rate. The modulator data is strobed at every rising edge of the modulator clock.            |

| 1              | 0    | 1    | The modulator clock is running with half of the modulator data rate. The modulator data is strobed at every edge of the modulator clock.           |

| 2              | 1    | 0    | The modulator clock is off and the modulator data is Manchester-encoded.                                                                           |

| 3              | 1    | 1    | The modulator clock is running with double of the modulator data rate. The modulator data is strobed at every other positive modulator clock edge. |

In Modulator Mode 2, the data is Manchester-encoded. An automatic calibration is continuously performed to achieve optimum decoding performance. The status of this calibration can be checked in the Control Parameter Register bits MS10–MS0 and in the Status Register bits MALx and MAFx. The clock input CLKx is ignored in this mode.

## Input Clocking

The filter module clock is separate from the system clock (except when using Modulator Mode 3). This design permits the filter module to run asynchronously from the control module, allowing two different speeds for input data and control block timing. The clock setup is different for each input mode. See Table 7.

| INPUT MODE | CLOCK FUNCTIONALITY                                                                                                                                                                                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | The clock for the filter module is fed by the CLKx input, which can be either external or driven by the modulator. The frequency is the same.                                                                                                                                                                       |

| 1          | Each edge of CLKx generates a pulse, which clocks the filter module.                                                                                                                                                                                                                                                |

| 2          | The clock for the filter module is generated by the Manchester decoder.                                                                                                                                                                                                                                             |

| 3          | The clock source is the system clock, from the CLK pin. This clock can be divided down by a programmed number between 1 and 8 by bits MD2–MD0 in the Clock Divider Register. This clock can also be fed to the CLKx pin to drive the modulator clock if the bit CD in the Control Parameter Register is set to '1'. |

#### Table 7. Clock Operation in Each Interface Mode

Note that as long as the input data is clocked in correctly, all of the filter module functions (sinc filter unit, comparator unit, etc.) will be clocked at the same rate.

## **Manchester Decoding**

Manchester signaling is a method of encoding a data signal in such a way that it can be retrieved without the need of a separate clock line. When configured in Mode 2, the AMC1210 can translate a Manchester-encoded signal on the INx pin into a clock signal and a data signal. An automatic calibration is continuously performed to optimize the decoding of the data.

The calibration mechanism follows this sequence:

- 1. The modulator data is sampled at the frequency of the system clock (CLK).

- 2. The number of CLK cycles between transitions is counted and recorded for 1024 consecutive transitions.

- 3. The resulting array will have a '1' in the bit location that corresponds to the number of CLK cycles counted between transitions. For example, the sequence shown in Table 8 means that there was at least one instance where three and four, as well as seven and eight, CLK cycles occurred between two transitions. This array is stored in the bits MS10–MS0 in the Control Parameter Register.

- 4. An algorithm looks for a group of zeros that has ones before and after it. If this pattern is not found, the bits MALx and MAFx in the Status Register are set high.

- 5. If the algorithm is successful, it will use the location of the first '0' as the number of CLK cycles needed to determine the frequency and which transitions are valid in the Manchester code.

- 6. The algorithm starts over from Step 2 automatically.

#### Table 8. Example Control Parameter Register

|            |      |     |     |     |     |     | otor rtog |     |     |     |     |

|------------|------|-----|-----|-----|-----|-----|-----------|-----|-----|-----|-----|

| VALUE      | 0    | 0   | 0   | 1   | 1   | 0   | 0         | 1   | 1   | 0   | 0   |

| BIT        | MS10 | MS9 | MS8 | MS7 | MS6 | MS5 | MS4       | MS3 | MS2 | MS1 | MS0 |

| CLK CYCLES | 11   | 10  | 9   | 8   | 7   | 6   | 5         | 4   | 3   | 2   | 1   |

The MALx bit shows the status of the previous Manchester decoder calibration cycle. If it is high, the decoder calibration has failed on the previous calibration cycle. The MAFx bit shows if any failures have occurred since the last read of the Status Register. Any MALx failure will cause MAFx to go high. MAFx is reset to low when the Status Register is read.

The decoding procedure is performed continuously when the AMC1210 is configured for Modulator Mode 2. Note that the CLK frequency must be at least six times the Manchester data rate for the decoder to perform properly.

## Comparator Unit

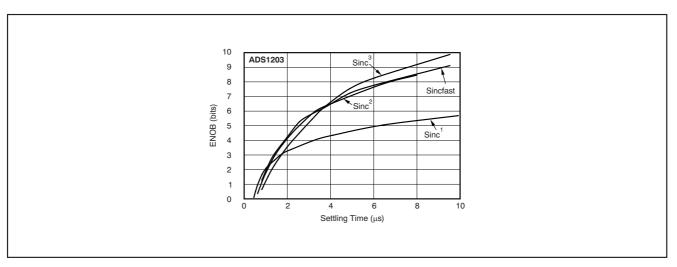

An independent comparator unit allows the user to monitor input conditions with a fast settling time without sacrificing input measurement resolution. The filter of the comparator unit is similar to the sinc filter unit, with OSR values ranging continuously between 1 and 32. Setting the OSR to 32, a maximum 15-bit output width of 32,768 can be achieved. The output of the filter is compared with two programmed threshold levels to detect over- and under-value conditions. These threshold levels are programmed in the high and low level Threshold Registers for each individual filter module. When an over- or under-value condition occurs, it signals the interrupt unit to set an interrupt signal and store the conditions in the Interrupt Register. The Interrupt Register can then be polled to see which condition caused the interrupt signal. It is not possible to read out the value of the comparator filter.

This filter, together with the comparators, is generally used to detect over-currents. It is necessary to decide on an OSR given the desired resolution/settling time combination. This programming will be discussed in more detail in the Applications Information section.

The comparator filter unit and the sinc filter unit differ in the way they handle input data. The comparator filter unit translates a low input signal to a '0' and a high input signal to a '1', whereas the sinc filter unit uses '-1' and '1'. The resulting calculations give only positive values for the output of the comparator filter. The data representation is straight binary. Table 9 and Figure 14 show the different full-scale values that the comparator filter can store using different oversampling ratios.

| OSR | Sinc <sup>1</sup> | Sinc <sup>2</sup>   | Sinc <sup>3</sup>   | Sincfast             |

|-----|-------------------|---------------------|---------------------|----------------------|

| x   | 0 to x            | 0 to x <sup>2</sup> | 0 to x <sup>3</sup> | 0 to 2x <sup>2</sup> |

| 4   | 0 to 4            | 0 to 16             | 0 to 64             | 0 to 32              |

| 8   | 0 to 8            | 0 to 64             | 0 to 512            | 0 to 128             |

| 16  | 0 to 16           | 0 to 256            | 0 to 4096           | 0 to 512             |

| 32  | 0 to 32           | 0 to 1024           | 0 to 32,768         | 0 to 2048            |

#### Table 9. Peak Data Values for Different OSR/Filter Combinations

# TEXAS INSTRUMENTS

## AMC1210

## Figure 14. Comparator Filter Resolution

The maximum resolution yields the peak values in Table 9 (15 bits binary, 32,768 decimal). Note that in order to achieve the maximum value, the delta-sigma modulator is operated at absolute maximum positive or negative full-scale, which is outside of the recommended full-scale range of 80% of most delta-sigma modulators.

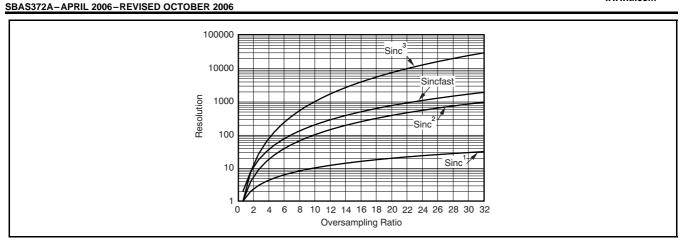

## Sinc Filter Unit

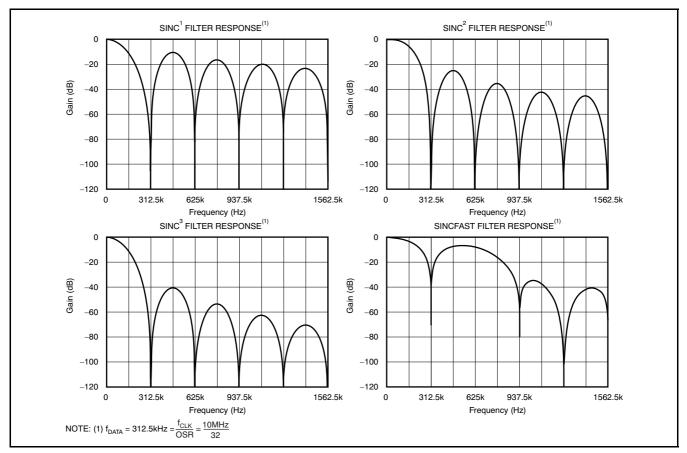

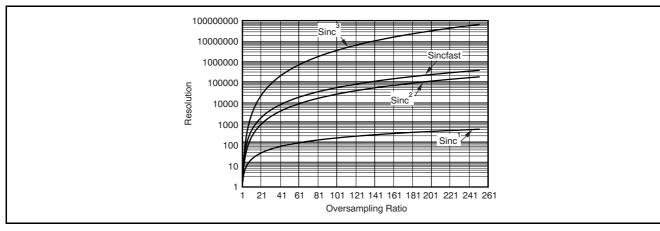

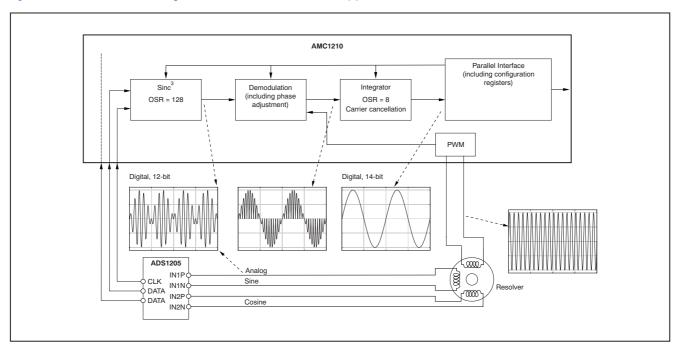

The AMC1210 utilizes a standard integration/decimation/differentiation scheme to achieve the sinc filter. It can be configured as a Sinc<sup>1</sup>, Sinc<sup>2</sup>, Sinc<sup>3</sup> or Sincfast filter with oversampling ratios (OSRs) continuously between 1 and 256. Figure 15 illustrates the frequency response of each type of filter.

Figure 15. AMC1210 Frequency Responses with Various Sinc Filters

These figures show the digital filter frequency response for one oversampling ratio (SOSR = 32) and a modulator rate of 10MHz.

The general purpose of the digital filter is to average the input modulator data. Achieving higher resolution requires additional samples for averaging, thereby increasing the total samples necessary to accurately represent an abrupt change. It also requires additional clock cycles to complete a single sample. The ratio of clock cycles to output samples is controlled by the SOSR value (the oversampling ratio for the sinc filter unit) in the Sinc Filter Parameter Register. Table 10 and Figure 16 show the maximum resolution given different filter structures and SOSR values.

| Table 10. Peak Data Values for Dif | ferent SOSR/Filter Combinations |

|------------------------------------|---------------------------------|

|------------------------------------|---------------------------------|

| SOSR | Sinc <sup>1</sup> | Sinc <sup>2</sup>  | Sinc <sup>3</sup>         | Sincfast            |

|------|-------------------|--------------------|---------------------------|---------------------|

| х    | ±Χ                | ±X <sup>2</sup>    | ±x <sup>3</sup>           | ±2x <sup>2</sup>    |

| 4    | -4 to 4           | -16 to 16          | -64 to 64                 | -32 to 32           |

| 8    | -8 to 8           | -64 to 64          | -512 to 512               | -128 to 128         |

| 16   | -16 to 16         | -256 to 256        | -4096 to 4096             | -512 to 512         |

| 32   | -32 to 32         | -1024 to 1024      | -32,768 to 32,768         | -2048 to 2048       |

| 64   | -64 to 64         | -4096 to 4096      | -262,144 to 262,144       | -8192 to 8192       |

| 128  | -128 to 128       | -16,384 to 16, 384 | -2,097,152 to 2,097,152   | -32,768 to 32,768   |

| 256  | -256 to 256       | -65,536 to 65,536  | -16,777,216 to 16,777,216 | -131,072 to 131,072 |

Figure 16. Sinc Filter Resolution

#### SBAS372A-APRIL 2006-REVISED OCTOBER 2006

The sinc filter has a bit width of 25 bits and a signed two's complementary data representation. The maximum possible resolution gives a 26-bit word (+/-16,777,216). Note that this value is only reached if the delta-sigma modulator is operated at absolute maximum positive or negative full-scale, which is beyond the recommended full-scale range of 80% of most delta-sigma modulators. This value also does not represent the resolution of the signal. The signal resolution is determined by the modulator, and increasing the filter bit width will not offer any improved noise performance beyond the modulator capabilities.

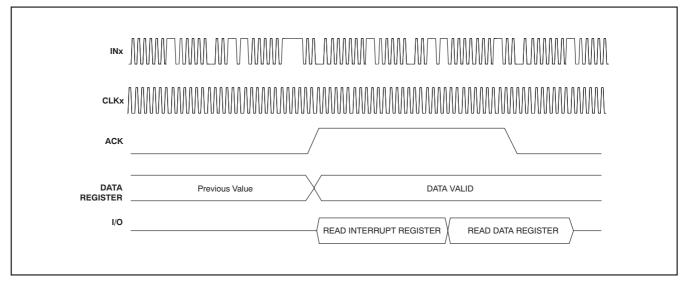

Figure 17 shows how a typical application would use the digital filter. When the filter is enabled, it is continuously processing data and generating output words. When an output word is ready to read, the processor is first triggered by a rising edge on the ACK pin. Then the Interrupt Register is read to check which filter module generated new data. Once all valid data registers have been read, the ACK pin goes low.

The data registers can be up to 32 bits.

Figure 17. Typical Data Read Sequence

#### Integrator Unit

The integrator allows digital integration (summation) of the filter output data or the direct modulator input data when the sinc filter unit is bypassed. It consists of a parameterized integrator and a data shift unit. The integrator is a simple 32-bit binary two's complement accumulator. The time of integration is determined by either the IOSR value or an external sample-and-hold signal. The bit IMOD in the Integrator Parameter Register determines which mode is used.

The integrator is enabled by setting the bit IEN in the Integrator Parameter Register to high. When IEN is low, the integrator is disabled, reset, and bypassed.

The input to the integrator is fed by the sinc filter unit. This can be adjusted to allow the input to feed directly into the integrator. See Bypassing the Sinc Filter Unit.

#### Sample-and-Hold Mode (IMOD = 1)

If Sample-and-Hold Mode is selected, the SHS bit in the Control Parameter Register determines which sample-and-hold signal is used to determine the total integration time. When a rising edge occurs on the selected sample-and-hold pin, the resulting integrator value is stored in the Data Register and the integrator is reset.

#### Oversampling Mode (IMOD = 0)

In Oversampling Mode, the integrator sums a preset number of samples from the sinc filter unit, determined by an oversampling ratio value (IOSR) in the Integrator Parameter Register. The integrator can be configured with oversampling ratios continuously between 1 and 128. The integrator is sampled at the data output rate of the sinc filter unit. Table 11 shows the different full-scale values that the integrator can store with different oversampling ratios, assuming that the sinc filter unit is set to SOSR = 256 at the full-scale output.

| IOSR | INTEGRATOR OUTPUT MAX<br>(with a Sinc <sup>3</sup> Structure) |  |  |  |  |

|------|---------------------------------------------------------------|--|--|--|--|

| х    | –(SOSR <sup>3</sup> )(x) to (SOSR <sup>3</sup> )(x)           |  |  |  |  |

| 4    | -67,108,864 to 67,108,856                                     |  |  |  |  |

| 8    | -134,217,728 to 134,217,712                                   |  |  |  |  |

| 16   | -268,435,456 to 268,435,424                                   |  |  |  |  |

| 32   | -536,870,912 to 536,870,848                                   |  |  |  |  |

| 64   | -1,073,741,824 to 1,073,741,696                               |  |  |  |  |

| 128  | -2,147,483,648 to 2,147,483,648                               |  |  |  |  |

#### Table 11. Peak Data Values for Different IOSR Values

The start of an integrator cycle in Oversampling Mode is controlled by the sinc filter unit. A new integrator cycle is started when the sinc filter is enabled. The bit MFE in the Clock Divider Register can be used to synchronize the integrator unit in all four of the filter modules. Following the rising edge of the MFE bit, the integrator will begin to accumulate data in all four modules. When the same data output rate is used on all sinc filters, synchronous timing is achieved.

#### Integrator Overflow

Meeting or exceeding the maximum values will trigger an integrator overflow (IOx goes high). This overflow condition is only possible in Oversampling Mode when the sinc filter is set to a Sinc3 structure and it outputs only full-scale values.

In Sample-and-Hold Mode, the integrator flag will go high if the maximum integrator value is exceeded (-2,147,483,648 or 2,147,483,648). This event will occur if the sample-and-hold signal SHx is held in the active state longer than the overflow time.

#### SBAS372A-APRIL 2006-REVISED OCTOBER 2006

Equation 1 calculates the time it takes for the integrator to overflow:

$t_{\text{overflow}} = \frac{(\text{INT}_{\text{max}} \cdot \text{SOSR})}{\left(\text{FILT}_{\text{out}} \cdot f_{\text{input}}\right)}$

## where:

- $INT_{MAX}$  = the maximum integrator value (-2,147,483,648 if  $FILT_{OUT} < 0, 2,147,483,648$  otherwise)

- FILT<sub>OUT</sub> = Average Sinc filter output value (from -FILT<sub>MAX</sub> to +FILT<sub>MAX</sub>; see Table 10 )

- SOSR = oversampling ratio of the Sinc filter

- f<sub>INPUT</sub> = modulator data rate

For example, if the sinc filter outputs an average code value of 100,000 at a rate of 39.06kHz ( $f_{INPUT} = 10.0MHz/SOSR = 256$ ), it will take 549.8ms for an integrator overflow flag to occur.

When integrator overflow occurs, the integrator value is reset and integration continues.

## **16-Bit Data Shifting**

If 16-bit data representation is chosen (DR is high), the shift control bits SH in the Integrator Parameter Register control which 16-bit part of a 32-bit data word is sent to the register map. The shift control bits are the number of left shifts in the 32-bit data word to achieve the maximum 16-bit value range. For example, if the sinc filter runs with a Sinc<sup>2</sup> structure and an oversampling ratio of 256, the data values will be in the range of -16,777,216 to 16,777,216. To get a maximum 16-bit range of -32,767 to 32,767, the shift control bits should be set to 9. In this case, 9 LSBs of the 25-bit word are lost. The sign bit is not affected by the shift, which means the sign is always correct, regardless of the shift control bits.

Table 12 shows an example. The first column shows the original 32-bit word, the second column shows the SH bits value, and the last column shows which bits of the 32-bit word will be output in 16-bit mode.

| 32-BIT WORD | SH VALUE | 16-BIT<br>REPRESENTATION |

|-------------|----------|--------------------------|

| b31–b0      | 1        | b16–b1                   |

|             | 9        | b24–b9                   |

|             | 14       | b29–b14                  |

#### Table 12. 16-Bit Representation Example

#### **Bypassing the Sinc Filter Unit**

If the integrator is used without the sinc filter unit, the bit FEN has to be set high, the sinc filter structure has to be set to Sinc<sup>1</sup>, and the sinc filter OSR has to be set to '1'. In this case, the integrator will sum the direct input data from the modulator.

#### Demodulation

Obtaining the resolver position from the AM-modulated resolver input signal requires mathematical demodulation. This calculation is performed by the AMC1210 after phase calibration. Modulation is enabled by setting the DEN bit in the Integrator Parameter Register high. For more information, see the Signal Generator Unit description and the Applications Information.

## Time Measure Unit

The time measure unit provides two modes of measuring times, depending on the TM bit in the Control Parameter Register. A counter is implemented in the time measure unit that counts clock cycles from the modulator clock input or the system clock.

The maximum measured time,  $t_{MAX}$ , is calculated with the formula shown in Equation 2.  $f_{CLK}$  is either the modulator clock speed or the system clock speed.

$$t_{MAX} = \frac{65536}{f_{CLK}}$$

(2)

(1)

TEXAS STRUMENTS www.ti.com

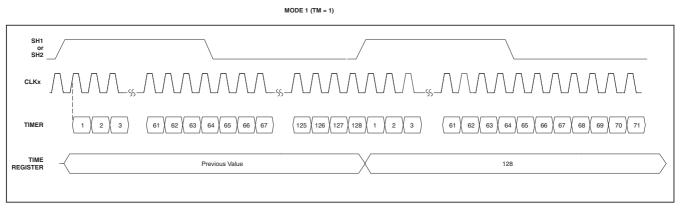

## Mode 1 (TM = 1)

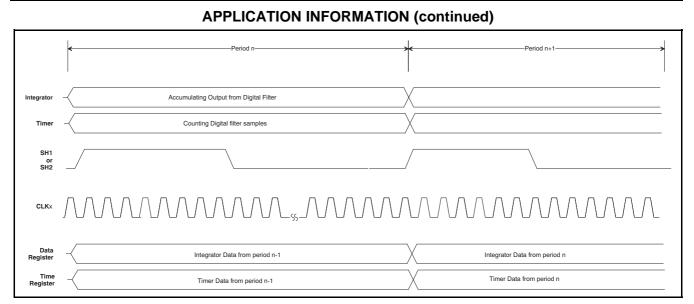

In Mode 1, the time measure unit updates the Time Register with the elapsed amount of incoming modulator clock cycles between two rising edges of the selected sample-and-hold signal (selected by the SHS bit of the Control Parameter Register). This mode can be used to measure the speed of the modulator clock or determine the number of input bits that have been clocked into the filter module. Each time a positive edge of the selected sample-and-hold is detected, the Time Register will be updated with the time counter value, and the time counter will be reset. Figure 18 shows an example of a typical functional timer sequences in Mode 1.

Figure 18. Typical Functional Timer Sequence, Mode 1 (TM = 1)

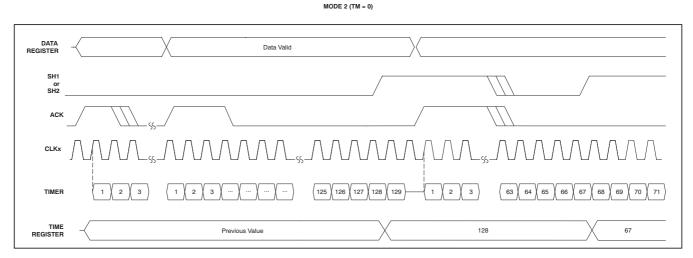

## Mode 2 (TM = 0)

In Mode 2, the time measure unit updates the Time Register with the elapsed amount of system clock cycles from the last available data to the next rising edge of the selected sample-and-hold signal. Each time data is available, that is, when the sinc filter or the integrator has new data, the timer will reset. The timer continuously counts when a rising edge of the selected sample-and-hold signal occurs. At this point, the Time Register is updated with the time counter value, and the time counter will be reset. Figure 19 shows an example of a typical functional timer sequence in Mode 2.

Since the Time Register is a 16-bit register, the maximum time measured is 65,536 clock cycles. The bit TOx in the Status Register is set to high when the time counter receives an overflow (that is, when the counter changes from 0xFFFF to 0x0000). This status bit is reset when the Status Register is read.

Figure 19. Typical Functional Timer Sequence, Mode 2 (TM = 0)

TEXAS STRUMENTS www.ti.com

SBAS372A-APRIL 2006-REVISED OCTOBER 2006

## CONTROL AND INTERRUPT MODULE

The control and interrupt module consists of a Signal Generator unit, a comprehensive interrupt unit and a register map. The register map contains all control parameters, output data and status bits for the AMC1210. A detailed description of each register is available in the Register Map section.

## Signal Generator Unit

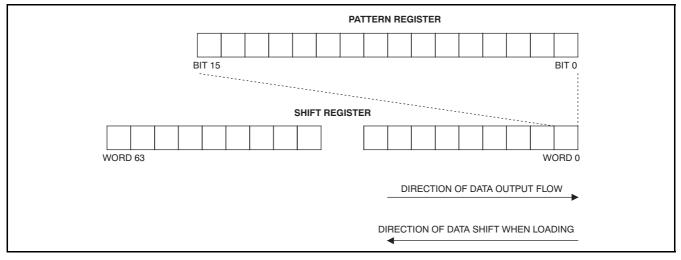

The signal generator (see Figure 20) provides a 5V Pulse Width Modulated (PWM) signal at pin PWM1 and a complementary signal at PWM2. The output of PWM1 to PWM2 is a ±5V differential signal that can be externally low-pass-filtered to generate a carrier signal with a predefined clock frequency.

The signal generator is a shift register with a length between 1 and 1024. The shift register is programmed through the Pattern Register (bits SP). On the first write command to the bits SP, the first 16 bits of the shift register are loaded. Each following write command causes the data in the shift register to shift 16 bits *upwards*, and the 16 bits from the Pattern Register are placed in the LSBs of the shift register. For example, if 874 bits of predefined pattern are to be stored in the shift register, 55 writes to the Pattern Register must be issued (with MSB first and LSB last), and the value 873 must be written into the bits PC in the Control Register.

Figure 20. AMC1210 Signal Generator Unit

The output data rate of the signal generator is programmed with the Clock Divider Register (bits SD). The output data rate can be selected to be an integer division of the CLK rate. For example, if the CLK pin is operating at 40MHz with the bits SD = 4, the bit rate of the signal generator is 10MHz. The length of the pattern can be programmed with the Control Register (bits PC). A length can be chosen between 1 and 1024 bits. This signal is designed for use as the carrier frequency in resolver applications, where proper demodulation requires a completely synchronous clock to the carrier timing.

## Calibrating the Signal Generator

The Signal Generator unit also must be in phase with the total system for resolver demodulation. This condition requires a calibration to align the phase of the Signal Generator output to the sinc filter output. The phase calibration begins when the bit PCAL in the Clock Divider Register is set high. The AMC1210 performs the calibration by monitoring the polarity of both the output of the signal generator and the sinc filter. Once the polarities are defined, a demodulation signal is generated with the corresponding phase shift.

The bit PCAL controls demodulation. Initially, it is set high. The AMC1210 then outputs a low on bit PCAL when the modulation is performed correctly. The microcontroller can monitor the calibration by reading PCAL. The first calibration attempt will try to calibrate for one period of the Signal Generator. If PCAL stays high after that period, then calibration has failed. In order to restart calibration, a low must be written to PCAL in order to restat the PCAL state. Writing a subsequent high starts the calibration over.

## CONTROL AND INTERRUPT MODULE (continued)

### Driving a Signal with the Signal Generator

The resolver can be driven directly from the AMC1210. If the bit HBE is set to high, the pins PWM1 and PWM2 are capable of driving 100mA directly into the resolver coils. If bit HBE = 0, the drive capability is lowered.

The pattern generator is enabled by the bit SGE in the Clock Divider Register.

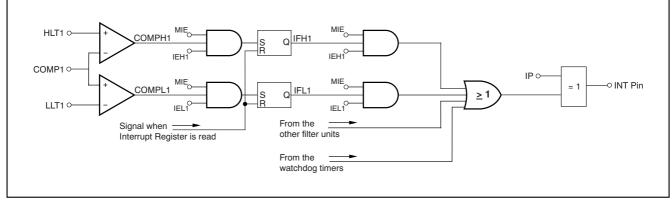

## Interrupt Unit

Figure 21 shows the structure of the interrupt unit.

Figure 21. AMC1210 Interrupt Unit

Each comparator output is one interrupt source (COMPHx or COMPLx) creating eight total comparator outputs in the AMC1210. Each of these eight interrupt sources is stored in a flag register (IFHx or IFLx), if the master interrupt enable (MIE) and the appropriate interrupt enable (IEHx or IELx) are set to high. This flag register will be set to high if an interrupt is issued. This flag will be reset if the Interrupt Register is read and the interrupt source is still active when the Interrupt Register is read, the appropriate flag will remain set.

If the modulator clock is failing (when the modulator clock is slower than 1/64th of the system clock CLK), a watchdog timer will set a flag MFx, if the appropriate modulator flag interrupt enable bit (MFIEx) and the master interrupt enable (MIE) is set. If the modulator clock is still failing when the Interrupt Register is read, the appropriate flag remains set. The flag clears if the fail condition is no longer true, and the Interrupt Register is read.

Any of the 12 interrupt bits will activate the interrupt pin INT, if enabled. The polarity of the INT pin can be chosen with the Interrupt polarity control bit (IP) in the Control Register.

## Acknowledge

The acknowledge pin ACK indicates that new data is available from one of the filter modules. When the acknowledge pin goes high, new data is available in one or more of the Data Registers. By reading the Interrupt Register, the filter module with new data can be determined. When one Data Register is read, the appropriate acknowledge flag in the Interrupt Register will be reset; when all flags are reset, the acknowledge pin is reset to low. The acknowledge pin can be inverted if the acknowledge polarity control bit (AP) in the Control Register is set high. The acknowledge flags cannot be set if both the sinc filter and the integrator are disabled. Each acknowledge flag can be disabled if the Acknowledge Enable control bit (AE) in the appropriate Sinc Filter Parameter Register is set to low. The acknowledge flag is not set when the oversampling rates of the sinc filter and the integrator are both set to '1'.

#### SBAS372A-APRIL 2006-REVISED OCTOBER 2006

| ADDR                 | )    | RESET VALUE                      | NAME                                               |

|----------------------|------|----------------------------------|----------------------------------------------------|

|                      |      |                                  |                                                    |

|                      |      | 0x0000                           | Interrupt Register                                 |

| 0x0                  |      | 0x0000                           | Control Parameter Register for Filter Module 1     |

| 0x0                  | 2    | 0x0000                           | Sinc Filter Parameter Register for Filter Module 1 |

| 0x0                  | 3    | 0x0000                           | Integrator Parameter Register for Filter Module 1  |

| Filter Module 1 0x04 | 1    | 0x7FFF                           | High-level Threshold Register for Filter Module 1  |

| 0x0                  | 5    | 0x0000                           | Low-level Threshold Register for Filter Module 1   |

| 0x0                  | 6    | 0x0000                           | Comparator Parameter Register for Filter Module 1  |

| 0x0                  | 7    | 0x0000                           | Control Parameter Register for Filter Module 2     |

| 0x0                  | 3    | 0x0000                           | Sinc Filter Parameter Register for Filter Module 2 |

| 0x0                  | )    | 0x0000                           | Integrator Parameter Register for Filter Module 2  |

| Filter Module 2 0x0  | 4    | 0x7FFF                           | High-level Threshold Register for Filter Module 2  |

| 0x0                  | 3    | 0x0000                           | Low-level Threshold Register for Filter Module 2   |

| 0x00                 | 2    | 0x0000                           | Comparator Parameter Register for Filter Module 2  |

| 0x0l                 | )    | 0x0000                           | Control Parameter Register for Filter Module 3     |

| 0x0                  | E    | 0x0000                           | Sinc Filter Parameter Register for Filter Module 3 |

| 0x0                  | -    | 0x0000                           | Integrator Parameter Register for Filter Module 3  |

| Filter Module 3 0x10 | )    | 0x7FFF                           | High-level Threshold Register for Filter Module 3  |

| 0x1                  | 1    | 0x0000                           | Low-level Threshold Register for Filter Module 3   |

| 0x1                  | 2    | 0x0000                           | Comparator Parameter Register for Filter Module 3  |

| 0x1                  | 3    | 0x0000                           | Control Parameter Register for Filter Module 4     |

| 0x1                  | 1    | 0x0000                           | Sinc Filter Parameter Register for Filter Module 4 |

| 0x1                  | 5    | 0x0000                           | Integrator Parameter Register for Filter Module 4  |

| Filter Module 4 0x1  | 6    | 0x7FFF                           | High-level Threshold Register for Filter Module 4  |

| 0x1                  | 7    | 0x0000                           | Low-level Threshold Register for Filter Module 4   |

| 0x1                  | 3    | 0x0000                           | Comparator Parameter Register for Filter Module 4  |

| 0x1                  | 9    | 0x0000                           | Control Register                                   |

| 0x1/                 | 4    | 0x0000                           | Pattern Register                                   |

| 0x1                  | 3    | 0x0000                           | Clock Divider Register                             |

| 0x10                 | )    | 0x0000                           | Status Register                                    |

| 0x1l                 | )    | 0x0000/0x00000000(1)             | Data Register for Filter Module 1 <sup>(1)</sup>   |

| 0x1                  | E    | 0x0000                           | Time Register for Filter Module 1                  |

| 0x1                  | -    | 0x0000/0x00000000 <sup>(1)</sup> | Data Register for Filter Module 2 <sup>(1)</sup>   |

| Ox2                  | )    | 0x0000                           | Time Register for Filter Module 2                  |

| Data/Time Output 0x2 |      | 0x0000/0x00000000(1)             | Data Register for Filter Module 3 <sup>(1)</sup>   |

| 0x2                  | 2    | 0x0000                           | Time Register for Filter Module 3                  |

| 0x2                  | 3    | 0x0000/0x00000000 <sup>(1)</sup> | Data Register for Filter Module 4 <sup>(1)</sup>   |

| 0x2                  | 1    | 0x0000                           | Time Register for Filter Module 4                  |

| 0x25 to              | 0x7F | 0x0000                           | Not used. Read will return 0x0000                  |

## **REGISTER MAP**

(1) The Data Registers can also be represented as 32-bit.

All control parameters are stored in the register map. Additionally, the status of the AMC1210 is read out through the register map. The mnemonic in the succeeding register description is given in Example 1.

SBAS372A-APRIL 2006-REVISED OCTOBER 2006

### **Example 1: Register Description Mnemonic**

| Bit 8 | Bit 9 | Bit 10 | The bit position in the register.                                                                                                 |

|-------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| CS1   | _     | SHS    | The name of the register<br>bit. A '-' means <i>Not Used</i><br>and therefore a write to<br>such a bit position will get<br>lost. |

| '1'   | '0'   | '0'    | The digit is the reset value.                                                                                                     |

| W     | R     | RW     | Indicates if the bit position<br>is a read-only (R), readable<br>and writable (RW) or<br>write-only (W).                          |

## **REGISTER DESCRIPTIONS**

This section describes the functionality of each register and its corresponding bits.

## Interrupt Register (address 0x00)

The Interrupt Register contains the 12 interrupt flags together with the acknowledge flags. If an interrupt occurs (that is, when the output of the comparator filter is above the high level threshold or below the low level threshold, or when one of the modulators is not functional), the appropriate interrupt flag is set (if enabled). An interrupt flag is reset when the Interrupt Register is read and the corresponding interrupt source is no longer active. The acknowledge bits are reset when the corresponding data register is read. Table 13 describes the Interrupt Register.

| Table ' | 13. | Interrupt | Register |

|---------|-----|-----------|----------|

|---------|-----|-----------|----------|

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| AF4    | AF3    | AF2    | AF1    | MF4    | MF3    | MF2   | MF1   | IFL4  | IFH4  | IFL3  | IFH3  | IFL2  | IFH2  | IFL1  | IFH1  |

|        |        |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

| '0'    | '0'    | '0'    | '0'    | '0'    | '0'    | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   |

| BIT POSITION | BIT | DESCRIPTION                                                                                                                  |  |  |  |  |  |  |  |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 15           | AF4 | Acknowledge flag for Filter 4.<br>0: No new data available for Filter 4<br>1: New data available for Filter 4                |  |  |  |  |  |  |  |

| 14           | AF3 | Acknowledge flag for Filter 3.<br>0: No new data available for Filter 3<br>1: New data available for Filter 3                |  |  |  |  |  |  |  |

| 13           | AF2 | Acknowledge flag for Filter 2.<br>0: No new data available for Filter 2<br>1: New data available for Filter 2                |  |  |  |  |  |  |  |

| 12           | AF1 | Acknowledge flag for Filter 1.<br>0: No new data available for Filter 1<br>1: New data available for Filter 1                |  |  |  |  |  |  |  |

| 11           | MF4 | Modulator failure flag for Filter 4.<br>0: Modulator is operating normally for Filter 4<br>1: Modulator failure for Filter 4 |  |  |  |  |  |  |  |

| 10           | MF3 | Modulator failure flag for Filter 3.<br>0: Modulator is operating normally for Filter 3<br>1: Modulator failure for Filter 3 |  |  |  |  |  |  |  |