## 10-Bit Integrated, Multiformat, HDTV Video Decoder, **RGB Graphics Digitizer**, and 2:1 Multiplexed **HDMI/DVI** Interface

AD9388A

### **FEATURES**

#### **Mutliformat decoder**

Three 10-bit analog-to-digital converters (ADCs)

ADC sampling rates up to 170 MHz

Mux with 12 analog input channels

525i-/625i-component SD support

525p-/625p-component progressive scan support

720p-/1080i-/1080p-component HDTV support

Digitizes RGB graphics up to 1600 × 1200 at 60 Hz (UXGA)

VBI data slicer (including teletext)

**Analog-to-HDMI fast switching**

**Dual High-Definition Multimedia Interface (HDMI) Rx**

2:1 multiplexed HDMI receiver

**HDMI 1.3, DVI 1.0**

225 MHz HDMI receiver

Repeater support

High-bandwidth digital content protection (HDCP 1.3)

36-bit deep color support

S/PDIF (IEC60958-compatible) digital audio output

Multichannel I2S audio output (up to 8 channels)

Adaptive equalizer for cable lengths up to 30 meters

Internal EDID RAM

#### General

Highly flexible output interface

STDI function support standard identification

2 any-to-any 3 × 3 color-space conversion matrices

Programmable interrupt request output pins WWW.DZSC.COM

#### **APPLICATIONS**

Advanced TVs

**PDP HDTVs**

LCD TVs (HDTV ready)

LCD/DLP® rear projection HDTVs

**CRT HDTVs**

**LCoS® HDTVs**

Audio/video receivers (AVRs)

LCD/DLP front projectors

**HDTV STBs with PVR**

DVD recorders with progressive scan input support

#### **GENERAL DESCRIPTION**

The AD9388A is a high quality, single-chip graphics digitizer with an integrated 2:1 multiplexed HDMI™ receiver.

The AD9388A contains one main component processor (CP) that processes YPrPb and RGB component formats, including RGB graphics. The CP also processes the video signals from the HDMI receiver. The AD9388A can keep the HDCP link between an HDMI source and the selected HDMI port active in analog mode operation. This allows for fast switching between the analog and HDMI modes.

The AD9388A supports the decoding of a component RGB or YPrPb video signal into a digital YCrCb or RGB pixel output stream. The support for component video includes 525i, 625i, 525p, 625p, 720p, 1080i, 1080p, and 1250i standards, as well as many other HD and SMPTE standards.

Graphic digitization is also supported by the AD9388A. The AD9388A is capable of digitizing RGB graphics signals from VGA to UXGA rates and converting them into a digital RGB or YCrCb pixel output stream.

The AD9388A incorporates a dual input, HDMI 1.3-compatible receiver that supports HDTV formats up to 1080p and display resolutions up to UXGA ( $1600 \times 1200$  at 60 Hz). The reception of encrypted video is possible with the inclusion of HDCP. In addition, the inclusion of adaptive equalization ensures robust operation of the interface with cable lengths up to 30 meters. The HDMI receiver has an advanced audio functionality, such as a mute controller that prevents audible extraneous noise in the audio output.

Derivative parts of the AD9388A are available; AD9388ABSTZ-A5 is composed of one analog and one digital input. To facilitate professional applications, where HDCP processing and decryption are not required, the AD9388ABSTZ-5P derivative is available. This allows users who are not HDCP adopters to purchase the AD9388A. See the Ordering Guide for details on these derivative parts.

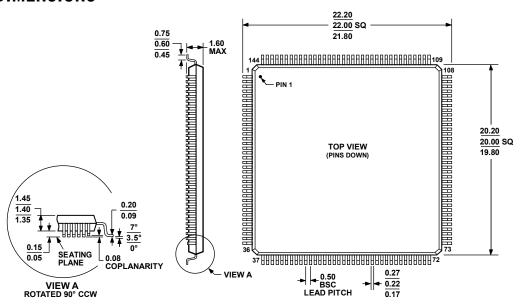

Fabricated in an advanced CMOS process, the AD9388A is available in a space saving, 144-lead, surface-mount, RoHScompliant, plastic LQFP and is specified over the -40°C to +85°C temperature range.

# **TABLE OF CONTENTS**

| Features                                                  |

|-----------------------------------------------------------|

| Applications                                              |

| General Description                                       |

| Revision History                                          |

| Functional Block Diagram                                  |

| Specifications                                            |

| Electrical Characteristics                                |

| Analog and HDMI Specifications 6                          |

| Data and I <sup>2</sup> C Timing Characteristics          |

| Absolute Maximum Ratings                                  |

| Thermal Resistance                                        |

| Package Thermal Performance9                              |

| ESD Caution9                                              |

| Pin Configurations and Function Descriptions10            |

| Functional Overview                                       |

| Analog Front End16                                        |

| HDMI Receiver                                             |

| REVISION HISTORY                                          |

| 7/08—Rev. SpA to Rev. B                                   |

| 5/08—Rev. Sp0 to Rev. SpA  Changes to General Description |

| Changes to Component Processor (CP) Section               |

| 10/07—Revsion Sp0: Initial Version                        |

| Component Processor Pixel Data Output Modes 16 |

|------------------------------------------------|

| Component Video Processing                     |

| RGB Graphics Processing                        |

| General Features                               |

| Theory of Operation                            |

| Analog Front End17                             |

| HDMI Receiver                                  |

| Component Processor (CP)                       |

| VBI Data Processor                             |

| Pixel Output Formatting                        |

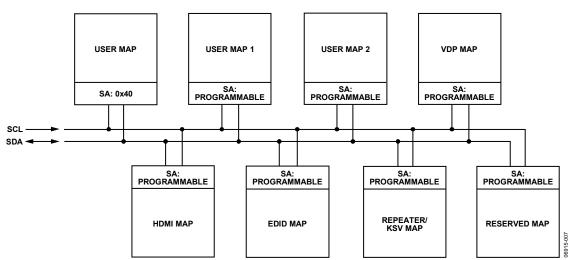

| Register Map Architecture                      |

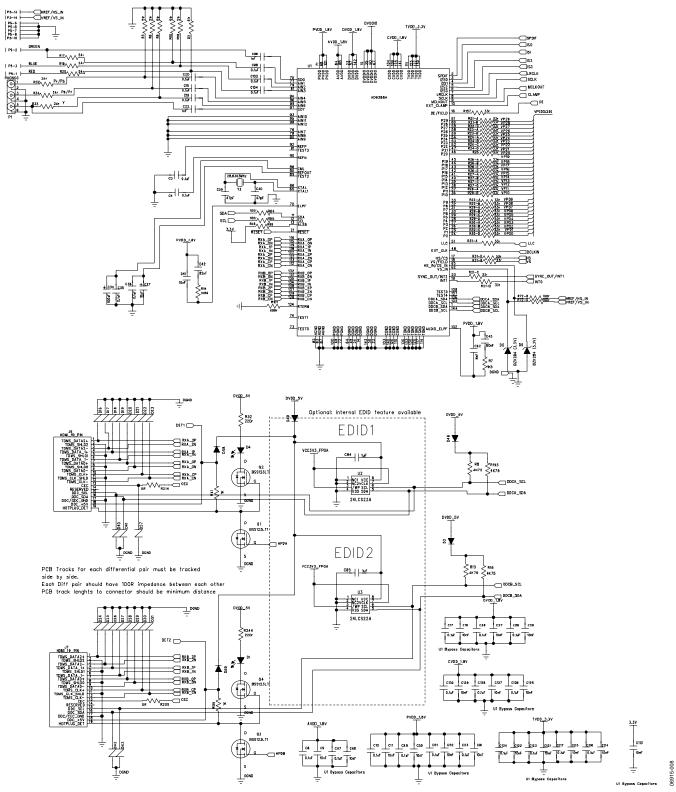

| Typical Connection Diagram22                   |

| Recommended External Loop Filter Components 23 |

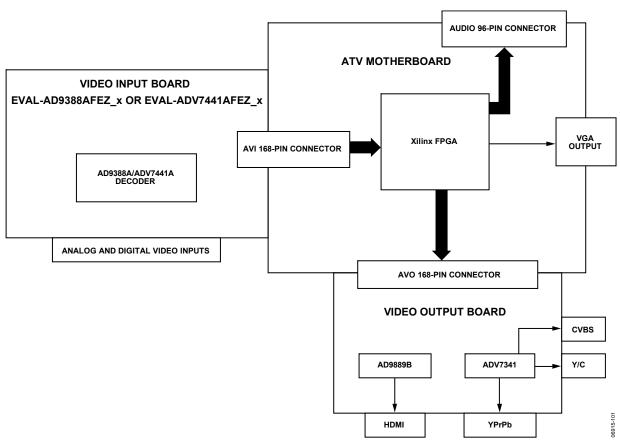

| AD9388A/ADV7441A Evaluation Platform24         |

| Outline Dimensions                             |

| Ordering Guide                                 |

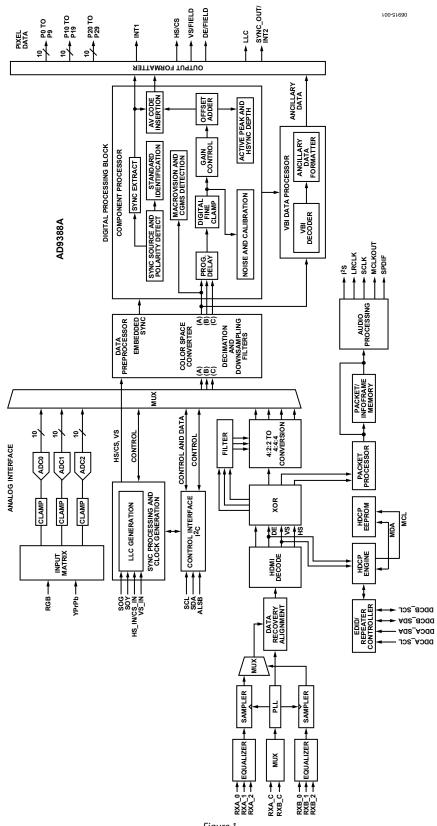

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS**

AVDD = 1.71 V to 1.89 V, DVDD = 1.62 V to 1.98 V, DVDDIO = 2.97 V to 3.63 V, PVDD = 1.71 V to 1.89 V, TVDD = 3.135 V to 3.465 V, CVDD = 1.71 V to 1.89 V. Operating temperature range is  $-40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>          | Symbol              | Test Conditions                               | Min   | Тур        | Max      | Unit |

|---------------------------------|---------------------|-----------------------------------------------|-------|------------|----------|------|

| STATIC PERFORMANCE <sup>2</sup> |                     |                                               |       |            |          |      |

| Resolution (Each ADC)           | N                   |                                               |       |            | 10       | Bits |

| Integral Nonlinearity           | INL                 | BSL at 27 MHz (@ a 10-bit level)              |       | -0.5/+2    | -4/+6    | LSB  |

|                                 |                     | BSL at 54 MHz (@ a 10-bit level)              |       | -0.5/+2    |          | LSB  |

|                                 |                     | BSL at 74 MHz (@ a 10-bit level)              |       | -0.5/+1.5  |          | LSB  |

|                                 |                     | BSL at 110 MHz (@ a 10-bit level)             |       | -0.7/+2    |          | LSB  |

|                                 |                     | BSL at 170 MHz (@ an 8-bit level)             |       | -0.25/+0.5 |          | LSB  |

| Differential Nonlinearity       | DNL                 | At 27 MHz (@ a 10-bit level)                  |       | -0.5/+0.5  | -0.95/+2 | LSB  |

|                                 |                     | At 54 MHz (@ a 10-bit level)                  |       | ±0.5       |          | LSB  |

|                                 |                     | At 74 MHz (@ a 10-bit level)                  |       | ±0.5       |          | LSB  |

|                                 |                     | At 110 MHz (@ a 10-bit level)                 |       | ±0.5       |          | LSB  |

|                                 |                     | At 170 MHz (@ an 8-bit level)                 |       | -0.25/+0.2 |          | LSB  |

| DIGITAL INPUTS                  |                     |                                               |       |            |          |      |

| Input High Voltage <sup>3</sup> | V <sub>IH</sub>     |                                               | 2     |            |          | V    |

|                                 |                     | HS_IN, VS_IN low trigger mode                 | 0.7   |            |          | V    |

| Input Low Voltage <sup>3</sup>  | V <sub>IL</sub>     |                                               |       |            | 0.8      | V    |

|                                 |                     | HS_IN, VS_IN low trigger mode                 |       |            | 0.3      | V    |

| Input Current                   | I <sub>IN</sub>     | Pin 21 (RESET)                                | -60   |            | +60      | μΑ   |

| •                               |                     | All input pins other than Pin 21              | -10   |            | +10      | μΑ   |

| Input Capacitance <sup>4</sup>  | C <sub>IN</sub>     |                                               |       |            | 10       | pF   |

| DIGITAL OUTPUTS                 |                     |                                               |       |            |          |      |

| Output High Voltage⁵            | V <sub>OH</sub>     | I <sub>SOURCE</sub> = 0.4 mA                  | 2.4   |            |          | V    |

| Output Low Voltage⁵             | Vol                 | $I_{SINK} = 3.2 \text{ mA}$                   |       |            | 0.4      | V    |

| High Impedance Leakage Current  | I <sub>LEAK</sub>   |                                               |       |            | 10       | μΑ   |

| Output Capacitance <sup>4</sup> | Соит                |                                               |       |            | 20       | pF   |

| POWER REQUIREMENTS⁴             |                     |                                               |       |            |          |      |

| Digital Core Power Supply       | DVDD                |                                               | 1.62  | 1.8        | 1.98     | V    |

| Digital I/O Power Supply        | DVDDIO              |                                               | 2.97  | 3.3        | 3.63     | V    |

| PLL Power Supply                | PVDD                |                                               | 1.71  | 1.8        | 1.89     | V    |

| Analog Power Supply             | AVDD                |                                               | 1.71  | 1.8        | 1.89     | V    |

| Terminator Power Supply         | TVDD                |                                               | 3.135 | 3.3        | 3.465    | V    |

| Comparator Power Supply         | CVDD                |                                               | 1.71  | 1.8        | 1.89     | V    |

| Digital Core Supply Current     | I <sub>DVDD</sub>   | Graphics RGB sampling @ 108 MHz <sup>6</sup>  |       | 141        | 252      | mA   |

|                                 |                     | YPrPb 1080p sampling @ 148.5 MHz <sup>6</sup> |       | 203        | 263      | mA   |

|                                 |                     | HDMI RGB sampling @ 165 MHz <sup>7, 8</sup>   |       | 242        | 329      | mA   |

|                                 |                     | HDMI RGB sampling @ 225 MHz <sup>7,8</sup>    |       | 242        | 326      | mA   |

| Digital I/O Supply Current      | I <sub>DVDDIO</sub> | Graphics RGB sampling @ 108 MHz <sup>6</sup>  |       | 17         | 37       | mA   |

|                                 |                     | YPrPb 1080p sampling @ 148.5 MHz <sup>6</sup> |       | 42         | 62       | mA   |

|                                 |                     | HDMI RGB sampling @ 165 MHz <sup>7,8</sup>    |       | 17         | 34       | mA   |

|                                 |                     | HDMI RGB sampling @ 225 MHz <sup>7,8</sup>    |       | 20         | 34       | mA   |

| HDMI Comparators                | I <sub>CVDD</sub>   | Graphics RGB sampling @ 108 MHz <sup>6</sup>  |       | 56         | 78       | mA   |

| Parameter <sup>1</sup>                   | Symbol             | Test Conditions                                | Min | Тур  | Max | Unit |

|------------------------------------------|--------------------|------------------------------------------------|-----|------|-----|------|

| TMDS PLL and Equalizer<br>Supply Current |                    | YPrPb 1080p sampling @ 148.5 MHz <sup>6</sup>  |     | 56   | 79  | mA   |

|                                          |                    | HDMI RGB sampling @ 165 MHz <sup>7,8</sup>     |     | 86   | 105 | mA   |

|                                          |                    | HDMI RGB sampling @ 225 MHz <sup>7,8</sup>     |     | 95   | 118 | mA   |

| Analog Supply Current                    | l <sub>AVDD</sub>  | Graphics RGB sampling @ 108 MHz <sup>6</sup>   |     | 174  | 278 | mA   |

|                                          |                    | YPrPb 1080p sampling @ 148.5 MHz <sup>6</sup>  |     | 180  | 284 | mA   |

|                                          |                    | HDMI RGB sampling @ 165 MHz <sup>7,8</sup>     |     | 0    | 2   | mA   |

|                                          |                    | HDMI RGB sampling @ 225 MHz <sup>7,8</sup>     |     | 0    | 2   | mA   |

| Terminator Supply Current                | I <sub>TVDD</sub>  | Graphics RGB sampling @ 108 MHz <sup>6</sup>   |     | 12   | 18  | mA   |

|                                          |                    | YPrPb 1080p sampling @ 148.5 MHz <sup>6</sup>  |     | 12   | 18  | mA   |

|                                          |                    | HDMI RGB sampling @ 165 MHz <sup>7, 8, 9</sup> |     | 42   | 47  | mA   |

|                                          |                    | HDMI RGB sampling @ 225 MHz <sup>7, 8, 9</sup> |     | 63   | 69  | mA   |

| Audio and Video Supply Current           | I <sub>PVDD</sub>  | Graphics RGB sampling @ 108 MHz <sup>6</sup>   |     | 14   | 21  | mA   |

|                                          |                    | YPrPb 1080p sampling @ 148.5 MHz <sup>6</sup>  |     | 19   | 24  | mA   |

|                                          |                    | HDMI RGB sampling @ 165 MHz <sup>7,8</sup>     |     | 10   | 19  | mA   |

|                                          |                    | HDMI RGB sampling @ 225 MHz <sup>7,8</sup>     |     | 15   | 20  | mA   |

| Power-Down Current                       | I <sub>PWRDN</sub> |                                                |     | 11.6 |     | mA   |

| Power-Up Time                            | t <sub>PWRUP</sub> |                                                |     | 25   |     | ms   |

$<sup>^1</sup>$  The minimum/maximum specifications are guaranteed over the  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  temperature range (T<sub>MIN</sub> to T<sub>MAX</sub>).  $^2$  All ADC linearity tests performed at input range of full scale - 12.5% and at zero scale + 12.5%.  $^3$  Pin 1, Pin 105, Pin 106, and Pin 144 are 5 V tolerant.

<sup>&</sup>lt;sup>4</sup> Guaranteed by characterization.

Submittee by Characterization.

S  $V_{OH}$  and  $V_{OL}$  levels obtained using default drive strength value (0x15) in User Map Register 0xF4.

Current measurements for analog inputs were made with HDMI/analog simultaneous mode disabled (User Map Register 0xBA Bit 7 programmed with Value 0) and no HDMI sources connected to the part.

<sup>&</sup>lt;sup>7</sup> Current measurements for HDMI inputs were made with a source connected to the active HDMI port and no source connected to the inactive HDMI port.

$<sup>^8</sup>$  Audio stream is uncompressed stereo audio sampling frequency of  $f_{\rm s}=48$  kHz and MCLKOUT = 256  $f_{\rm s}$ .  $^9$  The terminator supply current may vary with the HDMI source in use.

## **ANALOG AND HDMI SPECIFICATIONS**

AVDD = 1.71 V to 1.89 V, DVDD = 1.62 V to 1.98 V, DVDDIO = 2.97 V to 3.63 V, PVDD = 1.71 V to 1.89 V, TVDD = 3.135 V to 3.465 V, CVDD = 1.71 V to 1.89 V. Operating temperature range is -40°C to +85°C, unless otherwise noted.

Table 2.

| Parameter <sup>1, 2</sup>                                | Test Conditions                | Min | Тур         | Max                                        | Unit               |

|----------------------------------------------------------|--------------------------------|-----|-------------|--------------------------------------------|--------------------|

| ANALOG                                                   |                                |     |             |                                            |                    |

| Clamp Circuitry                                          |                                |     |             |                                            |                    |

| External Clamp Capacitor                                 |                                |     | 0.1         |                                            | μF                 |

| Input Impedance (Except Pin 74)                          | Clamps switched off            |     | 10          |                                            | ΜΩ                 |

| Input Impedance of Pin 74                                |                                |     | 20          |                                            | kΩ                 |

| CML                                                      |                                |     | 0.88        |                                            | V                  |

| ADC Full-Scale Level                                     |                                |     | CML + 0.5   |                                            | V                  |

| ADC Zero-Scale Level                                     |                                |     | CML - 0.5   |                                            | V                  |

| ADC Dynamic Range                                        |                                |     | 1           |                                            | V                  |

| Clamp Level (When Locked)                                | Component input (Y signal)     |     | CML - 0.120 |                                            | V                  |

|                                                          | Component input (Pr signal)    |     | CML         |                                            | V                  |

|                                                          | Component input (Pb signal)    |     | CML         |                                            | V                  |

|                                                          | PC RGB input (R, G, B signals) |     | CML - 0.120 |                                            | V                  |

| HDMI SPECIFICATIONS <sup>3</sup>                         |                                |     |             |                                            |                    |

| Intrapair (Positive-to-Negative) Differential Input Skew |                                |     |             | 0.4                                        | t <sub>bit</sub> 4 |

| Channel-to-Channel Differential Input Skew               |                                |     |             | $0.2 t_{\text{pixel}}^5 + 1.78 \text{ ns}$ |                    |

$<sup>^1</sup>$  The minimum/maximum specifications are guaranteed over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  temperature range.  $^2$  Guaranteed by characterization.

<sup>&</sup>lt;sup>3</sup> Guaranteed by design. <sup>4</sup> t<sub>bit</sub> is 1/10 the pixel period of the TMDS clock. <sup>5</sup> t<sub>pixel</sub> is the period of the TMDS clock.

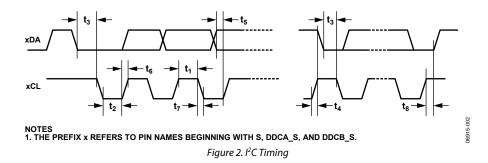

## DATA AND I<sup>2</sup>C TIMING CHARACTERISTICS

AVDD = 1.71 V to 1.89 V, DVDD = 1.62 V to 1.98 V, DVDDIO = 2.97 V to 3.63 V, PVDD = 1.71 V to 1.89 V, TVDD = 3.135 V to 3.465 V, CVDD = 1.71 V to 1.89 V; operating temperature range is  $-40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted.

Table 3.

| Parameter <sup>1, 2</sup>                         | Symbol                           | Test Conditions                            | Min    | Тур     | Max    | Unit   |

|---------------------------------------------------|----------------------------------|--------------------------------------------|--------|---------|--------|--------|

| SYSTEM CLOCK AND CRYSTAL                          |                                  |                                            |        |         |        |        |

| Crystal Nominal Frequency                         |                                  |                                            |        | 28.6363 |        | MHz    |

| Crystal Frequency Stability                       |                                  |                                            |        |         | ±50    | ppm    |

| Horizontal Sync Input Frequency                   |                                  |                                            | 14.8   |         | 110    | kHz    |

| LLC Frequency Range                               |                                  |                                            | 12.825 |         | 170    | MHz    |

| I <sup>2</sup> C PORTS (FAST MODE) <sup>3</sup>   |                                  |                                            |        |         |        |        |

| xCL Frequency⁴                                    |                                  |                                            |        |         | 400    | kHz    |

| xCL Minimum Pulse Width High⁴                     | t <sub>1</sub>                   |                                            | 0.6    |         |        | μs     |

| xCL Minimum Pulse Width Low <sup>4</sup>          | $t_2$                            |                                            | 1.3    |         |        | μs     |

| Hold Time (Start Condition)                       | t <sub>3</sub>                   |                                            | 0.6    |         |        | μs     |

| Setup Time (Start Condition)                      | <b>t</b> 4                       |                                            | 0.6    |         |        | μs     |

| xDA Setup Time <sup>4</sup>                       | <b>t</b> <sub>5</sub>            |                                            | 100    |         |        | ns     |

| xCL and xDA Rise Times <sup>4</sup>               | t <sub>6</sub>                   |                                            |        |         | 300    | ns     |

| xCL and xDA Fall Times <sup>4</sup>               | <b>t</b> <sub>7</sub>            |                                            |        |         | 300    | ns     |

| Setup Time (Stop Condition)                       | t <sub>8</sub>                   |                                            | 0.6    |         |        | μs     |

| I <sup>2</sup> C PORTS (NORMAL MODE)              |                                  |                                            |        |         |        | ,      |

| xCL Frequency                                     |                                  |                                            |        |         | 100    | kHz    |

| xCL Minimum Pulse Width High                      | t <sub>1</sub>                   |                                            | 4      |         |        | μs     |

| xCL Minimum Pulse Width Low                       | $t_2$                            |                                            | 4.7    |         |        | μs     |

| Hold Time (Start Condition)                       | t <sub>3</sub>                   |                                            | 4      |         |        | μs     |

| Setup Time (Start Condition)                      | t <sub>4</sub>                   |                                            | 4.7    |         |        | μs     |

| xDA Setup Time                                    | <b>t</b> <sub>5</sub>            |                                            | 250    |         |        | ns     |

| xCL and xDA Rise Times                            | t <sub>6</sub>                   |                                            |        |         | 1000   | ns     |

| xCL and xDA Fall Times                            | t <sub>7</sub>                   |                                            |        |         | 300    | ns     |

| Setup Time (Stop Condition)                       | t <sub>8</sub>                   |                                            | 4      |         |        | μs     |

| RESET FEATURE                                     |                                  |                                            |        |         |        | -      |

| Reset Pulse Width                                 |                                  |                                            | 5      |         |        | ms     |

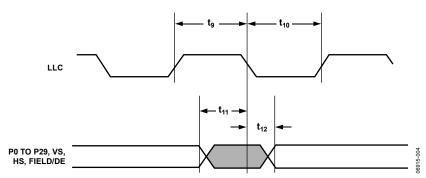

| CLOCK OUTPUTS                                     |                                  |                                            |        |         |        |        |

| LLC Mark Space Ratio                              | t <sub>9</sub> :t <sub>10</sub>  |                                            | 45:55  |         | 55:45  | % duty |

| ·                                                 |                                  |                                            |        |         |        | cycle  |

| DATA AND CONTROL OUTPUTS                          |                                  |                                            |        |         |        |        |

| Data Output Transition Time SDR (CP) <sup>5</sup> | t <sub>11</sub>                  | End of valid data to negative clock edge   |        |         | 2      | ns     |

|                                                   | t <sub>12</sub>                  | Negative clock edge to start of valid data |        |         | 0.5    | ns     |

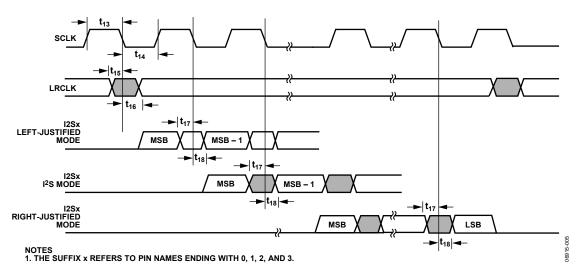

| I <sup>2</sup> S PORT (MASTER MODE)               |                                  |                                            |        |         |        |        |

| SCLK Mark Space Ratio                             | t <sub>13</sub> :t <sub>14</sub> |                                            | 45:55  |         | 55:45  | % duty |

|                                                   |                                  |                                            |        |         |        | cycle  |

| LRCLK Data Transition Time                        | t <sub>15</sub>                  | End of valid data to negative SCLK edge    |        |         | 10     | ns     |

| LRCLK Data Transition Time                        | t <sub>16</sub>                  | Negative SCLK edge to start of valid data  |        |         | 10     | ns     |

| 12Sx Data Transition Time <sup>6</sup>            | t <sub>17</sub>                  | End of valid data to negative SCLK edge    |        |         | 5      | ns     |

| 12Sx Data Transition Time <sup>6</sup>            | t <sub>18</sub>                  | Negative SCLK edge to start of valid data  |        |         | 5      | ns     |

| MCLKOUT Frequency                                 |                                  |                                            | 4.096  |         | 24.576 | MHz    |

$<sup>^1</sup>$  The minimum/maximum specifications are guaranteed over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range ( $T_{MIN}$  to  $T_{MAX}$ ).

<sup>&</sup>lt;sup>2</sup> Guaranteed by characterization.

<sup>&</sup>lt;sup>3</sup> Refers to all I<sup>2</sup>C pins (DDC and control port).

<sup>&</sup>lt;sup>4</sup> The prefix x refers to pin names beginning with S, DDCA\_S, and DDCB\_S.

<sup>5</sup> CP timing figures were obtained using the maximum drive strength value (0x3F) in User Map Register 0xF4.

<sup>&</sup>lt;sup>6</sup> The suffix x refers to pin names ending with 0, 1, 2, and 3.

## **Timing Diagrams**

Figure 3. Pixel Port and Control CP Output Timing (CP Core)

Figure 4. I<sup>2</sup>S Timing

## **ABSOLUTE MAXIMUM RATINGS**

Table 4

| Table 4.                          |                                |

|-----------------------------------|--------------------------------|

| Parameter                         | Rating                         |

| AVDD to AGND                      | 2.2 V                          |

| DVDD to DGND                      | 2.2 V                          |

| PVDD to PGND                      | 2.2 V                          |

| DVDDIO to DGND                    | 4 V                            |

| CVDD to CGND                      | 2.2 V                          |

| TVDD to TGND                      | 4 V                            |

| DVDDIO to AVDD                    | −0.3 V to +3.6 V               |

| DVDDIO to TVDD                    | −3.6 V to +3.6 V               |

| DVDDIO to DVDD                    | -2 V to +2 V                   |

| CVDD to DVDD                      | −2 V to +0.3 V                 |

| PVDD to DVDD                      | −2 V to +0.3 V                 |

| AVDD to CVDD                      | -2 V to +2 V                   |

| AVDD to PVDD                      | -2 V to +2 V                   |

| AVDD to DVDD                      | -2 V to +2 V                   |

| AVDD to TVDD                      | −3.6 V to +0.3 V               |

| TVDD to DVDD                      | −2 V to +2 V                   |

| Digital Inputs                    |                                |

| Voltage to DGND                   | DGND – 0.3 V to DVDDIO + 0.3 V |

| Digital Outputs                   |                                |

| Voltage to DGND                   | DGND – 0.3 V to DVDDIO + 0.3 V |

| Analog Inputs                     | AGND – 0.3 V to AVDD + 0.3 V   |

| Voltage to AGND  Maximum Junction | AGND = 0.3 V to AVDD + 0.3 V   |

| Temperature (T <sub>J_MAX</sub> ) | 125°C                          |

| Storage Temperature Range         | −65°C to +150°C                |

| Infrared Reflow,                  |                                |

| Soldering (20 sec)                | 260°C                          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

Table 5.

| Package Type           | $\Psi_{JT}^{1}$ | Unit |

|------------------------|-----------------|------|

| 144-Lead LQFP (ST-144) | 1.62            | °C/W |

<sup>&</sup>lt;sup>1</sup> Junction-to-package surface thermal resistance.

#### PACKAGE THERMAL PERFORMANCE

To reduce power consumption during AD9388A operation, turn off unused ADCs.

On a four-layer PCB that includes a solid ground plane, the  $\theta_{JA}$  value is 25.3°C/W. However, due to variations within the PCB metal and, therefore, variations in PCB heat conductivity, the value of  $\theta_{JA}$  may differ for various PCBs.

The most efficient measurement technique is to use the surface temperature of the package to estimate the die temperature because this is not affected by the variance associated with the  $\theta_{IA}$  value.

The maximum junction temperature ( $T_{I\_MAX}$ ) of 125°C must not be exceeded. The following equation calculates the junction temperature using the measured surface temperature of the package and applies only when no heat sink is used on DUT:

$$T_{J\_MAX} = T_S + (\Psi_{JT} \times W_{TOTAL})$$

where:

$T_S$  is the surface temperature of the package expressed in degrees Celsius.

$\Psi_{JT}$  is the junction-to-package surface thermal resistance.  $W_{TOTAL} = \{(AVDD \times IAVDD) + (DVDD \times IDVDD) + (DVDDIO \times IDVDDIO) + (PVDD \times IPVDD) + (CVDD \times ICVDD) + (TVDD \times ITVDD)\}.$

Contact an Analog Devices, Inc., representative for more details on package thermal performance at video.products@analog.com.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

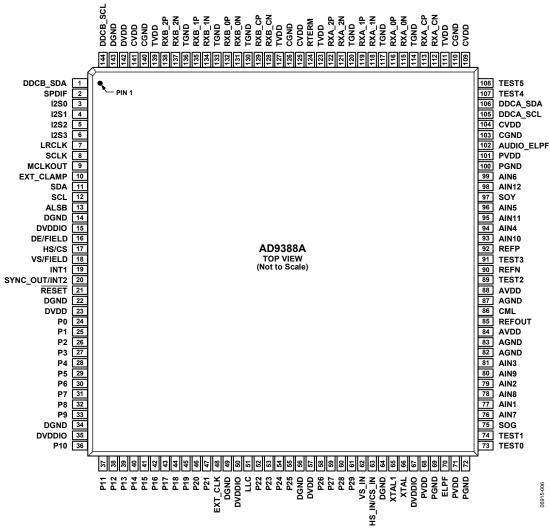

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No.                      | Mnemonic                   | Type <sup>1</sup> | Description                                                      |

|------------------------------|----------------------------|-------------------|------------------------------------------------------------------|

| 14, 22, 34, 49, 56, 64, 143  | DGND                       | G                 | Digital Ground.                                                  |

| 82, 83, 87                   | AGND                       | G                 | Analog Ground.                                                   |

| 69, 72, 100                  | PGND                       | G                 | PLL Ground.                                                      |

| 103, 110, 126, 140           | CGND                       | G                 | Comparator Ground.                                               |

| 114, 117, 120, 130, 133, 136 | TGND                       | G                 | Terminator Ground.                                               |

| 15, 35, 50, 67               | DVDDIO                     | Р                 | Digital I/O Supply Voltage (3.3 V).                              |

| 23, 57, 142                  | DVDD                       | Р                 | Digital Core Supply Voltage (1.8 V).                             |

| 84, 88                       | AVDD                       | Р                 | Analog Supply Voltage (1.8 V).                                   |

| 68, 71, 101                  | PVDD                       | Р                 | Audio and Video PLL Supply Voltage (1.8 V).                      |

| 104, 109, 125, 141           | CVDD                       | Р                 | HDMI Comparator, TMDS PLL, and Equalizer Supply Voltage (1.8 V). |

| 111, 123, 127, 139           | TVDD                       | Р                 | Terminator Supply Voltage (3.3 V).                               |

| 73, 74, 91, 108              | TEST0, TEST1, TEST3, TEST5 | 1                 | Test Pins. Do not connect.                                       |

| 89                           | TEST2                      | 0                 | Test Pin. Do not connect.                                        |

| 107                          | TEST4                      | I/O               | Test Pin. Do not connect.                                        |

| 76 to 81, 93 to 96, 98, 99   | AIN1 to AIN12              | 1                 | Analog Video Input Channel.                                      |

| Pin No.                                | Mnemonic      | Type <sup>1</sup> | Description                                                                                                                                                                                                                          |

|----------------------------------------|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24 to 33, 36 to 47, 52 to 55, 58 to 61 | P0 to P29     | 0                 | Video Pixel Output Port.                                                                                                                                                                                                             |

| 19                                     | INT1          | 0                 | Interrupt. Can be active low or active high. The set of events that triggers an interrupt is under user control.                                                                                                                     |

| 20                                     | SYNC_OUT/INT2 | 0                 | Sliced Synchronization Output Signal (SYNC_OUT).                                                                                                                                                                                     |

|                                        |               |                   | Interrupt Signal (INT2).                                                                                                                                                                                                             |

| 17                                     | HS/CS         | 0                 | Horizontal Synchronization Output Signal (HS).                                                                                                                                                                                       |

|                                        |               |                   | Composite Synchronization (CS). A single signal containing both horizontal and vertical synchronization pulses.                                                                                                                      |

| 18                                     | VS/FIELD      | 0                 | Vertical Synchronization Output Signal (VS).                                                                                                                                                                                         |

|                                        |               |                   | Field Synchronization (FIELD). Field synchronization output signal in all interlaced video modes.                                                                                                                                    |

| 16                                     | DE/FIELD      | 0                 | Data Enable Signal (DE). Indicates active pixel data.                                                                                                                                                                                |

|                                        |               |                   | Field Synchronization (FIELD). Field synchronization output signal in all interlaced video modes.                                                                                                                                    |

| 11                                     | SDA           | I/O               | I <sup>2</sup> C Port Serial Data Input/Output Pin. SDA is the data line for the control port.                                                                                                                                       |

| 12                                     | SCL           | 1                 | I <sup>2</sup> C Port Serial Clock Input. (Maximum clock rate of 400 kHz.) SCL is the clock line for the control port.                                                                                                               |

| 13                                     | ALSB          | 1                 | This pin sets the second LSB of each AD9388A register map.                                                                                                                                                                           |

| 21                                     | RESET         | I                 | System Reset Input. Active low. A minimum low reset pulse width of 5 ms is required to reset the AD9388A circuitry.                                                                                                                  |

| 51                                     | LLC           | О                 | Line-Locked Output Clock for Pixel Data. Range is 13.5 MHz to 170 MHz.                                                                                                                                                               |

| 65                                     | XTAL1         | 0                 | This pin should be connected to the 28.63636 MHz crystal or left as a no connect if an external 3.3 V 28.63636 MHz clock oscillator source is used to clock the AD9388A. In crystal mode, the crystal must be a fundamental crystal. |

| 66                                     | XTAL          | I                 | Input Pin for the 28.63636 MHz Crystal. This pin can be overdriven by an external 3.3 V 28.63636 MHz clock oscillator source to clock the AD9388A.                                                                                   |

| 70                                     | ELPF          | 0                 | The recommended external loop filter must be connected to this ELPF pin.                                                                                                                                                             |

| 102                                    | AUDIO_ELPF    | 0                 | The recommended external loop filter must be connected to this AUDIO_ELPF pin.                                                                                                                                                       |

| 85                                     | REFOUT        | 0                 | Internal Voltage Reference Output.                                                                                                                                                                                                   |

| 86                                     | CML           | 0                 | Common-Mode Level for the Internal ADCs.                                                                                                                                                                                             |

| 90                                     | REFN          | 1                 | Internal Voltage Output.                                                                                                                                                                                                             |

| 92                                     | REFP          | I                 | Internal Voltage Output.                                                                                                                                                                                                             |

| 63                                     | HS_IN/CS_IN   | 1                 | HS Input Signal. Used in analog mode for 5-wire timing mode. CS Input Signal. Used in analog mode for 4-wire timing mode. For optimal performance, a 100 $\Omega$ series resistor is recommended on the HS_IN/CS_IN pin.             |

| 62                                     | VS_IN         | I                 | VS Input Signal. This pin is used in analog mode for 5-wire timing mode. For optimal performance, a $100\Omega$ series resistor is recommended on the VS_IN pin.                                                                     |

| 75                                     | SOG           | I                 | Synchronization-on-Green Input. This pin is used in embedded synchronization mode.                                                                                                                                                   |

| 97                                     | SOY           | 1                 | Synchronization-on-Luma Input. This pin is used in embedded synchronization mode.                                                                                                                                                    |

| 112                                    | RXA_CN        | 1                 | Digital Input Clock Complement of Port A in the HDMI Interface.                                                                                                                                                                      |

| 113                                    | RXA_CP        | 1                 | Digital Input Clock True of Port A in the HDMI Interface.                                                                                                                                                                            |

| 115                                    | RXA_0N        | 1                 | Digital Input Channel 0 Complement of Port A in the HDMI Interface.                                                                                                                                                                  |

| 116                                    | RXA_0P        | I                 | Digital Input Channel 0 True of Port A in the HDMI Interface.                                                                                                                                                                        |

| 118                                    | RXA_1N        | I                 | Digital Input Channel 1 Complement of Port A in the HDMI Interface.                                                                                                                                                                  |

| 119                                    | RXA_1P        | ļ                 | Digital Input Channel 1 True of Port A in the HDMI Interface.                                                                                                                                                                        |

Pov B | Page 11 of 29

| Pin No. | Mnemonic  | Type <sup>1</sup> | Description                                                                                           |

|---------|-----------|-------------------|-------------------------------------------------------------------------------------------------------|

| 121     | RXA_2N    | I                 | Digital Input Channel 2 Complement of Port A in the HDMI Interface.                                   |

| 122     | RXA_2P    | 1                 | Digital Input Channel 2 True of Port A in the HDMI Interface.                                         |

| 128     | RXB_CN    | 1                 | Digital Input Clock Complement of Port B in the HDMI Interface.                                       |

| 129     | RXB_CP    | 1                 | Digital Input Clock True of Port B in the HDMI Interface.                                             |

| 131     | RXB_0N    | 1                 | Digital Input Channel 0 Complement of Port B in the HDMI Interface.                                   |

| 132     | RXB_OP    | 1                 | Digital Input Channel 0 True of Port B in the HDMI Interface.                                         |

| 134     | RXB_1N    | 1                 | Digital Input Channel 1 Complement of Port B in the HDMI Interface.                                   |

| 135     | RXB_1P    | 1                 | Digital Input Channel 1 True of Port B in the HDMI Interface.                                         |

| 137     | RXB_2N    | 1                 | Digital Input Channel 2 Complement of Port B in the HDMI Interface.                                   |

| 138     | RXB_2P    | 1                 | Digital Input Channel 2 True of Port B in the HDMI Interface.                                         |

| 106     | DDCA_SDA  | I/O               | HDCP Slave Serial Data Port A.                                                                        |

| 1       | DDCB_SDA  | I/O               | HDCP Slave Serial Data Port B.                                                                        |

| 105     | DDCA_SCL  | 1                 | HDCP Slave Serial Clock Port A.                                                                       |

| 144     | DDCB_SCL  | 1                 | HDCP Slave Serial Clock Port B.                                                                       |

| 2       | SPDIF     | 0                 | SPDIF Digital Audio Output.                                                                           |

| 3       | 12S0      | 0                 | I <sup>2</sup> S Audio (Channel 1 and Channel 2).                                                     |

| 4       | I2S1      | 0                 | I <sup>2</sup> S Audio (Channel 3 and Channel 4).                                                     |

| 5       | 12S2      | 0                 | I <sup>2</sup> S Audio (Channel 5 and Channel 6).                                                     |

| 6       | I2S3      | 0                 | I <sup>2</sup> S Audio (Channel 7, and Channel 8).                                                    |

| 7       | LRCLK     | 0                 | LRCLK, Data Output Clock for Left and Right Audio Channels.                                           |

| 8       | SCLK      | 0                 | Audio Serial Clock Output.                                                                            |

| 9       | MCLKOUT   | 0                 | Audio Master Clock Output.                                                                            |

| 10      | EXT_CLAMP | 1                 | External Clamp Signal. This is an optional mode of operation for the AD9388A.                         |

| 48      | EXT_CLK   | 1                 | Clock Input for External Clock and Clamp Mode. This is an optional mode of operation for the AD9388A. |

| 124     | RTERM     | 1                 | Sets Internal Termination Resistance. Connect this pin to TGND using a 500 $\Omega$ resistor.         |

$<sup>^{1}</sup>$  G = ground, P = power, I = input, and O = output.

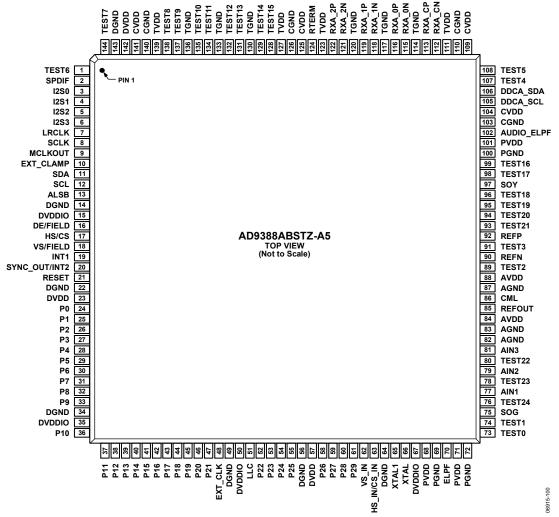

Figure 6. AD9388ABSTZ-A5 Derivative Pin Configuration

**Table 7. Pin Function Descriptions**

| Pin No.                                                       | Mnemonic                                          | Type <sup>1</sup> | Description                                                      |

|---------------------------------------------------------------|---------------------------------------------------|-------------------|------------------------------------------------------------------|

| 14, 22, 34, 49, 56, 64, 143                                   | DGND                                              | G                 | Digital Ground.                                                  |

| 82, 83, 87                                                    | AGND                                              | G                 | Analog Ground.                                                   |

| 69, 72, 100                                                   | PGND                                              | G                 | PLL Ground.                                                      |

| 103, 110, 126, 140                                            | CGND                                              | G                 | Comparator Ground.                                               |

| 114, 117, 120, 130,<br>133, 136                               | TGND                                              | G                 | Terminator Ground.                                               |

| 15, 35, 50, 67                                                | DVDDIO                                            | Р                 | Digital I/O Supply Voltage (3.3 V).                              |

| 23, 57, 142                                                   | DVDD                                              | Р                 | Digital Core Supply Voltage (1.8 V).                             |

| 84, 88                                                        | AVDD                                              | Р                 | Analog Supply Voltage (1.8 V).                                   |

| 68, 71, 101                                                   | PVDD                                              | Р                 | Audio and Video PLL Supply Voltage (1.8 V).                      |

| 104, 109, 125, 141                                            | CVDD                                              | Р                 | HDMI Comparator, TMDS PLL, and Equalizer Supply Voltage (1.8 V). |

| 111, 123, 127, 139                                            | TVDD                                              | Р                 | Terminator Supply Voltage (3.3 V).                               |

| 128, 129, 131, 132, 134,<br>135, 137, 138, 108, 91,<br>74, 73 | TEST15 to TEST8,<br>TEST5, TEST3,<br>TEST1, TEST0 | I                 | Test Pins. Do not connect.                                       |

| 76, 78, 80, 93, 94, 95,<br>96, 98, 99                         | Test 24 to Test16                                 | 1                 | Test Pins. Connect to AGND through a 10 $k\Omega$ resistor.      |

| 89                                                            | TEST2                                             | 0                 | Test Pin. Do not connect.                                        |

| 107                                                           | TEST4                                             | I/O               | Test Pin. Do not connect.                                        |

| 77, 79, 81                                                    | AIN1 to AIN3                                      | 1                 | Analog Video Input Channel.                                      |

Pov. B | Page 13 of 29

| Pin No.             | Mnemonic         | Type <sup>1</sup> | Description                                                                                                                                         |

|---------------------|------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 24 to 33, 36 to 47, | P0 to P29        | 0                 | Video Pixel Output Port.                                                                                                                            |

| 52 to 55, 58 to 61  |                  |                   | ·                                                                                                                                                   |

| 19                  | INT1             | 0                 | Interrupt. Can be active low or active high. The set of events that triggers an                                                                     |

| 20                  | CVAIC CLIT/INITS |                   | interrupt is under user control.                                                                                                                    |

| 20                  | SYNC_OUT/INT2    | 0                 | Sliced Synchronization Output Signal (SYNC_OUT).                                                                                                    |

| 17                  | LIC/CC           |                   | Interrupt Signal (INT2).                                                                                                                            |

| 17                  | HS/CS            | 0                 | Horizontal Synchronization Output Signal (HS).                                                                                                      |

|                     |                  |                   | Composite Synchronization (CS). A single signal containing both horizontal and vertical synchronization pulses.                                     |

| 18                  | VS/FIELD         | 0                 | Vertical Synchronization Output Signal (VS).                                                                                                        |

|                     |                  |                   | Field Synchronization (FIELD). Field synchronization output signal in all                                                                           |

|                     |                  |                   | interlaced video modes.                                                                                                                             |

| 16                  | DE/FIELD         | 0                 | Data Enable Signal (DE). Indicates active pixel data.                                                                                               |

|                     |                  |                   | Field Synchronization (FIELD). Field synchronization output signal in all                                                                           |

|                     |                  |                   | interlaced video modes.                                                                                                                             |

| 11                  | SDA              | I/O               | I <sup>2</sup> C Port Serial Data Input/Output Pin. SDA is the data line for the control port.                                                      |

| 12                  | SCL              | 1                 | I <sup>2</sup> C Port Serial Clock Input. (Maximum clock rate of 400 kHz.) SCL is the clock                                                         |

| 12                  | AL CD            | 1.                | line for the control port.                                                                                                                          |

| 13<br>21            | ALSB<br>RESET    |                   | This pin sets the second LSB of each AD9388A register map.  System Reset Input. Active low. A minimum low reset pulse width of 5 ms is              |

| 21                  | KESET            | 1                 | required to reset the AD9388A circuitry.                                                                                                            |

| 51                  | LLC              | 0                 | Line-Locked Output Clock for Pixel Data. Range is 13.5 MHz to 170 MHz.                                                                              |

| 65                  | XTAL1            | 0                 | This pin should be connected to the 28.63636 MHz crystal or left as a no connect                                                                    |

|                     |                  |                   | if an external 3.3 V 28.63636 MHz clock oscillator source is used to clock the                                                                      |

|                     |                  |                   | AD9388A. In crystal mode, the crystal must be a fundamental crystal.                                                                                |

| 66                  | XTAL             | I                 | Input Pin for the 28.63636 MHz Crystal. This pin can be overdriven by an                                                                            |

| 70                  | ELPF             |                   | external 3.3 V 28.63636 MHz clock oscillator source to clock the AD9388A.  The recommended external loop filter must be connected to this ELPF pin. |

| 102                 | AUDIO_ELPF       | 0                 | The recommended external loop filter must be connected to this ELPF pin.  The recommended external loop filter must be connected to AUDIO_ELPF.     |

| 85                  | REFOUT           | 0                 | Internal Voltage Reference Output.                                                                                                                  |

| 86                  | CML              | 0                 | Common-Mode Level for the Internal ADCs.                                                                                                            |

| 90                  | REFN             |                   | Internal Voltage Output.                                                                                                                            |

| 92                  | REFP             | li                | Internal Voltage Output.                                                                                                                            |

| 63                  | HS_IN/CS_IN      | 1                 | HS Input Signal. Used in analog mode for 5-wire timing mode.                                                                                        |

|                     |                  |                   | CS Input Signal. Used in analog mode for 4-wire timing mode.                                                                                        |

|                     |                  |                   | For optimal performance, a $100 \Omega$ series resistor is recommended on the                                                                       |

|                     |                  |                   | HS_IN/CS_IN pin.                                                                                                                                    |

| 62                  | VS_IN            | I                 | VS Input Signal. This pin is used in analog mode for 5-wire timing mode. For                                                                        |

| 75                  | 505              | 1.                | optimal performance, a 100 $\Omega$ series resistor is recommended on the VS_IN pin.                                                                |

| 75                  | SOG              |                   | Synchronization-on-Green Input. This pin is used in embedded synchronization mode.                                                                  |

| 97                  | SOY              | 1.                | Synchronization-on-Luma Input. This pin is used in embedded                                                                                         |

|                     |                  |                   | synchronization mode.                                                                                                                               |

| 112                 | RXA_CN           | 1                 | Digital Input Clock Complement of Port A in the HDMI Interface.                                                                                     |

| 113                 | RXA_CP           | 1                 | Digital Input Clock True of Port A in the HDMI Interface.                                                                                           |

| 115                 | RXA_0N           | 1                 | Digital Input Channel 0 Complement of Port A in the HDMI Interface.                                                                                 |

| 116                 | RXA_0P           | 1                 | Digital Input Channel 0 True of Port A in the HDMI Interface.                                                                                       |

| 118                 | RXA_1N           | 1                 | Digital Input Channel 1 Complement of Port A in the HDMI Interface.                                                                                 |

| 119                 | RXA_1P           |                   | Digital Input Channel 1 True of Port A in the HDMI Interface.                                                                                       |

| 121                 | RXA_2N           |                   | Digital Input Channel 2 Complement of Port A in the HDMI Interface.                                                                                 |

| 122                 | RXA_2P           |                   | Digital Input Channel 2 True of Port A in the HDMI Interface.                                                                                       |

| 106                 | DDCA_SDA         | 1/0               | HDCP Slave Serial Data Port A.                                                                                                                      |

| 1                   | TEST6            | I/O               | Test Pin. Do not connect.                                                                                                                           |

| 105                 | DDCA_SCL         |                   | HDCP Slave Serial Clock Port A.                                                                                                                     |

| 144                 | TEST7            | Ţ                 | Test Pin. Connect this pin to DGND using a 10 k $\Omega$ resistor.                                                                                  |

Pov. B | Page 14 of 29

| Pin No. | Mnemonic  | Type <sup>1</sup> | Description                                                                                           |

|---------|-----------|-------------------|-------------------------------------------------------------------------------------------------------|

| 2       | SPDIF     | 0                 | SPDIF Digital Audio Output.                                                                           |

| 3       | 12S0      | 0                 | I <sup>2</sup> S Audio (Channel 1 and Channel 2).                                                     |

| 4       | I2S1      | 0                 | I <sup>2</sup> S Audio (Channel 3 and Channel 4).                                                     |

| 5       | I2S2      | 0                 | I <sup>2</sup> S Audio (Channel 5 and Channel 6).                                                     |

| 6       | I2S3      | 0                 | I <sup>2</sup> S Audio (Channel 7 and Channel 8).                                                     |

| 7       | LRCLK     | 0                 | LRCLK, Data Output Clock for Left and Right Audio Channels.                                           |

| 8       | SCLK      | 0                 | Audio Serial Clock Output.                                                                            |

| 9       | MCLKOUT   | 0                 | Audio Master Clock Output.                                                                            |

| 10      | EXT_CLAMP | 1                 | External Clamp Signal. This is an optional mode of operation for the AD9388A.                         |

| 48      | EXT_CLK   | I                 | Clock Input for External Clock and Clamp Mode. This is an optional mode of operation for the AD9388A. |

| 124     | RTERM     | 1                 | Sets Internal Termination Resistance. Connect this pin to TGND using a 500 $\Omega$ resistor.         |

$<sup>^{1}</sup>$  G = ground, P = power, I = input, and O = output.

Pov. R | Page 15 of 29

## **FUNCTIONAL OVERVIEW**

The following overview provides a brief description of the functionality of the AD9388A. More details are available in the Theory of Operation section.

#### **ANALOG FRONT END**

The analog front end of the AD9388A provides three high quality 10-bit ADCs to enable true 10-bit video decoding, a multiplexer with 12 analog input channels to enable a multisource connection without the requirement of an external multiplexer, and three current and voltage clamp control loops to ensure that dc offsets are removed from the video signal.

### **HDMI RECEIVER**

The AD9388A is compatible with the HDMI 1.3 specification. The AD9388A supports all HDTV formats up to 1080p in nondeep color mode and 1080p in 36-bit deep color mode. Furthermore, it supports all display resolutions up to UXGA  $(1600 \times 1200 \text{ at } 60 \text{ Hz})$ .

This device includes the following features:

- Adaptive front-end equalization for HDMI operation over cable lengths of up to 30 meters.

- Synchronization conditioning for higher performance in strenuous conditions.

- Audio mute for removing extraneous noises.

- Programmable data island packet interrupt generator.

# COMPONENT PROCESSOR PIXEL DATA OUTPUT MODES

The AD9388A features single data rate outputs as follows:

- 8-/10-bit 4:2:2 YCrCb for 525i, 625i.

- 16-/20-bit 4:2:2 YCrCb for all standards.

- 24-/30-bit 4:4:4 YCrCb/RGB for all standards.

### **COMPONENT VIDEO PROCESSING**

The AD9388A supports 525i, 625i, 525p, 625p, 720p, 1080i, 1080p, and many other HDTV formats; automatic adjustment of gain (contrast) and offset (brightness); manual adjustment controls; analog component YPrPb/RGB video formats with embedded synchronization or with separate HS, VS, or CS; YCrCb-to-RGB and RGB-to-YCrCb conversions by any-to-any,  $3 \times 3$ , color-space conversion matrices; and user-defined pixel sampling for nonstandard video sources.

In addition, the AD9388A features brightness, saturation, and hue controls. System level component format detection is enabled by standard identification (STDI), and a synchronization source polarity detector (SSPD) determines the source and polarity of the synchronization signals that accompany the input video.

Certified Macrovision\* copy-protection detection is available on component formats (525i, 625i, 525p, and 625p).

When no video input is present, stable timing is provided by the free run output mode.

### **RGB GRAPHICS PROCESSING**

The AD9388A provides 170 MSPS conversion rate support of RGB input resolutions up to  $1600 \times 1200$  at 60 Hz (UXGA).

The AD9388A offers automatic or manual clamp and gain controls for graphics modes.

Similar to the component video processing features, the RBG graphics processing for the AD9388A features contrast and brightness controls, automatic detection of synchronization source and polarity by the SSPD block, standard identification enabled by the STDI block, and user-defined pixel sampling support for nonstandard video sources.

Additional RGB graphics processing features of the AD9388A include the following:

- Sampling PLL clock with 500 ps p-p jitter at 150 MSPS.

- 32-phase DLL support of optimum pixel clock sampling.

- Color-space conversion of RGB to YCrCb and decimation to a 4:2:2 format for videocentric, back-end IC interfacing.

- Data enable (DE) output signal supplied for direct connection to HDMI/DVI transmitter IC.

#### **GENERAL FEATURES**

The AD9388A offers a high quality multiformat video decoder and digitizer that features HS, VS, and FIELD output signals with programmable position, polarity, and width; programmable interrupt request output pins (INT1 and INT2); low power consumption: 1.8 V digital core and analog input, 3.3 V digital input/output, low power power-down mode; and a temperature range of  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  in a 144-lead, 20 mm  $\times$  20 mm, RoHS-compliant LQFP.

## THEORY OF OPERATION

## **ANALOG FRONT END**

The AD9388A analog front end comprises three 10-bit ADCs that digitize the analog video signal before applying it to the CP. The analog front end uses differential channels to each ADC to ensure high performance in a mixed-signal application.

The front end also includes a 12-channel input multiplexer that enables multiple video signals to be applied to the AD9388A. Current and voltage clamps are positioned in front of each ADC to ensure that the video signal remains within the range of the converter. Fine clamping of the video signals is performed downstream by digital fine clamping in the CP.

For component 525i, 625i, 525p, and 625p sources,  $2\times$  oversampling is performed, but  $4\times$  oversampling is available for component 525i and 625i. All other video standards are  $1\times$  oversampled. Oversampling the video signals reduces the cost and complexity of external antialiasing (AA) filters with the benefit of an increased signal-to-noise ratio (SNR).

#### **HDMI RECEIVER**

The HDMI receiver on the AD9388A incorporates active equalization of the HDMI data signals. This equalization compensates for the high frequency losses inherent in HDMI and DVI cables, especially those with long lengths and high frequencies. It is capable of equalizing for cable lengths up to 30 meters to achieve robust receiver performance at the highest HDMI data rates.

With the inclusion of HDCP, displays can receive encrypted video content. The HDMI interface of the AD9388A allows for authentication of a video receiver, decryption of encoded data at the receiver, and renewability of that authentication during transmission as specified by the HDCP 1.3 protocol.

The HDMI receiver also offers advanced audio functionality. The receiver contains an audio mute controller that can detect a variety of selectable conditions that may result in audible extraneous noise in the audio output. Upon detection of these conditions, the audio data can be ramped to prevent audio clicks and pops.

### **COMPONENT PROCESSOR (CP)**

The CP is capable of decoding and digitizing a wide range of component video formats in any color space. Component video standards supported by the CP include 525i, 625i, 525p, 625p, 720p, 1080i, 1080p, 1250i, VGA up to UXGA at 60 Hz, and many other standards.

The CP section of the AD9388A contains an AGC block. This block is followed by a digital clamp circuit that ensures that the video signal is clamped to the correct blanking level. Automatic adjustments within the CP include gain (contrast) and offset (brightness); however, manual adjustment controls are also supported. If no embedded synchronization is present, the video gain can be set manually.

A fully programmable, any-to-any  $3 \times 3$  color-space converter is placed before the CP section. This enables YPrPb-to-RGB and RGB-to-YCrCb conversions. Many other standards of color space can be implemented using the color-space converter.

A second fully programmable, any-to-any  $3 \times 3$  color space converter is placed in the back end of the CP core. This color space converter features advanced color controls such as contrast, saturation, brightness, and hue controls.

The output section of the CP can be configured in single data rate (SDR) mode with one data packet per clock cycle. In SDR mode, a 16-/20-bit 4:2:2 or 24-/30-bit 4:4:4 output is possible. In these modes, HS/CS, VS/FIELD, and DE/FIELD (where applicable) timing reference signals are provided.

The CP section contains circuitry to enable the detection of Macrovision-encoded YPrPb signals for 525i, 625i, 525p, and 625p. It is designed to be fully robust when decoding these types of signals.

## **VBI DATA PROCESSOR**

VBI extraction of CGMS data is performed by the VBI data processor (VDP) section of the AD9388A for interlaced, progressive, and high definition scanning rates. The data extracted is read back over the I<sup>2</sup>C interface.

For more detailed product information about the AD9388A, send an e-mail to video.products@analog.com or contact a local Analog Devices sales representative.

## PIXEL OUTPUT FORMATTING

Note that unused pins of the pixel output port are driven with a low voltage.

Table 8. Component Processor Pixel Output Pin Map (P19 toP0)

|                        |                                                               |     |                                                |       |         |          |         | Out    | out o                                        | f Da                                        | ta P                                      | ort Pi                                       | ns P[   | 19:0]   |         |         |         |        |        |   |   |

|------------------------|---------------------------------------------------------------|-----|------------------------------------------------|-------|---------|----------|---------|--------|----------------------------------------------|---------------------------------------------|-------------------------------------------|----------------------------------------------|---------|---------|---------|---------|---------|--------|--------|---|---|