# austriamicrosystems

# Serially Interfaced, 4-Digit LED Driver **AS1105**

**DATA SHEET**

## **Key Features**

- Cost effective version of AS1100 functionality for applications up to 4-Digits

- 10MHz Serial Interface

- Individual LED Segment Control

- Decode/No-Decode Digit Selection

- 20µA Low-Power Shutdown (Data Retained)

- Extremely low Operating Current 0.5mA in open loop

- Digital and Analog Brightness Control

- Display Blanked on Power-Up

- Drive Common-Cathode LED Display

- Software Reset<sup>1</sup>

- Optional External clock

- 20 pin SO Packages

### **General Description**

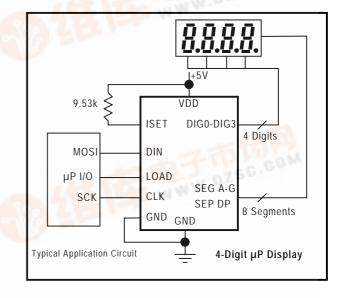

The AS1105 is an LED driver for 7 segment numeric displays of up to 4 digits. The AS1105 can be programmed via a conventional 4 wire serial interface. It includes a BCD code-B decoder, a multiplex scan circuitry, segment and display drivers and a 32 Bit memory. The memory is used to store the LED settings, so that continuous reprogramming is not necessary.

Every individual segment can be addressed and updated separately. Only one external resistor is required to set the current through the LED display. Brightness can be controlled either in an analog or digital way. The user can choose the internal code-B decoder to display numeric digits or to address each segment directly. The AS1105 features an extremely low shutdown current of only 20µA. and an operational current of less than 500µA. The number of visible digits can be programmed as well. The AS1105 can be reset by software and an external clock can be used. Several test modes support easy debugging.

AS1105 is offered in a 20 SOIC package.

## **Applications**

- Bar-Graph Displays

- Industrial Controllers

- Panel Meters

- LED Matrix Displays

- White Goods

Software Reset and external clock are not supported by MAX7219

Page 1 of 12

# **Absolute Maximum Ratings**

| Voltage (with respect to GND)                                        |                      |

|----------------------------------------------------------------------|----------------------|

| VDD                                                                  | -0.3V to 6V          |

| DIN, CLK, LOAD                                                       | -0.3V to 6V          |

| All Other Pins                                                       | -0.3V to (VDD +0.3V) |

|                                                                      |                      |

| Current                                                              |                      |

| DIG0-DIG3 Sink Current                                               | 500mA                |

| SEGA-G, DP Source Current                                            | 100mA                |

|                                                                      |                      |

| Continuous Power Dissipation (TA = +85°C)                            |                      |

| Wide SO (derate 11.8mW/°C above +70°C)                               | 941mW                |

|                                                                      |                      |

| Operating Temperature Ranges (T <sub>MIN</sub> to T <sub>MAX</sub> ) |                      |

| AS1105xL                                                             | 0°C to +70°C         |

| AS1105xE                                                             | -40°C to +85°C       |

| Storage Temperature Range                                            | -65°C to +150°C      |

| Package body temperature <sup>2</sup>                                | +240°C               |

### **Electrical Characteristics**

(VDD = 5V,  $R_{SET}$  = 9.53k $\Omega$ ±1%,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| Parameter                         | Symbol             | Conditions                                                  | Min | Тур | Max  | Units |

|-----------------------------------|--------------------|-------------------------------------------------------------|-----|-----|------|-------|

| Operating Supply Voltage          | VDD                |                                                             | 4.0 | 5.0 | 5.5  | V     |

| Shutdown Supply Current           | IDDsd              | All digital inputs at VDD or GND, T <sub>A</sub> = +25°C    |     | 20  | 50   | μA    |

|                                   |                    | R <sub>SET</sub> = open circuit                             |     |     | 500  | μΑ    |

| Operating Supply Current          | IDD                | All segments and decimal point on, I <sub>SEG</sub> = -40mA |     | 330 |      | mA    |

| Display Scan Rate                 | fosc               |                                                             | 500 | 800 | 1300 | Hz    |

| Digit Drive Sink Current          | I <sub>DIGIT</sub> | Vout = 0.65V                                                | 320 |     |      | mA    |

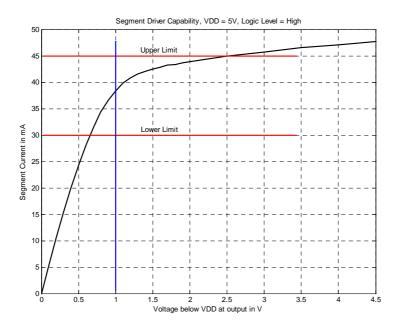

| Segment Drive Source Current      | I <sub>SEG</sub>   | $T_A = +25$ °C, $V_{OUT} = (VDD -1V)$                       | -30 | -40 | -45  | mA    |

| Segment Drive Current<br>Matching | $\Delta I_{SEG}$   |                                                             |     | 3.0 |      | %     |

| Digit Drive Source Current        | I <sub>DIGIT</sub> | Digit off, V <sub>DIGIT</sub> = (VDD -0.3V)                 | -2  |     |      | mA    |

| Segment Drive Sink Current        | I <sub>SEG</sub>   | Segment off, V <sub>SEG</sub> = 0.3V                        | 5   |     |      | mA    |

| Logic Inputs                      |                    |                                                             |     |     |      |       |

| Input Current DIN, CLK, LOAD      | lih, lil           | V <sub>IN</sub> = 0V or VDD                                 | -1  |     | 1    | μΑ    |

| Logic High Input Voltage          | $V_{IH}$           |                                                             | 3.5 |     |      | V     |

The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020B "Moisture/Reflow Sensitivity Classification for non-hermetic Solid State Surface Mount Devices".

Revision 1.32 Oct. 2004

| Parameter                     | Symbol            | Conditions               | Min     | Тур | Max  | Units |

|-------------------------------|-------------------|--------------------------|---------|-----|------|-------|

| Logic Low Input Voltage       | $V_{IL}$          |                          |         |     | 0.8  | V     |

| Output High Voltage           | Vон               | DOUT, Isource = -1mA     | VDD - 1 |     |      | V     |

| Output Low Voltage            | Vol               | DOUT, Isink = 1.6mA      |         |     | 0.4  | V     |

| Hysteresis Voltage            | Vı                | DIN, CLK, LOAD           |         | 1   |      | V     |

| Timing Characteristics        |                   |                          | •       |     |      |       |

| CLK Clock Period              | tcp               |                          | 100     |     |      | ns    |

| CLK Pulse Width High          | tсн               |                          | 50      |     |      | ns    |

| CLK Pulse Width Low           | tcL               |                          | 50      |     |      | ns    |

| CLK Rise to LOAD Rise Hold    | taau              |                          | 0       |     |      | ns    |

| Time                          | t <sub>CSH</sub>  |                          | 0       |     |      | 113   |

| DIN Setup Time                | t <sub>DS</sub>   |                          | 25      |     |      | ns    |

| DIN Hold Time                 | t <sub>DH</sub>   |                          | 0       |     |      | ns    |

| Output Data Propagation Delay | t <sub>DO</sub>   | C <sub>LOAD</sub> = 50pF |         |     | 25   | ns    |

| LOAD Rising Edge to Next      | t                 |                          | 50      |     |      | nc    |

| Clock Rising Edge             | tldck             |                          | 30      |     |      | ns    |

| Minimum LOAD Pulse High       | tcsw              |                          | 50      |     |      | ns    |

| Data-to-Segment Delay         | t <sub>DSPD</sub> |                          |         |     | 2.25 | ms    |

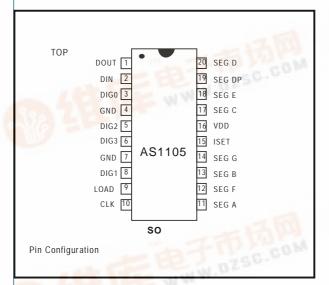

# Pin Description

| Pin          | Name           | Function                                                                                                                                                                                                                                              |

|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | DOUT           | Serial data output for cascading drivers. The output is valid after 16.5 clock cycles. The output is never set to high impedance.                                                                                                                     |

| 2            | DIN            | Data input. Data is programmed into the 16Bit shift register on the rising CLK edge                                                                                                                                                                   |

| 3,8,5,6      | DIG0-DIG3      | 4 digit driver lines that sink the current from the common cathode of the display. In shutdown mode the AS1105 switches the outputs to VDD                                                                                                            |

| 4, 7         | GND            | both GND pins must be connected                                                                                                                                                                                                                       |

| 9            | LOAD           | Strobe input. With the rising edge of the LOAD signal the 16 bit of serial data is latched into the register.                                                                                                                                         |

| 10           | CLK            | Clock input. The interface is capable to support clock frequencies up to 10MHz. The serial data is clocked into the internal shift register with the rising edge of the CLK signal. On the DOUT pin the data is applied with the falling edge of CLK. |

| 11–14, 17–20 | SEG A-G,<br>DP | Seven segment driver lines including the decimal point. When a segment is turned off the output is connected to GND.                                                                                                                                  |

| 15           | ISET           | The current into $I_{\text{SET}}$ determines the peak current through the segments and therefore the brightness.                                                                                                                                      |

| 16           | VDD            | Positive Supply Voltage (+5V)                                                                                                                                                                                                                         |

Revision 1.32 Oct 2004

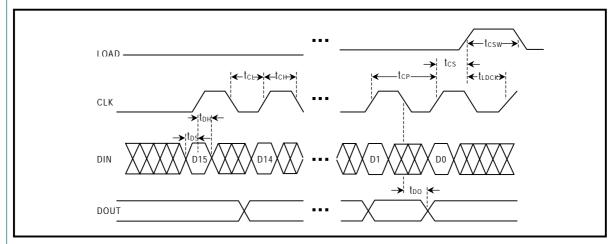

Figure 1: Timing diagram

| D15 | D14 | D13 | D12 | D11 | D10     | D9 | D8 | D7 | D6 | D5 | D4 | D3  | D2 | D1 | D0  |

|-----|-----|-----|-----|-----|---------|----|----|----|----|----|----|-----|----|----|-----|

| Χ   | Χ   | Χ   | Χ   |     | Address |    |    |    | 1  |    | D  | ata |    |    | LSB |

Table 1: Serial data format (16 bits)

## **Detailed Description**

#### Serial-Addressing Modes

Programming of the AS1105 is done via the 4 wire serial interface. A programming sequence consists of 16-bit packages. The data is shifted into the internal 16 Bit register with the rising edge of the CLK signal. With the rising edge of the LOAD signal the data is latched into a digital or control register depending on the address. The LOAD signal must go to high after the 16th rising clock edge. The LOAD signal can also come later but just before the next rising edge of CLK, otherwise data would be lost. The content of the internal shift register is applied 16.5 clock cycles later to the DOUT pin. The data is clocked out at the falling edge of CLK. The Bits of the 16Bitprogramming package are described in table 1. The first 4 Bits D15-D12 are "don't care, D11-D8 contain the address and D7-D0 contain the data. The first bit is D15, the most significant bit (MSB). The exact timing is given in figure 1.

#### Digit and Control Registers

The AS1105 incorporates 12 registers, which are listed in Table 2. The digit and control registers are selected via the 4Bit address word. The 4 digit registers are realized with a

32bit memory. Each digit can be controlled directly without rewriting the whole contents. The control registers consist of decode mode, display intensity, number of scanned digits, shutdown, display test and reset/external clock register.

#### Shutdown Mode

The AS1105 features a shutdown mode, where it consumes only  $20\mu A$  current. The shutdown mode is entered via a write to register 0Ch. Then all segment current sources are pulled to ground and all digit drivers are connected to VDD, so that nothing is displayed. All internal digit registers keep the programmed values. The shutdown mode can either be used for power saving or for generating a flashing display by repeatedly entering and leaving the shutdown mode. The AS1105 needs typically 250 $\mu$ s to exit the shutdown mode. During shutdown the AS1105 is fully programmable. Only the display test function overrides the shutdown mode.

#### Initial Power-Up

After powering up the system all register are reset, so that the display is blank. The AS1105 starts the shutdown mode. All registers should be programmed for normal operation. The default settings enable only scan of one digit, the internal decoder is disabled, data register and intensity register are set to the minimum value.

Revision 1.32 Oct. 2004 Page 4 of 12

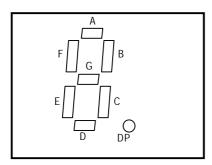

#### Decode-Mode Register

In the AS1105 a BCD decoder is included. Every digit can be selected via register 09h to be decoded. The BCD code consists of the numbers 0-9, E,H, L,P and -. In register 09h a logic high enables the decoder for the appropriate digit. In case that the decoder is bypassed (logic low) the data Bits D7-D0 correspond to the segment lines of the AS1105. In table 4 some possible settings for register 09h are shown. Bit D7, which corresponds to the decimal point, is not affected by the settings of the decoder. Logic high means that the decimal point is displayed. In table 5 the font of the Code B decoder is shown. In table 6 the correspondence of the register to the appropriate segments of a 7 segment display is shown (see figure 2)

#### Intensity Control and Interdigit Blanking

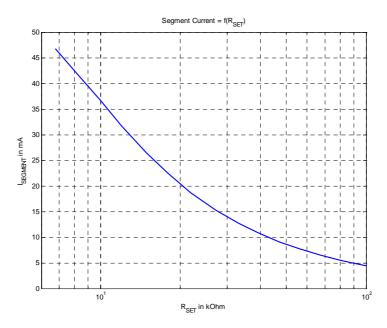

Brightness of the display can be controlled in an analog way by changing the external resistor (R<sub>SET</sub>). The current, which flows between VDD and I<sub>SET</sub>, defines the current that flows through the LEDs. The LED current is 100 times the I<sub>SET</sub> current. The minimum value of R<sub>SET</sub> should be 9.53k $\Omega$ , which corresponds to 40mA segment current. The brightness of the display can also be controlled digitally via register 0Ah. The brightness can be programmed in 16 steps and is shown in table 7. An internal pulse width modulator controls the intensity of the display.

### Scan-Limit Register

The scan limit register 0Bh selects the number of digits displayed. When all 4 digits are displayed the update frequency is typically 800Hz. If the number of digits displayed is reduced, the update frequency is reduced as well. The frequency can be calculated using 8fOSC/N, where N is the number of digits. Since the number of displayed digits influences the brightness, the resistor R<sub>SET</sub>

should be adjusted accordingly. Table 9 shows the maximum allowed current, when fewer than 4 digits are used. To avoid differences in brightness the scan limit register should not be used to blank portions of the display (leading zeros).

| Dogistor        |         | Addr | ess |    |          | Hex  |

|-----------------|---------|------|-----|----|----------|------|

| Register        | D15-D12 | D11  | D10 | D9 | D8       | Code |

| No-Op           | Х       | 0    | 0   | 0  | 0        | 0xx0 |

| Digit 0         | Х       | 0    | 0   | 0  | 1        | 0xX1 |

| Digit 1         | Х       | 0    | 0   | 1  | 0        | 0xX2 |

| Digit 2         | Х       | 0    | 0   | 1  | 1        | 0xX3 |

| Digit 3         | Х       | 0    | 1   | 0  | 0        | 0xX4 |

| Decode          | Х       | 1    | 0   | 0  | 1        | 0xX9 |

| Mode            | ^       | '    | U   | 0  | <b>'</b> | UXX  |

| Intensity       | Х       | 1    | 0   | 1  | 0        | 0xXA |

| Scan Limit      | X       | 1    | 0   | 1  | 1        | 0xXB |

| Shutdown        | Х       | 1    | 1   | 0  | 0        | 0xXC |

| Not used        | Х       | 1    | 1   | 0  | 1        | 0xXD |

| Reset and       | Х       | 1    | 1   | 1  | 0        | 0xXE |

| ext. Clock      | ^       | '    | '   |    | "        | UNNL |

| Display<br>Test | Х       | 1    | 1   | 1  | 1        | 0xXF |

Table 2: Register address map

|                     | Address Code |    | Register Data |    |    |    |    |    |    |  |

|---------------------|--------------|----|---------------|----|----|----|----|----|----|--|

| Mode                | (Hex)        | D7 | D6            | D5 | D4 | D3 | D2 | D1 | D0 |  |

| Shutdown<br>Mode    | 0xXC         | Χ  | Χ             | Χ  | Χ  | Χ  | Χ  | Χ  | 0  |  |

| Normal<br>Operation | 0xXC         | Χ  | Х             | Х  | Χ  | Х  | Χ  | Χ  | 1  |  |

Table 3: Shutdown register format (address (hex) = 0xXC)

| Decode Mode               |    |    | R  | egist | er Dat | a  |    |    | Hex Code |  |

|---------------------------|----|----|----|-------|--------|----|----|----|----------|--|

| Decode Mode               | D7 | D6 | D5 | D4    | D3     | D2 | D1 | D0 | Hex Code |  |

| No decode for digits 4-0  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  | 0x00     |  |

| Code B decode for digit 0 | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 1  | 0x01     |  |

| No decode for digits 4-1  |    | 0  | 0  | 0     | 0      | 0  | 0  | '  | 0.001    |  |

| Code B decode for digits  | 0  | 0  | 0  | 0     | 1      | 1  | 1  | 1  | 0x0F     |  |

| 3–0                       | 0  | U  | 0  | 0     |        | '  | '  | '  | UXUI     |  |

| Code B decode for digits  | 1  | 1  | 1  | 1     | 1      | 1  | 1  | 1  | 0xFF     |  |

| 4–0                       | '  | '  | '  | '     |        | '  | '  | '  | UAFF     |  |

Table 4: Decode-mode register examples (address (hex) = 0xX9)

Revision 1.32 Oct. 2004 Page 5 of 12

| 7-Segment | Register Data On Segments = 1 |       |    |    |    |    |     |   |   |   |   |   |   |   |

|-----------|-------------------------------|-------|----|----|----|----|-----|---|---|---|---|---|---|---|

| Character | D7*                           | D6-D4 | D3 | D2 | D1 | D0 | DP* | Α | В | С | D | E | F | G |

| 0         |                               | Χ     | 0  | 0  | 0  | 0  |     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1         |                               | Х     | 0  | 0  | 0  | 1  |     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2         |                               | Х     | 0  | 0  | 1  | 0  |     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3         |                               | Х     | 0  | 0  | 1  | 1  |     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4         |                               | Χ     | 0  | 1  | 0  | 0  |     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5         |                               | Χ     | 0  | 1  | 0  | 1  |     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6         |                               | Χ     | 0  | 1  | 1  | 0  |     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7         |                               | Χ     | 0  | 1  | 1  | 1  |     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8         |                               | Х     | 1  | 0  | 0  | 0  |     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9         |                               | Χ     | 1  | 0  | 0  | 1  |     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| _         |                               | Χ     | 1  | 0  | 1  | 0  |     | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| E         |                               | Χ     | 1  | 0  | 1  | 1  |     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| Н         |                               | Х     | 1  | 1  | 0  | 0  |     | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| L         |                               | Х     | 1  | 1  | 0  | 1  |     | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| Р         |                               | Х     | 1  | 1  | 1  | 0  |     | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| blank     |                               | Х     | 1  | 1  | 1  | 1  |     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Table 5: Code B font

<sup>\*</sup>The decimal point is set by bit D7 = 1

|               |    | Register Data |    |    |    |    |    |    |  |  |  |  |

|---------------|----|---------------|----|----|----|----|----|----|--|--|--|--|

|               | D7 | D6            | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

| Corresponding | DP | Δ             | В  | C  | D  | F  | F  | G  |  |  |  |  |

| Segment Line  | Di |               | Б  | C  | D  | _  | '  | U  |  |  |  |  |

Table 6: No-decode mode data bits and corresponding segment lines

Figure 2: Standard 7-segment LED

Revision 1.32 Oct 2004

| Duty Cycle     | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex Code |

|----------------|----|----|----|----|----|----|----|----|----------|

| 1/32 (min on)  | Χ  | Χ  | Χ  | Χ  | 0  | 0  | 0  | 0  | 0xx0     |

| 3/32           | Χ  | Χ  | Χ  | Χ  | 0  | 0  | 0  | 1  | 0xX1     |

| 5/32           | Χ  | Χ  | Χ  | Χ  | 0  | 0  | 1  | 0  | 0xX2     |

| 7/32           | Χ  | Χ  | Χ  | Χ  | 0  | 0  | 1  | 1  | 0xX3     |

| 9/32           | Χ  | Χ  | Χ  | Χ  | 0  | 1  | 0  | 0  | 0xX4     |

| 11/32          | Χ  | Χ  | Χ  | Χ  | 0  | 1  | 0  | 1  | 0xX5     |

| 13/32          | Χ  | Χ  | Χ  | Χ  | 0  | 1  | 1  | 0  | 0xX6     |

| 15/32          | Χ  | Χ  | Χ  | Χ  | 0  | 1  | 1  | 1  | 0xX7     |

| 17/32          | Χ  | Χ  | Χ  | Χ  | 1  | 0  | 0  | 0  | 0xX8     |

| 19/32          | Χ  | Χ  | Χ  | Χ  | 1  | 0  | 0  | 1  | 0xX9     |

| 21/32          | Χ  | Χ  | Χ  | Χ  | 1  | 0  | 1  | 0  | 0xXA     |

| 23/32          | Χ  | Χ  | Χ  | Χ  | 1  | 0  | 1  | 1  | 0xXB     |

| 25/32          | Χ  | Χ  | Χ  | Χ  | 1  | 1  | 0  | 0  | 0xXC     |

| 27/32          | Χ  | Χ  | Χ  | Χ  | 1  | 1  | 0  | 1  | 0xXD     |

| 29/32          | Χ  | Χ  | Χ  | Χ  | 1  | 1  | 1  | 0  | 0xXE     |

| 31/32 (max on) | Χ  | Χ  | Χ  | Χ  | 1  | 1  | 1  | 1  | 0xXF     |

Table 7: Intensity register format (address (hex) = 0xXA)

| Coon Limit             |    |    | Hex Code |    |    |    |    |    |          |

|------------------------|----|----|----------|----|----|----|----|----|----------|

| Scan Limit             | D7 | D6 | D5       | D4 | D3 | D2 | D1 | D0 | HEX COUC |

| Display digit 0 only   | Χ  | Χ  | Χ        | Χ  | Χ  | 0  | 0  | 0  | 0xx0     |

| Display digits 0 & 1   | Χ  | Χ  | Χ        | Χ  | Χ  | 0  | 0  | 1  | 0xX1     |

| Display digits 0 1 2   | Χ  | Χ  | Χ        | Χ  | Χ  | 0  | 1  | 0  | 0xX2     |

| Display digits 0 1 2 3 | Χ  | Χ  | Χ        | Χ  | Χ  | 0  | 1  | 1  | 0xX3     |

Table 8: Scan-limit register format (address (hex) = 0xXB)

### Display Test Register

With the display test register 0Fh all LED can be tested. In the test mode all LEDs are switched on at maximum brightness (duty cycle 31/32). All programming of digit and control registers is maintained. The format of the register is given in table 10.

| Number of<br>Digits<br>Displayed | Maximum<br>Segment Current<br>(mA) |

|----------------------------------|------------------------------------|

| 1                                | 10                                 |

| 2                                | 20                                 |

| 3                                | 30                                 |

Table 9: Maximum segment current for 1-, 2-, or 3-digit displays

| Mada                 | Register Data |    |    |    |    |    |    |    |

|----------------------|---------------|----|----|----|----|----|----|----|

| Mode                 | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Normal Operation     | Χ             | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | 0  |

| Display Test<br>Mode | X             | Χ  | Χ  | Х  | Х  | Х  | Х  | 1  |

Table 10: Display-test register format (address (hex) = 0xXF)

**Note:** The AS1105 remains in display-test mode until the display-test register is reconfigured for normal operation.

### No-Op Register (Cascading of AS1105)

The no-operation register 00h is used when AS1105s are cascaded in order to support more than 4 digit displays. The cascading must be done in a way that all DOUT are connected to DIN of the following AS1105. The LOAD and CLK signals are connected to all devices. For a write operation for example to the fifth device the command must be followed by four no-operation commands.

Revision 1.32 Oct 2004 Page 7 of 12

When the LOAD signal finally goes to high all shift registers are latched. The first four devices have got no-operation commands and only the fifth device sees the intended command and updates its register.

#### Reset and external Clock Register<sup>3</sup>

This register is addressed via the serial interface. It allows to switch the device to external clock mode (If D0=1 the CLK pin of the serial interface operates as system clock input.) and to apply an external reset (D1). This brings all registers (except reg. E) to default state. For standard operation the register contents should be "00h".

|                   | Address    | Register Data |    |    |    |    |    |     |    |

|-------------------|------------|---------------|----|----|----|----|----|-----|----|

| Mode              | code (hex) | D7            | D6 | D5 | D4 | D3 | D2 | D1  | D0 |

| Normal Operation, | 0xXE       | Х             | χ  | Х  | Х  | Х  | χ  | 0   | 0  |

| internal clock    | UXXL       | ^             | ^  | ^  | ^  | ^  | ^  | U   | 0  |

| Normal Operation, | 0xXE       | Χ             | Х  | X  | Χ  | Χ  | Χ  | 0   | 1  |

| external clock    | UXXL       |               |    |    |    |    |    |     |    |

| Reset state,      | 0xXE       | χ             | χ  | Χ  | Χ  | Χ  | χ  | 1   | 0  |

| internal clock    | UXXL       |               |    | ^  | ^  |    |    | l ' | U  |

| Reset state,      | 0xXE       | Χ             | x  | Х  | Х  | χ  | x  | 1   | 1  |

| external clock    | UXXL       | ^             | ^  | ^  | ^  | ^  | ^  | '   | 1  |

Table 11: Reset and external Clock register (address (hex) = 0xXE)

| I <sub>SEG</sub> (mA) | V <sub>LED</sub> (V) |      |      |      |      |  |  |  |

|-----------------------|----------------------|------|------|------|------|--|--|--|

| ISEG (IIIA)           | 1.5                  | 2.0  | 2.5  | 3.0  | 3.5  |  |  |  |

| 40                    | 12.2                 | 11.8 | 11.0 | 10.6 | 9.69 |  |  |  |

| 30                    | 17.8                 | 17.1 | 15.8 | 15.0 | 14.0 |  |  |  |

| 20                    | 29.8                 | 28.0 | 25.9 | 24.5 | 22.6 |  |  |  |

| 10                    | 66.7                 | 63.7 | 59.3 | 55.4 | 51.2 |  |  |  |

Table 12: RSET vs. segment current and LED forward voltage

## **Applications Information**

#### **Supply Bypassing and Wiring**

In order to achieve optimal performance the AS1105 shall be placed very close to the LED display to minimize effects of electromagnetic interference and wiring inductance. Furthermore it is recommended to connect a  $10\mu F$  electrolytic and a  $0.1\mu F$  ceramic capacitor between VDD and GND to avoid power supply ripple. Also, both GNDs must be connected to ground.

#### Selecting $R_{\text{SET}}$ Resistor and Using External Drivers

The current through the segments is controlled via the external resistor  $R_{\text{SET}}.$  Segment current is about 100 times the current in  $I_{\text{SET}}.$  The right values for  $I_{\text{SET}}$  are given in table 12. The maximum current the AS1105 can drive is 40mA. If higher currents are needed, external drivers must be used. In that case it is no longer necessary that the AS1105 drives high currents. A recommended value for  $R_{\text{SET}}$  is  $47k\Omega.$  In cases that the AS1105 only drives few digits table 9 specifies the maximum currents and  $R_{\text{SET}}$  must be set accordingly. Refer to absolute maximum ratings to calculate acceptable limits for ambient temperature, segment current, and the LED forward-voltage drop.

Revision 1.32 Oct 2004 Page 8 of 12

<sup>&</sup>lt;sup>3</sup> This register is not used by MAX7219, since it does not support software reset and external clocks

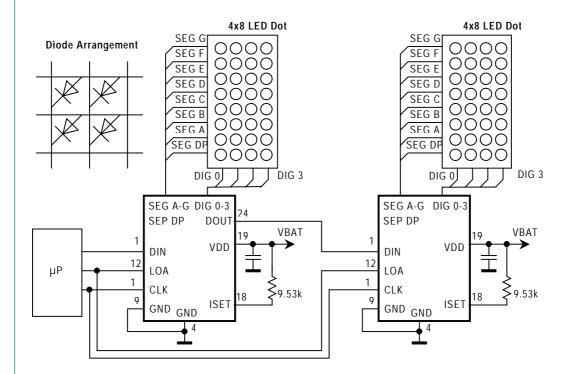

#### 4x8 LED Dot Matrix Driver

The example in Figure 3 uses the AS1105 to drive an 4x8 LED dot matrix. The LED columns have common cathode and are connected to the DIGO-3 outputs. The rows are connected to the segment drivers. Each of the 32 LEDs can be addressed separately. The columns are selected via the digits as shown in Table 2. The decode mode register (0xX9) has to be programmed to '00000000' as stated in Table 4. The single LEDs in a column can be addressed as stated in Table 6, where D0 corresponds to segment G and d/ to segment DP. For a multiple digit dot matrix several AS1105 have to be cascaded.

Figure 3: Application example as LED dot matrix driver

### **Cascading Drivers**

The AS1105 can be cascaded as well. The DOUT pin must be connected to the DIN pin of the following AS1105.

| Package                                                 | Thermal Resistance (0JA) |  |  |  |  |  |

|---------------------------------------------------------|--------------------------|--|--|--|--|--|

| 20 Wide SO                                              | +85°C/W                  |  |  |  |  |  |

| Maximum Junction Temperature (T <sub>J</sub> ) = +150°C |                          |  |  |  |  |  |

| Maximum Ambient Temperature (T <sub>A</sub> ) = +85°C   |                          |  |  |  |  |  |

Table 13: Package thermal resistance data

Revision 1.32 Oct. 2004

#### **Computing Power Dissipation**

The upper limit for power dissipation (PD) for the AS1105 is determined from the following equation:

$PD = (VDD \times 0.5mA) + (VDD - V_{LED})(DUTY \times I_{SEG} \times N)$

where:

VDD = supply voltage

DUTY = duty cycle set by intensity register

N = number of segments driven (worst case is 4)

$V_{LED}$  = LED forward voltage

Iseg = segment current set by Rset

#### Dissipation Example:

$I_{SEG} = 40 \text{mA}, N = 4, DUTY = 31/32, V_{LED} = 1.8 \text{V} \text{ at } 40 \text{mA}, VDD = 5.25 \text{V}$

$PD = 5.25V(0.5mA) + (5.25V - 1.8V)(31/32 \times 40mA \times 4) = 0.54W$

Thus, for a SO package  $\theta_{JA} = +85^{\circ}$ C/W (from Table 13), the maximum allowed ambient temperature  $T_A$  is given by:

$T_{J,MAX} = T_A + PD x \theta_{JA} = 150 \degree C = T_A + 0.54W x 85 \degree C/W.$

where  $T_A = +104$ °C.

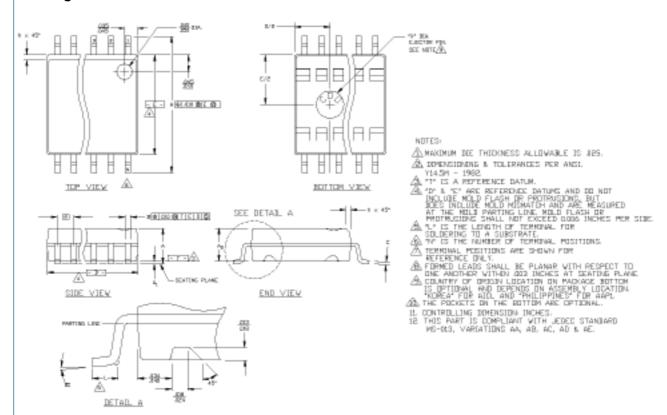

## Package Information

Revision 1.32 Oct. 2004

| 2IHT             | TARL | F | INT  | MILL   | TME: | TEBC |

|------------------|------|---|------|--------|------|------|

| $-1 \square 1.5$ |      | Г | 11.7 | 1911 1 |      |      |

| Ž           |              | COMMON        |              |                             | NOTE  |       | 3     |       | <b>[5]</b> |

|-------------|--------------|---------------|--------------|-----------------------------|-------|-------|-------|-------|------------|

| H<br>A<br>Z | $\mathbf{D}$ | IMENSIO       | ZN           | N <sub>D</sub> TE           | VARI- |       | D     |       | N          |

|             | MIN.         | NOM.          | MAX.         | <sup>-</sup> Τ <sub>Ε</sub> |       | MIN.  | N□M.  | MAX.  |            |

| Α           | 2.46         | 2.56          | 2.64         |                             | AA    | 10.21 | 10.34 | 10.46 | 16         |

| $A_1$       | 0.127        | 0.22          | 0.29         |                             | AB    | 11.46 | 11.58 | 11.71 | 18         |

| Αz          |              | 2.34          | 2.39         |                             | ÄC    | 12.70 | 12.83 | 12.95 | 20         |

| B           | 0.35         | 0.41          | 0.48         |                             | AD    | 15.29 | 15.42 | 15.54 | 24         |

| C           | 0.23         | 0.25          | 0.32         |                             | ΑE    | 17.81 | 17.93 | 18.06 | 28         |

| $\square$   | SEE          |               | <u> DNS</u>  | 3                           |       |       |       |       |            |

| LE          | 7.42         | 7.52          | 7.59         |                             |       |       |       |       |            |

| 6           |              | 1.27 BSC      |              |                             |       |       |       |       |            |

| Щ           | 10.16        | <u> 10.31</u> | 10.41        |                             |       |       |       |       |            |

| h           | 0.25         | 0.33          | <u> 0.41</u> |                             |       |       |       |       |            |

|             | 0.61         | 0.81          | 1.02         |                             |       |       |       |       |            |

| N           | SEE          |               |              | 5                           |       |       |       |       |            |

| Œ           | 0°           | <b>°</b>      | 8°           |                             |       |       |       |       |            |

| Х           | 2.16         | 2.36          | 2.54         |                             |       |       |       |       |            |

Figure 4: SOIC-20 package dimensions

Figure 5: Segment driver capability

Revision 1.32 Oct 2004

Figure 6: Segment Current versa R<sub>SET</sub>

## **Ordering Information**

| Part       | Temp Range    | Pin<br>Package | Delivery<br>Form |

|------------|---------------|----------------|------------------|

| AS1105WL   | 0°C to +70°C  | 24 Wide SO     | Tubes            |

| AS1105WE4  | -40°C to +85° | 24 Wide SO     |                  |

| AS1105WL-T | 0°C to +70°C  | 24 Wide SO     | T&R              |

### Contact

austriamicrosystems AG A 8141 Schloss Premstätten, Austria T. +43 (0) 3136 500 0 F. +43 (0) 3136 525 01 info@austriamicrosystems.com

## Copyright

Copyright © 2004 austriamicrosystems. Trademarks registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. To the best of its knowledge, austriamicrosystems asserts that the information contained in this publication is accurate and correct.

Austriamicrosystems reserves the right to change the circuitry and specifications without notice at any time.

Revision 1 32 Oct 2004 Page 12 of 12

<sup>&</sup>lt;sup>4</sup> Contact factory for availability