# THCV233 and THCV234 Main-Link

V-by-One®HS High-speed video data transmitter and receiver with bi-directional transceiver

#### 1. General Description

THCV233 and THCV234 are V-by-One® HS High-speed video data transmitter/receiver with bi-directional transceiver. They convey not only video data (Main-Link), but also bi-directional system control data (Sub-Link) that is driven by 2-wire serial interface. HOST CPU-side of Sub-Link is selectable on each device and the other side of Sub-Link\* integrates I/O expander.

THCV233-234 system is able to watch and control peripheral devices via 2-wire serial interface or GPIOs. They also can report interrupt events caused by change of GPIO inputs and internal statuses.

#### 2. Features

- LVDS Input internal termination

- CORE 1.8V, LVDS 3.3V

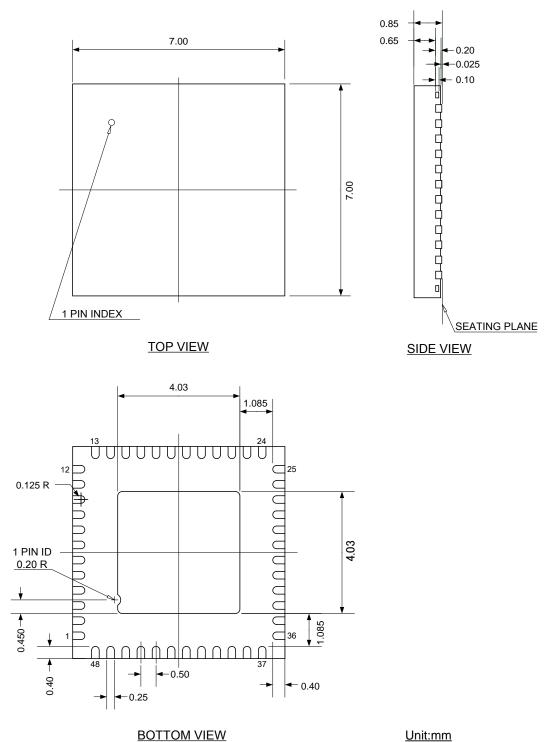

- Package: 48 pin QFN

- **EU RoHS Compliant**

- Main-Link

- Data width selectable: 24/32 bit

- Single/Dual Link selectable

- AC coupling

- Wide frequency range

- CDR requires no external freq. reference

- Supports Spread Spectrum Clocking: Up to 30kHz/±0.5% (center spread)

Concerning Sub-Link and GPIO detail specification, please refer to "THCV233-THCV234\_Sub-Link".

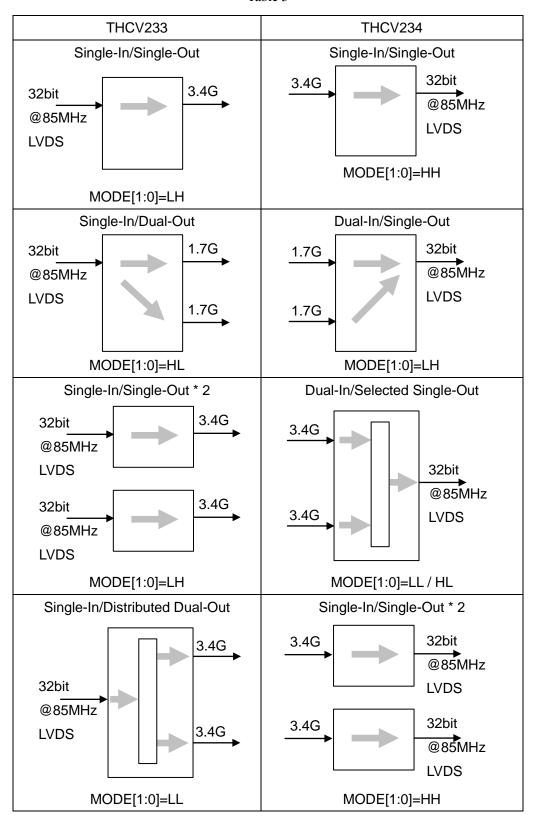

Si/So:Single-in/Single-out, Si/Do:Single-in/Dual-out Si/DDo:Single-in/Distributed Dual-out Di/So:Dual-in/Single-out, Di/SSo:Dual-in/Selected Single-out

#### LVDS Clock Freq. Product TMP VDL Width Link 9MHz to 100MHz Si/So Si/DDo 20MHz to 100MHz Si/Do 40MHz to 100MHz 0°C~ 70°C Si/So 9MHz to 85MHz Si/DDo 20MHz to 85MHz 32bit Si/Do 40MHz to 85MHz 1.62V 1.98V Si/So 9MHz to 100MHz Si/DDo 20MHz to 100MHz Si/Do 40MHz to 100MHz THCV233 Si/So 9MHz to 75MHz Si/DDo 20MHz to 75MHz 32hit 40MHz to 75MHz Si/Do 40°C~ 105°C 9MHz to 100MHz Si/So Si/DDo 20MHz to 100MHz 24bit Si/Do 40MHz to 100MHz 1 7V~ 1.98V Si/So 9MHz to 81MHz 32bit Si/DDo 20MHz to 81MHz 40MHz to 81MHz Si/Do 9MHz to 100MHz Si/So Di/SSo 20MHz to 100MHz Di/So 40MHz to 100MHz 0°C~ 1.62V 70°C 1.98V 9MHz to 85MHz Di/SSo 20MHz to 85MHz Di/So 40MHz to 85MHz THCV234 9MHz to 95MHz Si/So 24bit Si/DDo 20MHz to 95MHz Si/Do 40MHz to 95MHz -40°C~ 1.7V~ 105°C 1 98V Si/So 9MHz to 71.25MHz Si/DDo 20MHz to 71.25MHz Si/Do 40MHz to 71.25MHz

#### Table 1

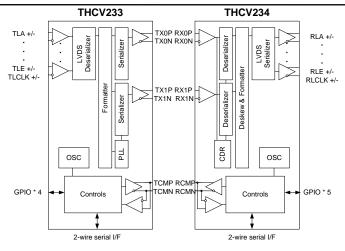

#### 3.Block Diagram

Figure 1

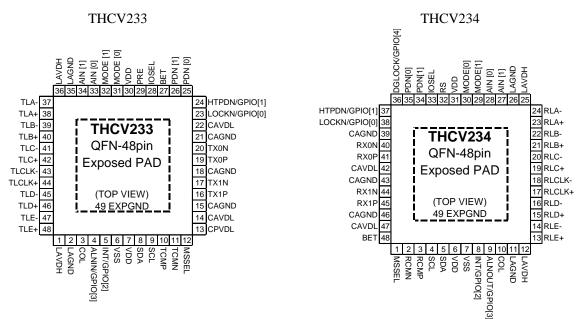

### 4. Pin Configuration

Figure 2

### 5. Pin Description

### Table 2 THCV233 Pin Description

| Pin Name      | Pin#  | Type* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLA -/+       | 37,38 | LÍ    | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TLB -/+       | 39,40 | LI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TLC -/+       | 41,42 | LI    | LVDC simplifying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TLCLK -/+     | 43,44 | LI    | LVDS signal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TLD -/+       | 45,46 | LI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TLE -/+       | 47,48 | LI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TX0N/P        | 20,19 | CO    | High-speed CML signal output (Main-Link).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX1N/P        | 17,16 | CO    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LOCKN/GPIO[0] | 23    |       | Lock detect input (LOCKN) or GPIO[0].  When IOSEL=L, used as LOCKN, it must be connected to Rx LOCKN with a Tx side 10kΩ pull-up resistor. LOCKN is input only.  When IOSEL=H without any register setting, used as GPIO[0] input, no external component is required.  When IOSEL=H and used as GPIO[0] output, it must be connected with a pull-up resistor to 3.3V as an open-drain output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HTPDN/GPIO[1] | 24    | во    | Hot plug detect input (HTPDN) or GPIO[1].  When IOSEL=L, used as HTPDN, it must be connected to Rx HTPDN with a Tx side 10kΩ pull-up resistor. HTPDN is input only.  When IOSEL=H without any register setting, used as GPIO[1] input, no external component is required.  When IOSEL=H and used as GPIO[1] output, it must be connected with a pull-up resistor to 3.3V as an open-drain output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TCMN/P        | 11,10 | СВ    | CML bi-directional input/output (Sub-Link). When PDN[1]=L, Sub-Link power down, it can be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| int/gpi0[2]   | 5     |       | Interrupt signal output for Sub-Link (INT) or GPIO[2].  When MSSEL=L, used as INT output, it must be connected with a pull-up resistor to 3.3V.  INT can monitor changes of GPIO input pins and internal statuses and reports event set by register (default: no monitor).  H: Steady state, L: Interrupt occured  When MSSEL=H without any register setting, used as GPIO[2] input, no external component is required.  When used as GPIO[2] open-drain output, it must be connected with a pull-up resistor to 3.3V.  When used as GPIO[2] input or push pull output, no external component is required.                                                                                                                                                                                                                                                                                                              |

| ALNIN/GPIO[3] | 4     | В     | Data alignment enable input for LVDS data sets (ALNIN) or GPIO[3]. ALNIN is default without any register setting.  ALNIN is external DE input pin. When input LVDS does not contain DE signal, DE can be provided as external input.  Activation of ALNIN function follow the following settings.  When PDN[1:0]=LH, Main-Link Only Active,SCL pin is worked as "choice of DE input" selector; therefore, SCL=L activates ALNIN.  H: DE input from LVDS is used for processing, L: DE input from ALNIN is used for processing  When PDN[1:0]=HH, Main-Link and Sub-Link active,register setting determines whether ALNIN is activated and its polarity.  When used as ALNIN, no external component is required. ALNIN is input only.  When used as GPIO[3] open-drain output, it must be connected with a pull-up resistor to 3.3V.  When used as GPIO[3] input or push pull output, no external component is required. |

| SDA           | 8     |       | Data Schmitt input/output for 2-wire serial interface.  When PDN[1]=H, Sub-Link active, it must be connected with a pull-up resistor to 3.3V.  When PDN[1:0]=LH, Main-Link Only Active, it must be connected with a pull-up resistor to 3.3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCL           | 9     |       | Clock Schmitt input/output for 2-wire serial interface.  When PDN[1]=H, Sub-Link active, it must be connected with a pull-up resistor to 3.3V.  When PDN[1:0]=LH, Main-Link Only Active, SCL pin is worked as "choise of DE input" selector.  H: DE input from LVDS is used for processing, L: DE input from ALNIN is used for processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

<sup>\*</sup>Type symbol

=3.3V CMOS input, B= CMOS Bi-directional buffer, BO= OpenDrain CMOS Bi-directional buffer L⊨LVDS input, CO=CML output, CB=CML Bi-directional buffer

P33=Power 3.3V, P18=Power 1.8V, GND=GND

### THCV233 Pin Description (Continued)

| Pin Name   | Pin#  | Type* | Description                                                                                                                                                                                                                                                                                     |

|------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSSEL      | 12    | I     | Master-side/Slave-side selector for Sub-Link and 2-wire serial interface. H: Sub-Link Slave side (inside 2-wire serial VF is master), L: Sub-Link Master side (inside 2-wire serial VF is slave) Sub-Link Master is connected to HOST MPU. Forbid the same setting between THCV233 and THCV234. |

| AIN [1:0]  | 34,33 | I     | Address setting for 2-wire serial interface.  When using 2-wire serial interface, it must be set the same value as THCV234's one.  AIN[1:0] = LL : 7'b001011  = LH : 7'b1110100  = HL : 7'b1110111  = HH : Reserved (Forbidden)                                                                 |

| MODE [1:0] | 32,31 | I     | Operation mode select input for Main-Link.  MODE[1:0] =LL : Single-in/Distribution dual-out =LH : Single-in/Single-out =HL : Single-in/Dual-out =HH : Reserved (Forbidden)                                                                                                                      |

| IOSEL      | 28    | I     | HTPDN, LOCKN pin enable input for Main-Link. H: HTPDN, LOCKN pin disable (GPIO[1:0] enable), L: HTPDN, LOCKN pin enable (GPIO[1:0] disable) When IOSEL inputs H, HTPDN and LOCKN state in THCV234 are brought by Sub-Link.                                                                      |

| PDN [1:0]  | 26,25 | I     | Power down Schmitt input.  PDN[1]: For Sub-Link power down control (2-wire serial interface + Sub-Link)  H: Normal operation, L: Power down  PDN[0]: For Main-Link power down control (LVDS-Rx + Main-Link)  H: Normal operation, L: Power down                                                 |

| PRE        | 29    | I     | Pre-Emphasis level select input for Main-Link.<br>H : 100%, L : 0%                                                                                                                                                                                                                              |

| COL        | 3     | I     | Data width setting for Main-Link.<br>H : 24bit, L : 32bit                                                                                                                                                                                                                                       |

| вет        | 27    | I     | Field-BET entry.  H : Field BET Operation, L : Normal Operation                                                                                                                                                                                                                                 |

| LAVDH      | 1,36  | P33   | LVDS power supply (3.3V)                                                                                                                                                                                                                                                                        |

| LAGND      | ,     |       | LVDS GND                                                                                                                                                                                                                                                                                        |

| CAVDL      | ,     |       | High-speed signal analog power supply (1.8V)                                                                                                                                                                                                                                                    |

| CAGND      |       |       | High-speed signal analog GND                                                                                                                                                                                                                                                                    |

| CPVDL      |       |       | High-speed signal PLL power supply (1.8V)                                                                                                                                                                                                                                                       |

| VDD        | ,     |       | Logic power supply (1.8V)                                                                                                                                                                                                                                                                       |

| VSS        | 6     |       | Logic GND                                                                                                                                                                                                                                                                                       |

| EXPGND     | 49    | GND   | EXPOSED PAD GND                                                                                                                                                                                                                                                                                 |

\*Type symbol

=3.3V CMOS input, B= CMOS Bi-directional buffer, BO= OpenDrain CMOS Bi-directional buffer

LI=LVDS input, CO=CML output, CB=CML Bi-directional buffer

P33=Power 3.3V, P18=Power 1.8V, GND=GND

### Table 3 THCV234 Pin Description

| Pin Name       | Pin#  | Type* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

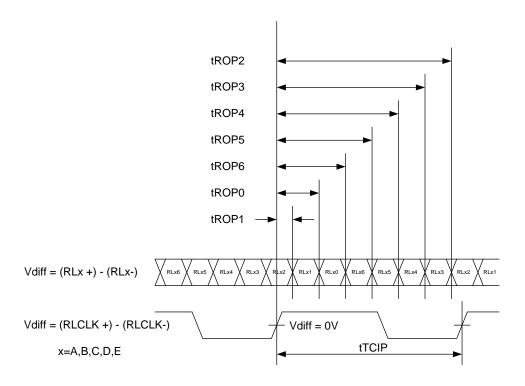

| RLA -/+        | 24,23 | LO    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RLB -/+        | 22.21 | LO    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RLC -/+        | 20,19 | LO    | LDD simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RLCLK -/+      | 18,17 | LO    | LVDS signal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RLD -/+        | 16,15 | LO    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RLE -/+        | 14,13 | LO    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RX0N/P         | 40,41 | CI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RX1N/P         | 44,45 | CI    | High-speed CML signal input (Main-Link).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LOCKN/GPIO[0]  | 38    | во    | Lock detect output (LOCKN) or GPIO[0].  When IOSEL=L, used as LOCKN, it must be connected to Tx LOCKN with a Tx side10kΩ pull-up resistor. LOCKN is output only.  When IOSEL=H without any register setting, used as GPIO[0] input, no external component is required.  When IOSEL=H and used as GPIO[0] output, it must be connected with a pull-up resistor to 3.3V as an open-drain output pin.                                                                                                                                                                                                          |

| HTPDN/GPIO[1]  | 37    | во    | Hot plug detect output (HTPDN) or GPI0[1].  When IOSEL=L, used as HTPDN, it must be connected to Tx HTPDN with a Tx side 10kΩ pull-up resistor. HTPDN is output only.  When IOSEL=H without any register setting, used as GPI0[1] input, no external component is required.  When IOSEL=H and used as GPI0[1] output, it must be connected with a pull-up resistor to 3.3V as an open-drain output pin.                                                                                                                                                                                                     |

| RCMN/P         | 2,3   | СВ    | CML bi-directional input/output (Sub-Link). When PDN[1]=L, Sub-Link power down, it can be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INT/GPIO[2]    | 8     |       | Interrupt signal output for Sub-Link (INT) or GPIO[2].  When MSSEL=L, used as INT output, it must be connected with a pull-up resistor to 3.3V.  INT can monitor changes of GPIO input pins and internal statuses and reports event set by register (default : no monitor).  H: Steady state, L: Interrupt occured  When MSSEL=H without any register setting, used as GPIO[2] input, no external component is required.  When used as GPIO[2] open-drain output, it must be connected with a pull-up resistor to 3.3V.  When used as GPIO[2] input or push pull output, no external component is required. |

| ALNOUT/GPIO[3] | 9     | В     | Data alignment enable output (ALNOUT) for LVDS data sets or GPIO[3]. ALNOUT is default without any register setting.  When used as ALNOUT, no external component is required. It is push pull output.  ALNOUT output DE timing depending upon data stream state. ALNOUT is output only.  When used as GPIO[3] open-drain output, it must be connected with a pull-up resistor to 3.3V.  When used as GPIO[3] input or push pull output, no external component is required.  Bit Error Test (BET) result output under Field-BET operation  H: No error, L: Bit error occured                                 |

| DGLOCK/GPIO[4] | 36    | BPU   | Multiple-chip configuration total Rx side LOCKN indicator (DGLOCK) or GPIO[4]. DGLOCK is default without any register setting.  When used as DGLOCK, it is internally connected with a pull-up resistor to 3.3V. No external component is required.  LOCKN arrange among Rx Multiple-chip configuration is achieved by connecting all DGLOCK pins.  When used as GPIO[4] output, which is open-drain output only. It must be connected with a pull-up resistor to 3.3V.  When used as GPIO[4] input, no external component is required.                                                                     |

| SDA            | 5     |       | Data Schmitt input/output for 2-wire serial interface.  When PDN[1]=H, Sub-Link active, it must be connected with a pull-up resistor to 3.3V.  When PDN[1]=L, Sub-Link power down, it can be directly connected to GND.                                                                                                                                                                                                                                                                                                                                                                                     |

| SCL            | 4     |       | Clock Schmitt input/output for 2-wire serial interface.  When PDN[1]=H, Sub-Link active, it must be connected with a pull-up resistor to 3.3V.  When PDN[1]=L, Sub-Link power down, it can be directly connected to GND.                                                                                                                                                                                                                                                                                                                                                                                    |

\*Type symbol

l=3.3V CMOS input, B= CMOS Bi-directional buffer, BO= OpenDrain CMOS Bi-directional buffer

BPU = CMOS Bi-directional buffer with an on-chip pullup resistor

LO=LVDS output, CO=CML output, CB=CML Bi-directional buffer

P33=Power 3.3V, P18=Power 1.8V, GND=GND

### THCV234 Pin Description (Continued)

| Pin Name     | Pin#   | Type* | Description (Continued)                                                                                                                                                                                                                                                                         |

|--------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSSEL        | 1      | I     | Master-side/Slave-side selector for Sub-Link and 2-wire serial interface. H: Sub-Link Slave side (inside 2-wire serial VF is master), L: Sub-Link Master side (inside 2-wire serial VF is slave) Sub-Link Master is connected to HOST MPU. Forbid the same setting between THCV233 and THCV234. |

| AIN [1:0]    | 27,28  | I     | Address setting for 2-wire serial interface.  When used 2-wire serial interface, it must be set the same value as THCV233's one.  AIN[1:0] = LL : 7'b001011  = LH : 7'b0110100  = HL : 7'b1110111  = HH : Reserved (Forbidden)                                                                  |

| MODE [1:0]   | 29,30  | I     | Operation mode select input for Main-Link.  MODE [1:0] =LL: Dual-in/Selected single-out (Lane0)  =LH: Dual-in/Single-out  =HL: Dual-in/Selected single-out (Lane1)  =HH: Single-in/Single-out                                                                                                   |

| IOSEL        | 33     | I     | HTPDN, LOCKN pin enable output for Main-Link.<br>H: HTPDN, LOCKN pin disable (GPIO[1:0] enable), L: HTPDN, LOCKN pin enable (GPIO[1:0] disable)<br>When IOSEL inputs H, HTPDN and LOCKN state in THCV234 are brought by Sub-Link.                                                               |

| PDN [1:0]    | 34,35  | Į     | Power down Schmitt input.  PDN[1]: For Sub-Link power down control (2-wire serial interface + Sub-Link)  H: Normal operation, L: Power down  PDN[0]: For Main-Link power down control (LVDS-Rx + Main-Link)  H: Normal operation, L: Power down                                                 |

| RS           | 32     | I     | LVDS output swing range select input. H: Normal swing (350mv@typ.), L: Reduced swing (200mv@typ.) Latch select input under Field-BET operation H: Latched result, L: NOT Latched result                                                                                                         |

| COL          | 10     | I     | Data width setting for Main-Link.<br>H : 24bit, L : 32bit                                                                                                                                                                                                                                       |

| ВЕТ          | 48     | I     | Field-BET entry. H : Field BET Operation, L : Normal Operation                                                                                                                                                                                                                                  |

| LAVDH        |        | P33   | LVDS power supply (3.3V)                                                                                                                                                                                                                                                                        |

| LAGND        | 11,26  | GND   | LVDS GND                                                                                                                                                                                                                                                                                        |

| CAVDL        |        |       | High-speed signal analog power supply (1.8V)                                                                                                                                                                                                                                                    |

| CAGND        | , -, - |       | High-speed signal analog GND                                                                                                                                                                                                                                                                    |

| VDD          | 6,31   |       | Logic power supply (1.8V)                                                                                                                                                                                                                                                                       |

| VSS          | 7      | _     | Logic GND                                                                                                                                                                                                                                                                                       |

| *Type symbol | 49     | GND   | Exposed PAD GND                                                                                                                                                                                                                                                                                 |

\*Type symbol I=3.3V CMOS input, B= CMOS Bi-directional buffer, BO= OpenDrain CMOS Bi-directional buffer

BPU = CMOS Bi-directional buffer with an on-chip pullup resistor

LO=LVDS output, CO=CML output, CB=CML Bi-directional buffer

P33=Power 3.3V, P18=Power 1.8V, GND=GND

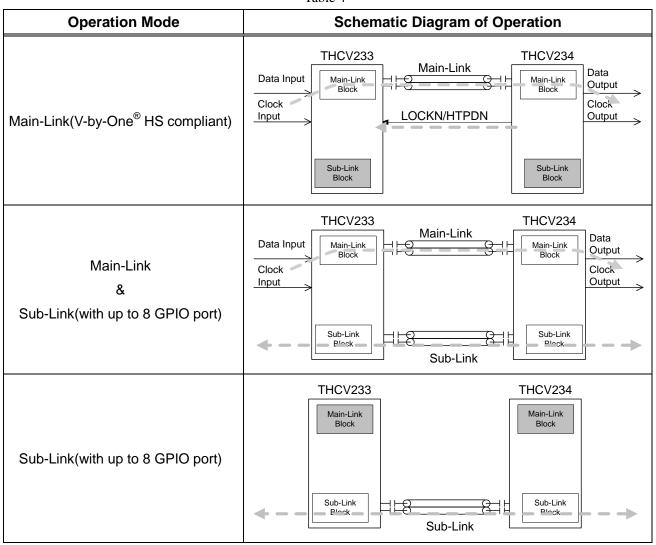

### 6. General Operation Mode

Table 4

### 7. Main-Link Operation Mode

Table 5

#### **8. Function Description**

**Functional Overview**

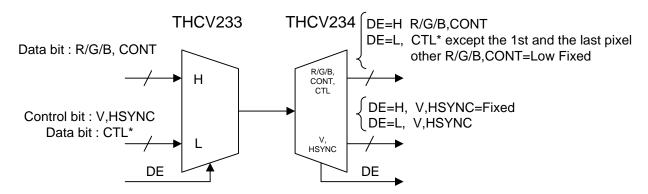

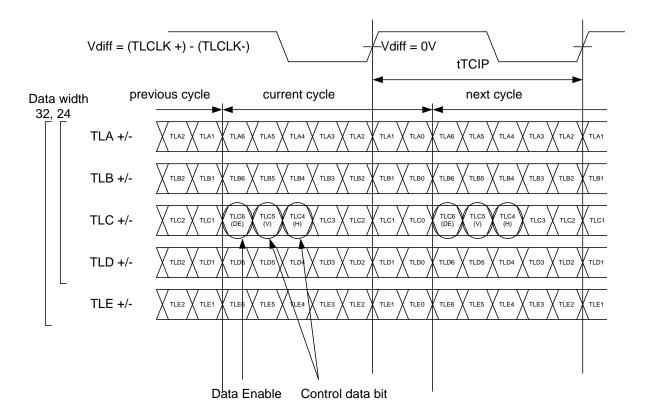

With High Speed CML SerDes, proprietary encoding scheme and CDR (Clock and Data Recovery) architecture, THCV233 and THCV234 enable transmission of 24/32bit video data, 2bit control data and Data Enable (DE) through Main-Link by single/dual differential pair cable with minimal external components. In addition, THCV233 and THCV234 has Sub-Link which enables bi-directional transmission of 2-wire interface signals, GPIO signals and also HTPDN/LOCKN signals for Main-Link through the other 1-pair of CML-Line. It does not need any external frequency reference, such as a crystal oscillator.

THCV233, transmitter of Main-Link, inputs LVDS data (including video data, control data and DE) and serializes video data and control data separately, depending on polarity of DE. DE is a signal which indicates whether video or control data are active. When DE is high, it serializes video data inputs into CML data streams. And it transmits serialized control data when DE is low. Instead of DE in the LVDS format, THCV233 has ALNIN LVCMOS-input pin, which enables to transfer LVDS input data with external DE input via ALNIN.

THCV234, receiver of Main-Link, automatically extracts clock from the incoming data streams and converts high-speed serial data into video data with DE being high or control data with DE being low, recognizing which type of serial data is being sent by transmitter. And it outputs the recovered data in the form of LVDS data. THCV234 has ALNOUT output pin which transmits DE signal in LVCMOS. THCV234 can seamlessly operate for a wide range of a serial bit rate from 270Mbps to 3.4Gbps/lane.

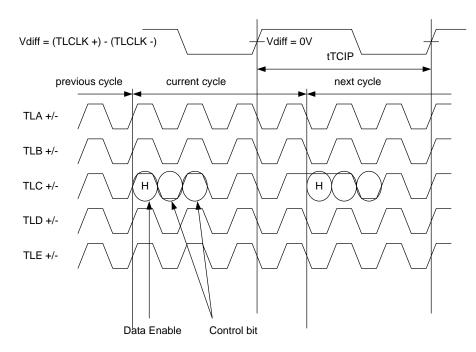

#### Data Enable Requirement (DE)

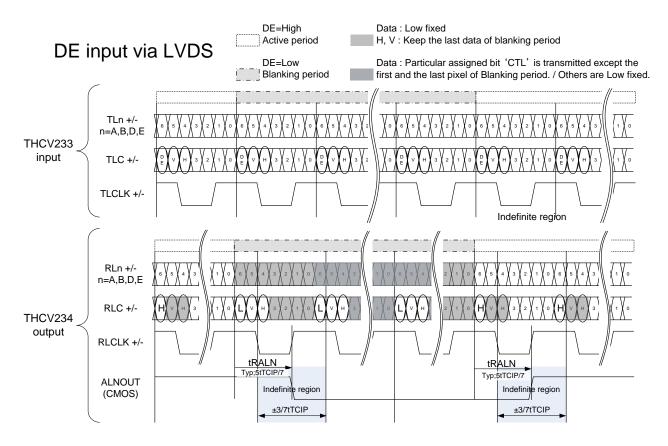

There are some requirements for DE signal as described in Figure 3, Figure 4 Figure 14 and Table 31.

If DE=Low, control data of same cycle and particular assigned data bit 'CTL' except the first and the last pixel are transmitted. Otherwise video data are transmitted during DE=High.

Control data from receiver in DE=High period are previous data of DE transition. See Figure 4.

The length of DE being low and high is at least 2 clock cycles long, as described in Figure 14 and Table 31.

Data Enable must be toggled like High -> Low -> High at regular interval.

\*CTL are particular assigned bit among R/G/B, CONT that can carry arbitrary data during DE=Low period.

Figure 3 Conceptual diagram of the basic operation of the chipset

Figure 4 Data bit and control bit transmission when DE is from LVDS (default)

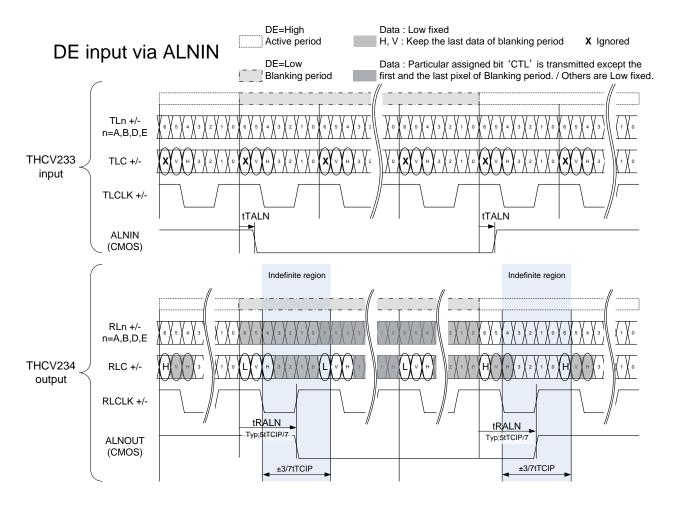

Data alignment indicator input of THCV233 (ALNIN)

ALNIN is external DE input. When input LVDS does not contain DE signal, DE can be provided via ALNIN. Activation setting of ALNIN function is described in the following "Data Enable Select of THCV233".

Data alignment indicator output of THCV234 (ALNOUT)

ALNOUT output DE timing depending upon data stream state.

#### Data Enable Select of THCV233

Depending on pin or register setting THCV233 can deal with several DE alternatives.

When PDN[1:0]=LH, SCL pin is worked as "choice of DE input" selector.

H:DE input from LVDS is used for processing, L:DE input from ALNIN is used for processing When PDN[1:0]=HH, register setting determines the following. Default "From LVDS, normal polarity, TLC[6]" See register mapping. When DE input bit is from TLC[5] or TLC[4], operation follows Figure 4.

Whether DE input from LVDS or from ALNIN is used for processing

DE input polarity

Whether DE input from LVDS used for processing is TLC[6] or TLC[5] or TLC[4]

Figure 5 indicate ALNIN operation. User must take care of data indefinite region and had better ignore them.

Figure 5 Data bit and control bit transmission when DE is from ALNIN

HTPDN, LOCKN transmission route setting (IOSEL)

IOSEL determine the HTPDN/LOCKN signal transmission route.

If HTPDN and LOCKN are transmitted by Sub-Link, remained pins become GPIO.

Table 6 HTPDN/LOCKN Transmission Route Setting

| IOSEL | HTPDN/LOCKN                                          |

|-------|------------------------------------------------------|

| L     | HTPDN/LOCKN are transmitted via external DC signal.  |

| Н     | HTPDN/LOCKN are transmitted via Sub-Link.            |

|       | Remained pins become GPIO, driven via 2-wire serial. |

Please refer to "THCV233-THCV234 Sub-Link" data sheet about Sub-Link and GPIO.

Power Down (PDN[1:0])

PDN[1:0] turn off internal circuitry of Main-Link and Sub-Link separately.

Table 7 Power Down Setting

| PDN[1:0] | Operation                              |

|----------|----------------------------------------|

| LL       | Both Main-Link and Sub-Link power down |

| LH       | Only Main-Link is active               |

| HL       | Only Sub-Link is active                |

| HH       | Both Main-Link and Sub-Link active     |

Please refer to "THCV233-THCV234\_Sub-Link" data sheet about Sub-Link and GPIO.

Color depth or data width setting function for Main-Link (COL)

COL pin enables to select data width for Main-Link. E-ch. (TLE-/+ and RLE-/+) is disable with COL=H.

Table 8 Data Width Setting Function

| С | OL | Mode Function    |

|---|----|------------------|

|   | L  | 32bit-Data width |

|   | Н  | 24bit-Data width |

Operation mode function of THCV233 (MODE[1:0])

MODE[1:0] pins select data transfer mode of THCV233 as Table 2.

Table 9 Operation Mode Setting Function for THCV233

| MODE[1:0] | Operation mode                    |

|-----------|-----------------------------------|

| LL        | Single-in / Distribution Dual-out |

| LH        | Single-in / Single-out            |

| HL        | Single-in / Dual-out              |

| HH        | Reserved (forbidden)              |

Operation mode function of THCV234 (MODE[1:0])

MODE[1:0] pins select data transfer mode of THCV234 as Table 2.

Table 10 Operation Mode Setting Function for THCV234

| MODE[1:0] | Operation mode                         |

|-----------|----------------------------------------|

| LL        | Dual-in / Selected single-out (Lane 0) |

| LH        | Dual-in / Single-out                   |

| HL        | Dual-in / Selected single-out (Lane 1) |

| HH        | Single-in /Single-out                  |

2-wire serial interface master/slave setting (MSSEL)

MSSEL selects Master / Slave side of Sub-Link and 2-wire serial interface in the devices. THCV233 and THCV234 should be with different setting.

Table 11 Master / Slave Setting

| MSSEL | Sub-Link Master / Slave (2-wire serial master / slave) |

|-------|--------------------------------------------------------|

| L     | Sub-Link Master side (2-wire serial slave)             |

| Н     | Sub-Link Slave side (2-wire serial master)             |

Please refer to "THCV233-THCV234 Sub-Link" data sheet about Sub-Link and GPIO.

2-wire serial interface interrupt output (INT)

INT outputs interrupt event indicator on Sub-Link Master side of the system.

As default setting, INT does not monitor any event. Being set by 2-wire serial interface, THCV233 and THCV234 can monitor any changes of GPIO input pins and internal statuses as an interrupt.

Table 12 Interrupt output

| INT | State              |

|-----|--------------------|

| L   | Interrupt occurred |

| Н   | Steady state       |

Please refer to "THCV233-THCV234 Sub-Link" data sheet about Sub-Link and GPIO.

2-wire serial interface address setting (AIN[1:0])

AIN[1:0] pins determine address setting of THCV233 and THCV234.

Both devices should have the same address setting.

Table 13 2-wire serial interface address setting select

| AIN[1:0] | 2-wire interface address setting |

|----------|----------------------------------|

| LL       | 7'b0001011                       |

| LH       | 7'b0110100                       |

| HL       | 7'b1110111                       |

| HH       | Reserved (forbidden)             |

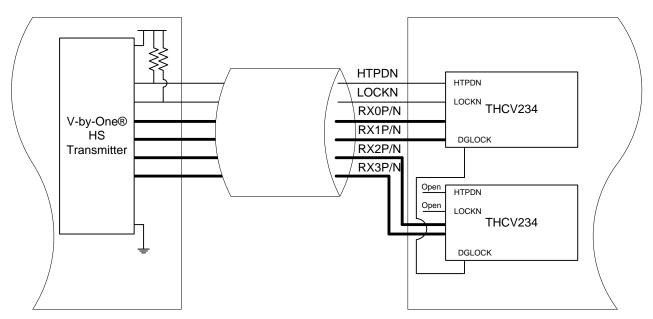

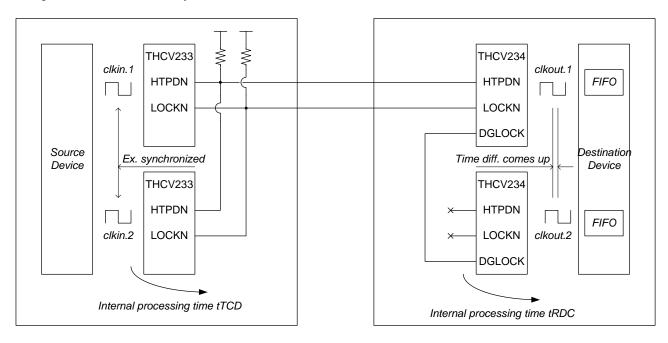

Multiple-chip configuration total Rx side LOCKN indicator (DGLOCK)

In order to reduce the number of cables needed for HTPDN and LOCKN in multiple-Rx chip configuration, THCV234 is equipped with the DGLOCK pin. When all the DGLOCK pins are connected as in Figure 6, the connected Rx chips can share the CDR lock status, making all the Rx chips in the same operation status.

Figure 6 Usage of DGLOCK in multiple-Rx configuration

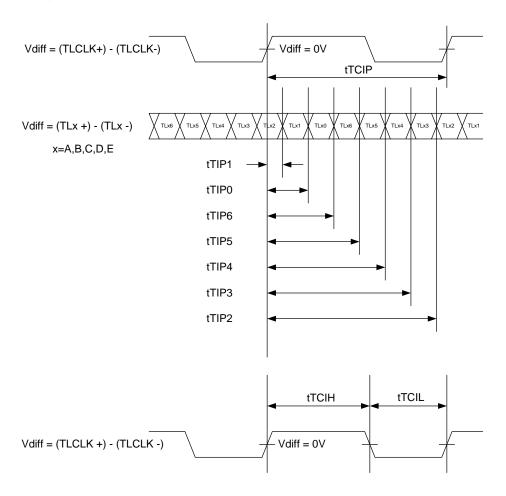

#### LVDS Mapping

LVDS data (video data, control data, DE) are mapped as Figure 7. TLC[6] is special bit for DE(data enable), and TLC[5:4] are for control data bits and the other bits are for video data. Among video data there are special assigned bit 'CTL' are defined for the data transmission under DE=low condition.

The number of LVDS channel depends on color depth mode(COL).

TLD[6] is not available in 24bit Data-width mode.

Figure 7 LVDS Data mapping timing diagram

Table 14 LVDS Color Data Mapping Table

| THCV233 | THCV234 | C        | OL          | Symbol defined by |

|---------|---------|----------|-------------|-------------------|

| Input   | Output  | H (8bit) | L (10bit)   | V-by-One® HS      |

| TLA[0]  | RLA[0]  | R[2]     | R[4]        | D2                |

| TLA[1]  | RLA[1]  | R[3]     | R[5]        | D3                |

| TLA[2]  | RLA[2]  | R[4]     | R[6]        | D4                |

| TLA[3]  | RLA[3]  | R[5]     | R[7]        | D5                |

| TLA[4]  | RLA[4]  | R[6]     | R[8]        | D6                |

| TLA[5]  | RLA[5]  | R[7]     | R[9]        | D7                |

| TLA[6]  | RLA[6]  | G[2]     | G[4]        | D10               |

| TLB[0]  | RLB[0]  | G[3]     | G[5]        | D11               |

| TLB[1]  | RLB[1]  | G[4]     | G[6]        | D12               |

| TLB[2]  | RLB[2]  | G[5]     | G[7]        | D13               |

| TLB[3]  | RLB[3]  | G[6]     | G[8]        | D14               |

| TLB[4]  | RLB[4]  | G[7]     | G[9]        | D15               |

| TLB[5]  | RLB[5]  | B[2]*2   | B[4]*2      | D18               |

| TLB[6]  | RLB[6]  | B[3]*2   | B[5]*2      | D19               |

| TLC[0]  | RLC[0]  | B[4]*2   | B[6]*2      | D20               |

| TLC[1]  | RLC[1]  | B[5]*2   | B[7]*2      | D21               |

| TLC[2]  | RLC[2]  | B[6]*2   | B[8]*2      | D22               |

| TLC[3]  | RLC[3]  | B[7]*2   | B[9]*2      | D23               |

| TLC[4]  | RLC[4]  | HSYNC    | HSYNC       | Hsync             |

| TLC[5]  | RLC[5]  | VSYNC    | VSYNC       | Vsync             |

| TLC[6]  | RLC[6]  | DE       | DE          | DE                |

| TLD[0]  | RLD[0]  | R[0]     | R[2]        | D0                |

| TLD[1]  | RLD[1]  | R[1]     | R[3]        | D1                |

| TLD[2]  | RLD[2]  | G[0]     | G[2]        | D8                |

| TLD[3]  | RLD[3]  | G[1]     | G[3]        | D9                |

| TLD[4]  | RLD[4]  | B[0]*2   | B[2]*2      | D16               |

| TLD[5]  | RLD[5]  | B[1]*2   | B[3]*2      | D17               |

| TLD[6]  | RLD[6]  | N/A*1    | CONT[1]*2*3 | D24*3             |

| TLE[0]  | RLE[0]  |          | R[0]*2      | D30               |

| TLE[1]  | RLE[1]  |          | R[1]*2      | D31               |

| TLE[2]  | RLE[2]  | Channel  | G[0]*2      | D28               |

| TLE[3]  | RLE[3]  | Power    | G[1]*2      | D29               |

| TLE[4]  | RLE[4]  | Down     | B[0]*2      | D26               |

| TLE[5]  | RLE[5]  |          | B[1]*2      | D27               |

| TLE[6]  | RLE[6]  |          | CONT[2]*2*3 | D24*3             |

<sup>\*1</sup> N/A: Not available, THCV234 output RLDn[6]=Low.

<sup>\*2</sup> CTL bits, which are carried during DE=Low except the 1st and the last pixel

<sup>\*3 3</sup>D flags defined in the V-by-One® HS Standard are assigned to the following bit. V-by-One® HS Standard Packer/Unpacker D[24](3DLR) <=> LVDS T/RLE[6] V-by-One® HS Standard Packer/Unpacker D[25](3DEN) <=> LVDS T/RLD[6]

THCV234 LVDS Reduced swing output function (RS) RS controls THCV234 LVDS output swing level.

Table 15 LVDS output swing level

| RS | Output swing                  |

|----|-------------------------------|

| L  | Reduced swing (200mV typical) |

| Н  | Normal swing (350mV typical)  |

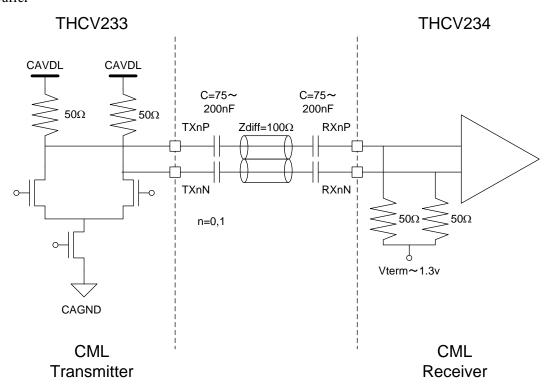

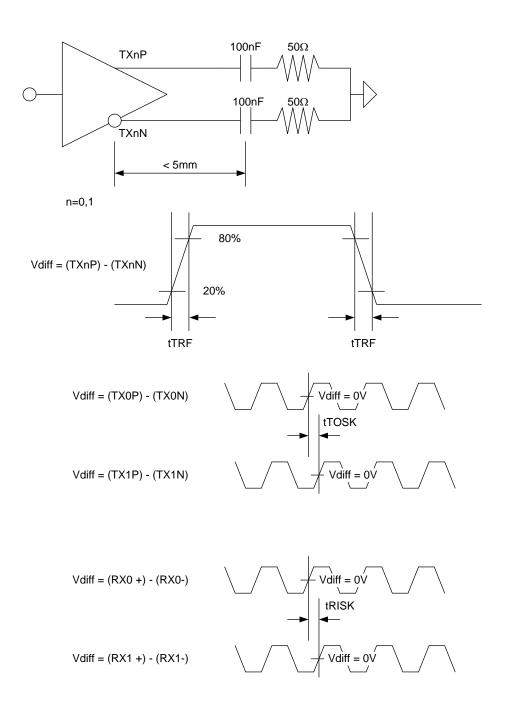

#### CML Buffer

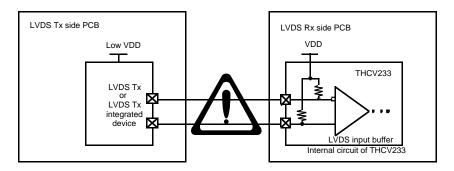

Capacitor on transmitter side is mandatory, while receiver side is optional and recommended.

Figure 8 High-Speed CML Buffer Scheme

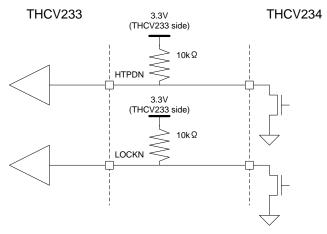

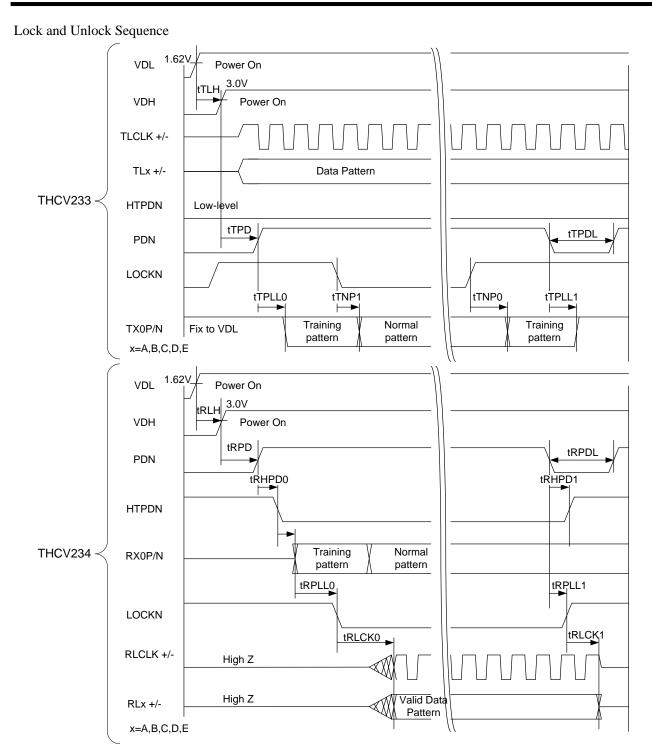

#### Lock detect and Hot-plug function

When IOSEL=L, LOCKN and HTPDN are both open drain outputs from THCV234. Pull-up resistors are needed at THCV233 side to 3.3V. See Figure 9.

If THCV234 is not active (power down mode (PDN[0]=L) or powered off), HTPDN is open. Otherwise, HTPDN is pulled down by THCV234.

HTPDN of THCV233 side is high when THCV234 is not active or the receiver board is not connected. Then THCV233 enters into the power down mode. When HTPDN transits from High to Low, THCV233 starts up and transmits training pattern for link training.

LOCKN indicates whether THCV234 is in the lock state or not. If THCV234 is in the unlock state, LOCKN is open. Otherwise (in the lock state), it's pulled down by THCV234.

THCV233 keeps transmitting training pattern until LOCKN transits to Low. After training done, THCV234 sinks current and LOCKN is Low. Then THCV233 starts transmitting normal video pattern.

When IOSEL=H, equivalent training processes are driven by Sub-Link.

Figure 9 Hot-plug and Lock Detect Scheme

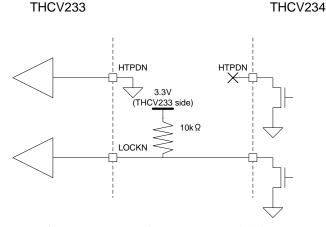

#### No HTPDN connection option

Even when IOSEL=L, HTPDN connection between THCV233 and THCV234 can be omitted as an application option. In this case, HTPDN at the Transmitter side should always be taken as Low. See Figure 10.

Figure 10 HTPDN is not Connected Scheme

#### THCV233 Pre-emphasis function (PRE)

Pre-emphasis can equalize severe signal degradation caused by long distance or high-speed transmission. PRE, select the strength of pre-emphasis.

Table 16 Pre-emphasis function table

| PRE | Description            |

|-----|------------------------|

| L   | without Pre-emphasis   |

| Н   | with 100% Pre-emphasis |

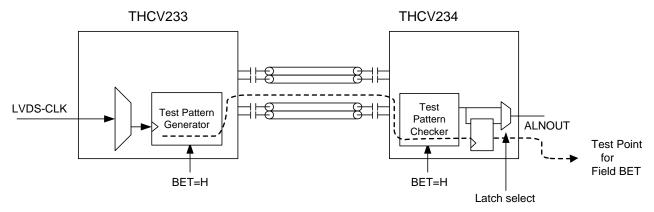

#### Field BET Operation

In order to help users to check validity of high speed serial lines (Main-link), THCV233/THCV234 has an operation mode in which they act as a bit error tester (BET). In this mode, THCV233 internally generates test pattern which is then serialized onto the Main-link. THCV234 receives the data stream and checks bit errors.

This "Field BET" mode is activated by setting BET= H both on THCV233 and THCV234. Pattern Generator CLK is from LVDS-CLK and the pattern is then 8b/10b encoded, scrambled, and serialized onto the Main-link. As for THCV234, the internal test pattern check circuit gets enabled and reports result on ALNOUT pin. The ALNOUT pin goes LOW whenever bit errors occur, or it stays HIGH when there is no bit error. Please refer to Figure 11. User can select 2 kinds of check result, "Latched-result" or "NOT latched result". The latch is reset by setting RS=L.

Table 17 THCV233-234 Field BET operation pin settings

| THCV233 | THC | V234 | Cond                | dition              |

|---------|-----|------|---------------------|---------------------|

| BET     | BET | RS   | Operation           | Output Latch select |

| L       | L   | -    | Normal Operation    | •                   |

| Н       | Н   | L    | FieldBET Operation  | NOT latched result  |

| Н       | Н   | Н    | Tielube i Operation | Latched result      |

Table 18 THCV234 Field BET result

| ALNOUT | Output             |

|--------|--------------------|

| L      | Bit error occurred |

| Н      | No error           |

Figure 11 Field BET Configuration

## 9. Absolute Maximum Ratings\*

Table 19 THCV233 Absolute Maximum Ratings

| Parameter                                         | Symbol | Min. | Тур. | Max.       | Units |

|---------------------------------------------------|--------|------|------|------------|-------|

| 1.8v Supply Voltage (CAVDL,CPVDL,VDD)             | VDL    | -0.3 | -    | +2.1       | V     |

| 3.3v Supply Voltage(LAVDH)                        | VDH    | -0.3 | -    | +4.0       | V     |

| CMOS Input Voltage                                | -      | -0.3 | -    | VDH+0.3    | V     |

| CMOS Bi-directional buffer Input / Output Voltage | -      | -0.3 | -    | 3.6        | V     |

| LVDS Receiver Input Voltage                       | -      | -0.3 | -    | VDH+0.3    | V     |

| CML Transmitter Output Voltage                    | -      | -0.3 | -    | VDL+0.3    | V     |

| CML Bi-directional buffer Input / Output Voltage  | -      | -0.3 | -    | VDL+0.3    | V     |

| Output Current                                    | -      | -50  | -    | 50         | mΑ    |

| Storage Temperature                               | -      | -55  | -    | +125       | °C    |

| Junction Temperature                              | -      | -    | -    | +125       | °C    |

| Reflow Peak Temperature/Time                      | -      | -    | -    | +260/10sec | °C    |

| Maximum Power Dissipation @ +25°C                 | -      | -    | -    | 3.2        | W     |

Table 20 THCV234 Absolute Maximum Ratings

| Parameter                                         | Symbol | Min. | Тур. | Max.       | Units |

|---------------------------------------------------|--------|------|------|------------|-------|

| 1.8v Supply Voltage(CAVDL,VDD)                    | VDL    | -0.3 | -    | +2.1       | V     |

| 3.3v Supply Voltage(LAVDH)                        | VDH    | -0.3 | ı    | +4.0       | V     |

| CMOS Input Voltage                                | -      | -0.3 | 1    | VDH+0.3    | V     |

| CMOS Bi-directional buffer Input / Output Voltage | -      | -0.3 | ı    | 3.6        | V     |

| CML Receiver Input Voltage                        | -      | -0.3 | ı    | VDL+0.3    | V     |

| CML Bi-directional buffer Input / Output Voltage  | -      | -0.3 | ı    | VDL+0.3    | V     |

| LVDS Transmitter Output Voltage                   | -      | -0.3 | -    | VDH+0.3    | V     |

| Output Current                                    | -      | -30  | -    | 30         | mΑ    |

| Storage Temperature                               | -      | -55  | ı    | +125       | °C    |

| Junction Temperature                              | -      | ı    | ı    | +125       | °C    |

| Reflow Peak Temperature/Time                      | -      | -    | -    | +260/10sec | °C    |

| Maximum Power Dissipation @ +25°C                 | -      | -    | -    | 3.2        | W     |

<sup>\* &</sup>quot;Absolute Maximum Ratings" are those values beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

\_\_\_

### 10. Operating Conditions

There are two types of operating temperature ranges as shown below.

- 1. From 0°C to 70°C

- 2. From -40°C to 105°C

Details are shown in the table below.

### Table 21 THCV233 Operating Conditions (0°C≤TMP≤70°C)

| Parameter                             | Symbol | Min. | Тур. | Max. | Units |

|---------------------------------------|--------|------|------|------|-------|

| 1.8v Supply Voltage (CAVDL,CPVDL,VDD) | VDL    | 1.62 | 1.80 | 1.98 | V     |

| 3.3v Supply Voltage(LAVDH)            | VDH    | 3.00 | 3.30 | 3.60 | V     |

| Operating Temperature                 | TMP    | 0    | -    | 70   | °C    |

### Table 22 THCV233 Operating Conditions (-40°C≤TMP≤105°C)

| Parameter                             | Symbol | Min.                        | Тур. | Max. | Units |

|---------------------------------------|--------|-----------------------------|------|------|-------|

| 1.8v Supply Voltage (CAVDL,CPVDL,VDD) | VDL    | 1.62 or 1.70 <sup>(1)</sup> | 1.80 | 1.98 | V     |

| 3.3v Supply Voltage(LAVDH)            | VDH    | 3.00                        | 3.30 | 3.60 | V     |

| Operating Temperature                 | TMP    | -40                         | -    | 105  | °C    |

#### Table 23 THCV234 Operating Conditions (0°C≤TMP≤70°C)

| Parameter                             | Symbol | Min. | Тур. | Max. | Units |

|---------------------------------------|--------|------|------|------|-------|

| 1.8v Supply Voltage (CAVDL,CPVDL,VDD) | VDL    | 1.62 | 1.80 | 1.98 | V     |

| 3.3v Supply Voltage(LAVDH)            | VDH    | 3.00 | 3.30 | 3.60 | V     |

| Operating Temperature                 | TMP    | 0    | -    | 70   | °C    |

#### Table 24 THCV234 Operating Conditions (-40°C≤TMP≤105°C)

| Parameter                             | Symbol | Min. | Тур. | Max. | Units |

|---------------------------------------|--------|------|------|------|-------|

| 1.8v Supply Voltage (CAVDL,CPVDL,VDD) | VDL    | 1.70 | 1.80 | 1.98 | V     |

| 3.3v Supply Voltage(LAVDH)            | VDH    | 3.00 | 3.30 | 3.60 | V     |

| Operating Temperature                 | TMP    | -40  | -    | 105  | °C    |

(1) Maximum value of LVDS CLK Frequency depends on minimum value of VDL. Please refer to page 1.

### 11. Electrical Specifications

### DC Specifications

### Table 25 THCV233 and THCV234 3.3V CMOS DC Specifications

| Symbol | Parameter                 | Conditions     | Min. | Тур. | Max. | Units |

|--------|---------------------------|----------------|------|------|------|-------|

| VIH    | High Level Input Voltage  | I,B,BO,BPU     | 2.1  | -    | VDH  | V     |

| VIL    | Low Level Input Voltage   | I,B,BO,BPU     | 0    | -    | 0.7  | V     |

| VOH    | High Level Output Voltage | B IOH=-8mA     | 2.4  | -    | VDH  | V     |

| VOL    | Low Level Output Voltage  | B IOL=8mA      | -    | -    | 0.4  | V     |

| VOL    | Low Level Output Voltage  | BO,BPU IOL=4mA | -    | -    | 0.4  | V     |

| IIH    | Input Leak Current High   | VIN=VDH        | -10  | -    | +10  | uA    |

| IIL    | Input Leak Current Low    | VIN=GND        | -10  | -    | +10  | uA    |

### Table 26 THCV233 LVDS, CML DC Specifications

| Symbol | Parameter                              | Conditions                        | Min. | Тур.       | Max. | Units |

|--------|----------------------------------------|-----------------------------------|------|------------|------|-------|

| VTTH   | LVDS Differential Input High Threshold | -                                 | -    | -          | 100  | mV    |

| VTTL   | LVDS Differential Input Low Threshold  | -                                 | -100 | -          | -    | mV    |

| ПН     | LVDS Input Leak Current High           | TLx+/-=VDH, PDN[0]=L<br>x=A~E,CLK | -    | -          | ±10  | uA    |

| ΠL     | LVDS Input Leak Current Low            | TLx+/-=GND, PDN[0]=L<br>x=A~E,CLK | =    | -          | ±10  | uA    |

| RTIN   | LVDS Differential Input Resistance     | PDN[0]=L                          | 80   | 100        | 120  | Ω     |

| VTOD   | CML Differential Mode Output Voltage   | -                                 | 200  | 300        | 400  | mV    |

| PRE    | CMI Dra amphania I aval                | PRE=L                             | -    | 0          | -    | %     |

| PRE    | CML Pre-emphasis Level                 | PRE=H                             | 80   | 100        | 120  | %     |

| VTOC   | CML Common Mode Output Voltage         | PRE=L                             |      | VDL-VTOD   |      | mV    |

| VIOC   | CIVIL Common wode Odiput Voltage       | PRE=H                             |      | VDL-2×VTOD |      | mV    |

| ITOH   | CML Output Leak Current High           | PDN[0]=L                          | -    | -          | ±10  | uA    |

| ITOS   | CML Output Short Circuit Current       | VDL=1.8V                          | -90  | =          | -    | mA    |

### Table 27 THCV234 LVDS, CML DC Specifications

| Symbol | Parameter                                             | Conditions                                | Min.  | Тур. | Max.  | Units |

|--------|-------------------------------------------------------|-------------------------------------------|-------|------|-------|-------|

| VRTH   | CML Differential Input High Threshold                 | -                                         | -     | -    | 50    | mV    |

| VRTL   | CML Differential Input Low Threshold                  | -                                         | -50   | -    | =     | mV    |

| IRIH   | CML Input Leak Current High                           | PDN[0]=L, RXnP/N=VDL<br>n=0,1             | -     | =    | ±10   | uA    |

| IRIL   | CML Input Leak Current Low                            | PDN[0]=L, RXnP/N=GND<br>n=0,1             | -     | -    | ±10   | uA    |

| IRRIH  | CML Input Current High                                | RXnP/N=VDL, n=0,1                         | -     | -    | 2     | mA    |

| IRRIL  | CML Input Current Low                                 | RXnP/N=GND, n=0,1                         | -6    | -    | =     | mA    |

| RRIN   | CML Differential Input Resistance                     | -                                         | 80    | 100  | 120   | Ω     |

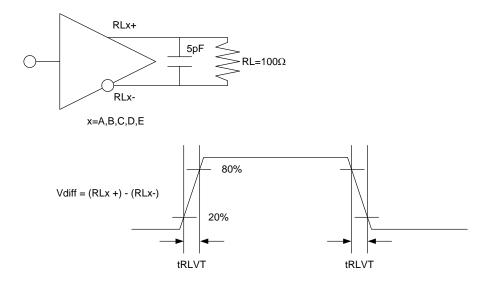

| VROD   | LVDS Differential Mode Output Voltage (Normal Swing)  | RL=100Ω, RS=H                             | 250   | 350  | 450   | mV    |

| VKOD   | LVDS Differential Mode Output Voltage (Reduced Swing) | RL=100Ω, RS=L                             | 100   | 200  | 300   | mV    |

| ΔVROD  | Change in VROD between<br>Complementary Output States | RL=100Ω                                   | -     | -    | 35    | mV    |

| VROC   | LVDS Common Mode Output Voltage                       | RL=100Ω                                   | 1.125 | 1.25 | 1.375 | V     |

| ΔVROC  | Change in VROC between Complementary Output States    | RL=100Ω                                   | -     | -    | 35    | mV    |

| IROS   | LVDS Output Short Circuit Current                     | RLx+/-=GND                                | -30   | -    | -     | mA    |

| IROZ   | LVDS Output TRI-STATE Current                         | PDN[0]=L,<br>RLx+/-=GND, VDH<br>x=A~E,CLK | -     | -    | ±10   | uA    |

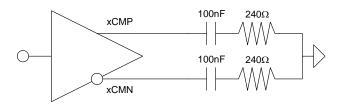

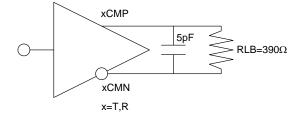

## Table 28 THCV233-234 CML Bi-Directional DC Specifications

| Symbol | Parameter                                               | Conditions      | Min.    | Тур. | Max.    | Units |

|--------|---------------------------------------------------------|-----------------|---------|------|---------|-------|

| VBTH   | Bi-Directional Buffer Differential Input High Threshold | -               | -       | -    | 175     | mV    |

| VBTL   | Bi-Directional Buffer Differential Input Low Threshold  | -               | -175    | -    | -       | mV    |

| VBTC   | Bi-Directional Buffer Input Terminated Common Voltage   | -               | VDL-0.6 | -    | VDL-0.3 | V     |

| VBOD   | Bi-Directional Buffer Differential Output Voltage       | RLB=390Ω        | 500     | -    | 800     | mV    |

| VBOC   | Bi-Directional Buffer Output Voltage                    | -               | VDL-0.6 | -    | VDL-0.3 | V     |

| IBOS   | Bi-Directional Buffer Output Short Circuit Current      | xCMP/N=VDL, GND | -30     | -    | -       | mA    |

| IBIZ   | Bi-Directional Buffer<br>Output Leak Current            | PDN=L           | -       | -    | ±10     | uA    |

| RBIN   | Bi-Directional Buffer Differential Input Resistance     | -               | 390     | -    | 550     | Ω     |

# Supply Currents

### Table 29 THCV233 Supply Currents

| Symbol   | Parameter                                                                                                     | Conditions                            | Min. | Тур. | Max.                                                 | Units |

|----------|---------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|------------------------------------------------------|-------|

|          | Transmitter Cumply Current for \/DI                                                                           | SiSo 10bit, PRE=H<br>PDN[1:0]=HH      | -    | -    | Max. 175 210 250 150 185 225 25 12 12 12 12 12 12 12 | mA    |

| пссм     | Transmitter Supply Current for VDL Main-Link & Sub-Link are active (Worst Case Pattern as shown in Figure 11) | SiDo 10bit, PRE=H<br>PDN[1:0]=HH      | -    | -    | 210                                                  | mA    |

|          | (Worst Case Fattern as shown in Figure 11)                                                                    | SiDDo 10bit, PRE=H<br>PDN[1:0]=HH     | -    | -    | 175 210 250 150 185 225 25 12 12 12 12 12 12         | mA    |

|          | Transmitter Supply Current for VDL                                                                            | SiSo 10bit, PRE=H<br>PDN[1:0]=LH      | -    | -    | 210 250 150 185 225 25 12 12 12 12 12 12 12 12       | mA    |

| ITCCW_M  | Only Main-Link is active (Worst Case Pattern as shown in Figure 11)                                           | SiDo 10bit, PRE=H<br>PDN[1:0]=LH      | -    | -    | 185                                                  | mA    |

|          | (Treat ease Fation as she mining gare 11)                                                                     | SiDDo 10bit, PRE=H<br>PDN[1:0]=LH     | -    | -    |                                                      | mA    |

| пссw_s   | Transmitter Supply Current for VDL<br>Only Sub-Link is active                                                 | PDN[1:0]=HL                           | -    | -    | 25                                                   | mA    |

|          | Transmitter Supply Current for VDH                                                                            | SiSo 10bit, PRE=H<br>PDN[1:0]=HH      | -    | -    | 12                                                   | mA    |

| пссw33   | Main-Link & Sub-Link are active (Worst Case Pattern as shown in Figure 11)                                    | SiDo 10bit, PRE=H<br>PDN[1:0]=HH      | -    | -    | 12                                                   | mA    |

|          | (Worst Case Fattern as shown in Figure 11)                                                                    | SiDDo 10bit, PRE=H<br>PDN[1:0]=HH     | -    | -    | 12                                                   | mA    |

|          | Transmitter Supply Current for VDH                                                                            | SiSo 10bit, PRE=H<br>PDN[1:0]=LH      | -    | -    | 12                                                   | mA    |

| пссмзз_м | Only Main-Link is active (Worst Case Pattern as shown in Figure 11)                                           | SiDo 10bit, PRE=H<br>PDN[1:0]=LH      | -    | -    | 12                                                   | mA    |

|          | (Word Gaso Fallon as shown in Igaio 11)                                                                       | SiDDo 10bit, PRE=H<br>PDN[1:0]=LH     | -    | -    | 12                                                   | mA    |

| пссw33_s | Transmitter Supply Current for VDH<br>Only Sub-Link is active                                                 | PDN[1:0]=HL                           | -    | -    | 1                                                    | mA    |

| пссѕ     | Transmitter Power Down Supply Current                                                                         | PDN[1:0]=LL<br>All Inputs =Fixed LorH | -    | -    | 170                                                  | uA    |

### Table 30 THCV234 Supply Currents

| Symbol    | Parameter                                                                                                  | Conditions                            | Min. | Тур. | Max.                                  | Units |

|-----------|------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|---------------------------------------|-------|

|           | Danis and Complete Company (Co.) (DI                                                                       | SiSo 10bit,<br>PDN[1:0]=HH            | -    | -    | 115                                   | mA    |

| IRCCW     | Receiver Supply Current for VDL Main-Link & Sub-Link are active (Worst Case Pattern as shown in Figure 11) | DiSo 10bit,<br>PDN[1:0]=HH            | -    | -    | 120                                   | mA    |

|           | (Worst Case Fattern as shown in Figure 11)                                                                 | DiSSo 10bit,<br>PDN[1:0]=HH           | -    | -    | 115                                   | mA    |

|           | Receiver Supply Current for VDL                                                                            | SiSo 10bit,<br>PDN[1:0]=LH            | -    | -    | 120 115 90 90 90 25 100 100 100 90 90 | mA    |

| IRCCW_M   | Only Main-Link is active (Worst Case Pattern as shown in Figure 11)                                        | DiSo 10bit,<br>PDN[1:0]=LH            | -    | -    | 90                                    | mA    |

|           | (Worst Case Fattern as shown in Figure 11)                                                                 | DiSSo 10bit,<br>PDN[1:0]=LH           | -    | -    |                                       | mA    |

| IRCCW_S   | Receiver Supply Current for VDL<br>Only Sub-Link is active                                                 | PDN[1:0]=HL                           | -    | -    | 25                                    | mA    |

|           | D : 0 10 1/ WDU                                                                                            | SiSo 10bit,<br>PDN[1:0]=HH            | -    | -    | 100                                   | mA    |

| IRCCW33   | Receiver Supply Current for VDH Main-Link & Sub-Link are active (Worst Case Pattern as shown in Figure 11) | DiSo 10bit,<br>PDN[1:0]=HH            | -    | -    | 100                                   | mA    |

|           | (Worst Case Fattern as shown in Figure 11)                                                                 | DiSSo 10bit,<br>PDN[1:0]=HH           | -    | -    | 100                                   | mA    |

|           | Receiver Supply Current for VDH                                                                            | SiSo 10bit, P<br>PDN[1:0]=LH          | -    | -    | 90                                    | mA    |

| IRCCW33_M | Only Main-Link is active (Worst Case Pattern as shown in Figure 11)                                        | DiSo 10bit,<br>PDN[1:0]=LH            | -    | -    | 90                                    | mA    |

|           | (Worst Case Fattern as shown in Figure 11)                                                                 | DiSSo 10bit,<br>PDN[1:0]=LH           | -    | -    | 90                                    | mA    |

| IRCCW33_S | Receiver Supply Current for VDH<br>Only Sub-Link is active                                                 | PDN[1:0]=HL                           | -    | -    | 5                                     | mA    |

| IRCCS     | Receiver Power Down<br>Supply Current                                                                      | PDN[1:0]=LL<br>All Inputs =Fixed LorH | -    | -    | 150                                   | uA    |

Figure 12 Worst Case Pattern

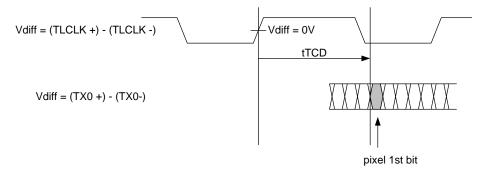

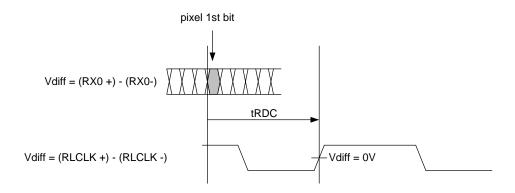

### **Switching Characteristics**

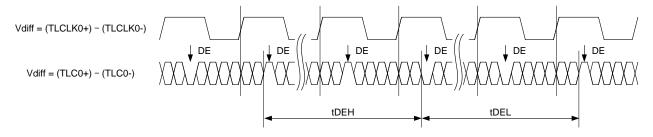

### Table 31 DE requirement

| Symbol | Parameter        | Conditions  | Min.    | Тур. | Max. | Units |

|--------|------------------|-------------|---------|------|------|-------|

| tDEH   | DE=High Duration | -           | 2xtTCIP | -    | -    | sec   |

| tDEL   | DE=Low Duration  | SiSo, SiDDo | 2xtTCIP | -    | -    | sec   |

| IDEL   | DE=LOW Duration  | SiDo        | 4xtTCIP | -    | -    | sec   |

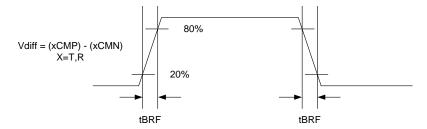

### Table 32 THCV233 Switching Characteristics (0°C≤TMP≤70°C)