## 8251A PROGRAMMABLE COMMUNICATION INTERFACE

- Synchronous and Asynchronous Operation

- Synchronous 5-8 Bit Characters; Internal or External Character Synchronization; Automatic Sync Insertion

- Asynchronous 5–8 Bit Characters; Clock Rate—1, 16 or 64 Times Baud Rate; Break Character Generation; 1, 1½, or 2 Stop Bits; False Start Bit Detection; Automatic Break Detect and Handling

- Synchronous Baud Rate—DC to 64K Baud

- Asynchronous Baud Rate—DC to 19.2K Baud

- Full-Duplex, Double-Buffered Transmitter and Receiver

- Error Detection—Parity, Overrun and Framing

- Compatible with an Extended Range of intel Microprocessors

- 28-Pin DIP Package

- All Inputs and Outputs are TTL Compatible

- Available in EXPRESS and Military Versions

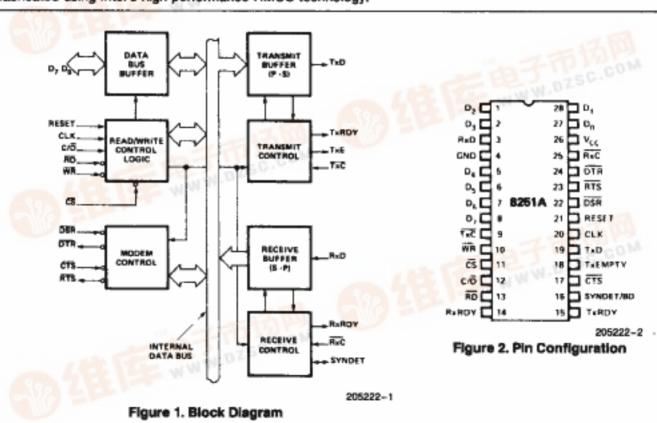

The Intel® 8251A is the industry standard Universal Synchronous/Asynchronous Receiver/Transmitter (USART), designed for data communications with Intel's microprocessor families such as MCS-48, 80, 85, and iAPX-86, 88. The 8251A is used as a peripheral device and is programmed by the CPU to operate using virtually any serial data transmission technique presently in use (including IBM "bi-sync"). The USART accepts data characters from the CPU in parallel format and then converts them into a continuous serial data stream for transmission. Simultaneously, it can receive serial data streams and convert them into parallel data characters for the CPU. The USART will signal the CPU whenever it can accept a new character for transmission or whenever it has received a character for the CPU. The CPU can read the complete status of the USART at any time. These include data transmission errors and control signals such as SYNDET, TxEMPTY. The chip is fabricated using Intel's high performance HMOS technology.

#### FEATURES AND ENHANCEMENTS

The 8251A is an advanced design of the industry standard USART, the Intel® 8251. The 8251A operates with an extended range of Intel microprocessors and maintains compatibility with the 8251. Familiarization time is minimal because of compatibility and involves only knowing the additional features and enhancements, and reviewing the AC and DC specifications of the 8251A.

The 8251A incorporates all the key features of the 8251 and has the following additional features and enhancements:

- 8251A has double-buffered data paths with separate I/O registers for control, status, Data In, and Data Out, which considerably simplifies control programming and minimizes CPU overhead.

- In asynchronous operations, the Receiver detects and handles "break" automatically, relieving the CPU of this task.

- A refined Rx initialization prevents the Receivers from starting when in "break" state, preventing unwanted interrupts from a disconnected USART.

- At the conclusion of a transmission, TxD line will always return to the marking state unless SBRK is programmed.

- Tx Enable logic enhancement prevents a Tx Disable command from halting transmission until all data previously written has been transmitted. The logic also prevents the transmitter from turning off in the middle of a word.

- When External Sync Detect is programmed, Internal Sync Detect is disabled, and an External Sync Detect status is provided via a flip-flop which clears itself upon a status read.

- Possibility of false sync detect is minimized by ensuring that if double character sync is programmed, the characters be contiguously detected and also by clearing the Rx register to all ones whenever Enter Hunt command is issued in Sync mode.

- As long as the 8251A is not selected, the RD and WR do not affect the internal operation of the device.

- The 8251A Status can be read at any time but the status update will be inhibited during status read.

- The 8251A is free from extraneous glitches and has enhanced AC and DC characteristics, providing higher speed and better operating margins.

- Synchronous Baud rate from DC to 64K.

#### FUNCTIONAL DESCRIPTION

#### General

The 8251A is a Universal Synchronous/Asynchronous Receiver/Transmitter designed for a wide range of Intel microcomputers such as 8048, 8080, 8085, 8086 and 8088. Like other I/O devices in a microcomputer system, its functional configuration is programmed by the system's software for maximum flexibility. The 8251A can support most serial data techniques in use, including IBM "bi-sync".

In a communication environment an interface device must convert parallel format system data into serial format for transmission and convert incoming serial format data into parallel system data for reception. The interface device must also delete or insert bits or characters that are functionally unique to the communication technique. In essence, the interface should appear "transparent" to the CPU, a simple input or output of byte-oriented system data.

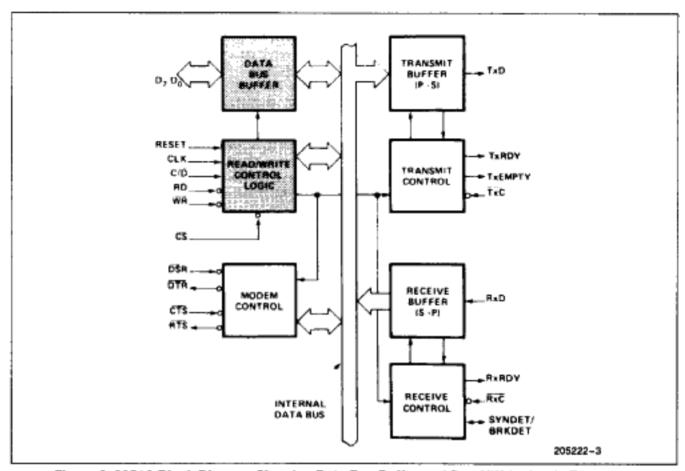

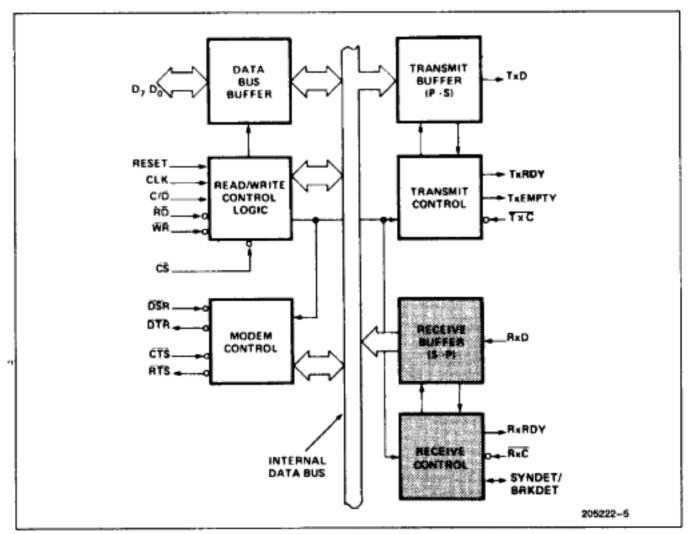

#### Data Bus Buffer

This 3-state bidirectional, 8-bit buffer is used to interface the 8251A to the system Data Bus. Data is transmitted or received by the buffer upon execution of INput or OUTput instructions of the CPU. Control words, Command words and Status information are also transferred through the Data Bus Buffer. The Command Status, Data-In and Data-Out registers are separate, 8-bit registers communicating with the system bus through the Data Bus Buffer.

This functional block accepts inputs from the system Control bus and generates control signals for overall device operation. It contains the Control Word Register and Command Word Register that store the various control formats for the device functional definition.

#### RESET (Reset)

A "high" on this input forces the 8251A into an "idle" mode. The device will remain at "idle" until a new set of control words is written into the 8251A to program its functional definition. Minimum RESET pulse width is 6 to (clock must be running).

A command reset operation also puts the device into the "idle" state.

Figure 3. 8251A Block Diagram Showing Data Bus Buffer and Read/Write Logic Functions

#### CLK (Clock)

The CLK input is used to generate internal device timing and is normally connected to the Phase 2 (TTL) output of the Clock Generator. No external inputs or outputs are referenced to CLK but the frequency of CLK must be greater than 30 times the Receiver or Transmitter data bit rates.

#### WR (Write)

A "low" on this input informs the 8251A that the CPU is writing data or control words to the 8251A.

#### RD (Read)

A "low" on this input informs the 8251A that the CPU is reading data or status information from the 8251A.

| C/D | RD | WR | CS |                       |

|-----|----|----|----|-----------------------|

| 0   | 0  | 1  | 0  | 8251A DATA → DATA BUS |

| 0   | 1  | 0  | 0  | DATA BUS → 8251A DATA |

| 1   | 0  | 1  | 0  | STATUS → DATA BUS     |

| 1   | 1  | 0  | 0  | DATA BUS → CONTROL    |

| X   | 1  | 1  | 0  | DATA BUS → 3-STATE    |

| X   | X  | Х  | 1  | DATA BUS → 3-STATE    |

#### C/D (Control/Data)

This input, in conjunction with the WR and RD inputs, informs the 8251A that the word on the Data Bus is either a data character, control word or status information.

1 - CONTROL/STATUS; 0 = DATA.

#### CS (Chip Select)

A "low" on this input selects the 8251A. No reading or writing will occur unless the device is selected. When CS is high, the Data Bus is in the float state and RD and WR have no effect on the chip.

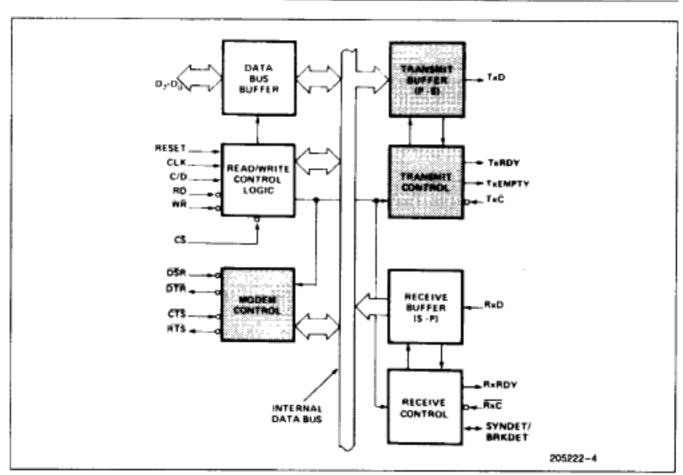

#### Modem Control

The 8251A has a set of control inputs and outputs that can be used to simplify the interface to almost any modern. The modern control signals are general purpose in nature and can be used for functions other than modern control, if necessary.

#### DSR (Data Set Ready)

The DSR input signal is a general-purpose, 1-bit inverting input port. Its condition can be tested by the CPU using a Status Read operation. The DSR input is normally used to test modern conditions such as Data Set Ready.

#### DTR (Data Terminal Ready)

The DTR output signal is a general-purpose, 1-bit inverting output port. It can be set "low" by programming the appropriate bit in the Command Instruction word. The DTR output signal is normally used for modern control such as Data Terminal Ready.

#### RTS (Request to Send)

The RTS output signal is a general-purpose, 1-bit inverting output port. It can be set "low" by programming the appropriate bit in the Command Instruction word. The RTS output signal is normally used for modern control such as Request to Send.

#### CTS (Clear to Send)

A "low" on this input enables the 8251A to transmit serial data if the Tx Enable bit in the Command byte is set to a "one". If either a Tx Enable off or CTS off condition occurs while the Tx is in operation, the Tx will transmit all the data in the USART, written prior to Tx Disable command before shutting down.

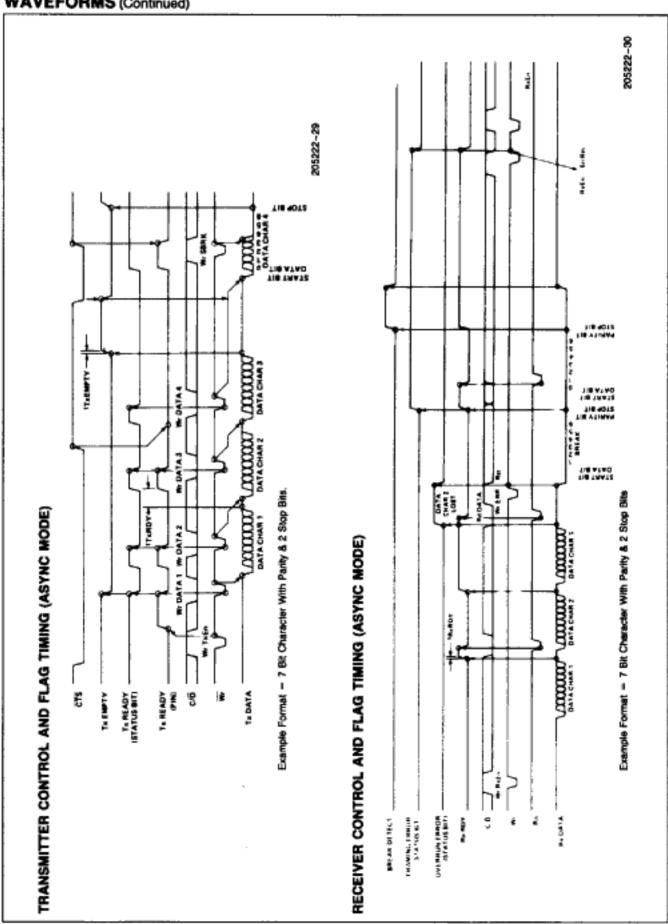

#### Transmitter Buffer

The Transmitter Buffer accepts parallel data from the Data Bus Buffer, converts it to a serial bit stream, inserts the appropriate characters or bits (based on the communication technique) and outputs a composite serial stream of data on the TxD output pin on the falling edge of TxC. The transmitter will begin transmission upon being enabled if CTS = 0. The TxD line will be held in the marking state immediately upon a master Reset or when Tx Enable or CTS is off or the transmitter is empty.

#### Transmitter Control

The Transmitter Control manages all activities associated with the transmission of serial data. It accepts and issues signals both externally and internally to accomplish this function.

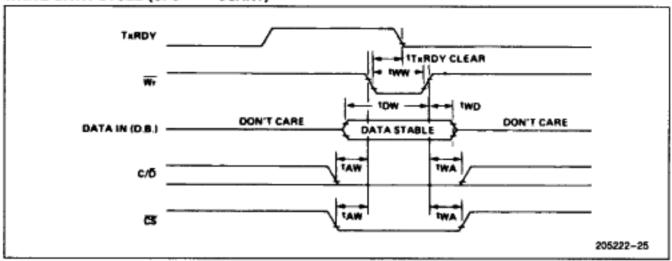

#### TxRDY (Transmitter Ready)

This output signals the CPU that the transmitter is ready to accept a data character. The TxRDY output pin can be used as an interrupt to the system, since it is masked by TxEnable; or, for Polled operation, the CPU can check TxRDY using a Status Read operation. TxRDY is automatically reset by the leading edge of WR when a data character is loaded from the CPU.

Note that when using the Polled operation, the TxRDY status bit is *not* masked by TxEnable, but will only indicate the Empty/Full Status of the Tx Data Input Register.

#### TxE (Transmitter Empty)

When the 8251A has no characters to send, the TxEMPTY output will go "high". It resets upon receiving a character from CPU if the transmitter is enabled. TxEMPTY remains high when the transmitter is disabled. TxEMPTY can be used to indicate the end of a transmission mode, so that the CPU "knows" when to "turn the line around" in the half-duplex operational mode.

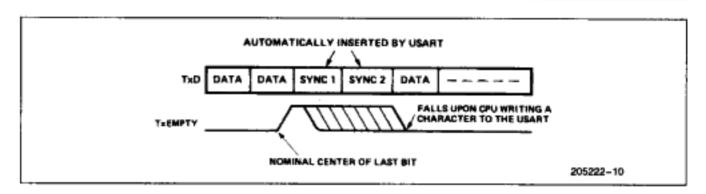

In the Synchronous mode, a "high" on this output indicates that a character has not been loaded and the SYNC character or characters are about to be or are being transmitted automatically as "filiers". Tx EMPTY does not go low when the SYNC characters are being shifted out.

Figure 4. 8251A Block Diagram Showing Modern and Transmitter Buffer and Control Functions

#### TxC (Transmitter Clock)

The Transmitter Clock controls the rate at which the character is to be transmitted. In the Synchronous transmission mode, the Baud Rate (1x) is equal to the TxC frequency. In Asynchronous transmission mode, the baud rate is a fraction of the actual TxC frequency. A portion of the mode instruction selects this factor; it can be 1, ½ or ½ the TxC.

#### For Example:

If Baud Rate equals 110 Baud.

TxC equals 110 Hz in the 1x mode.

TxC equals 1.72 kHz in the 16x mode.

TxC equals 7.04 kHz in the 64x mode.

The falling edge of TxC shifts the serial data out of the 8251A.

#### Receiver Buffer

The Receiver accepts serial data, converts this serial input to parallel format, checks for bits or characters that are unique to the communication technique and sends an "assembled" character to the CPU. Serial data is input to RxD pin, and is clocked in on the rising edge of RxC.

#### Receiver Control

This functional block manages all receiver-related activities which consists of the following features.

The RxD initialization circuit prevents the 8251A from mistaking an unused input line for an active low data line in the "break condition". Before starting to receive serial characters on the RxD line, a valid "1" must first be detected after a chip master Reset. Once this has been determined, a search for a valid low (Start bit) is enabled. This feature is only active in the asynchronous mode, and is only done once for each master Reset.

The False Start bit detection circuit prevents false starts due to a transient noise spike by first detecting the falling edge and then strobing the normal center of the Start bit (RxD = low).

Parity error detection sets the corresponding status bit.

The Framing Error status bit is set if the Stop bit is absent at the end of the data byte (asynchronous mode).

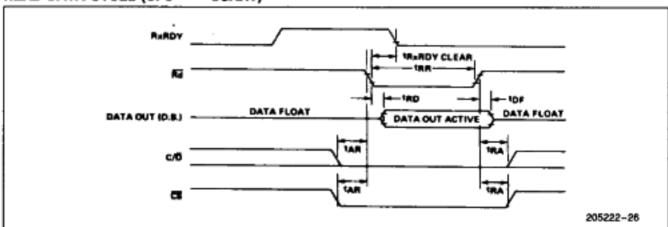

#### RxRDY (Receiver Ready)

This output indicates that the 8251A contains a character that is ready to be input to the CPU. RxRDY can be connected to the interrupt structure of the CPU or, for polled operation, the CPU can check the condition of RxRDY using a Status Read operation.

RxEnable, when off, holds RxRDY in the Reset Condition. For Asynchronous mode, to set RxRDY, the Receiver must be enabled to sense a Start Bit and a complete character must be assembled and transferred to the Data Output Register. For Synchronous mode, to set RxRDY, the Receiver must be enabled and a character must finish assembly and be transferred to the Data Output Register.

Failure to read the received character from the Rx Data Output Register prior to the assembly of the next Rx Data character will set overrun condition error and the previous character will be written over and lost. If the Rx Data is being read by the CPU when the internal transfer is occurring, overrun error will be set and the old character will be lost.

#### RxC (Receiver Clock)

The Receiver Clock controls the rate at which the character is to be received. In Synchronous Mode, the Baud Rate (1x) is equal to the actual frequency of RxC. In Asynchronous Mode, the Baud Rate is a fraction of the actual RxC frequency. A portion of the mode instruction selects this factor: 1, 1/16 or 1/64 the RxC.

#### For Example:

Baud Rate equals 300 Baud, if

RxC equals 300 Hz in the 1x mode;

RxC equals 4800 Hz in the 16x mode;

RxC equals 19.2 kHz in the 64x mode.

Baud Rate equals 2400 Baud, if RxC equals 2400 Hz in the 1x mode; RxC equals 38.4 kHz in the 16 mode;

RxC equals 153.6 kHz in the 64 mode.

Figure 5. 8251A Block Diagram Showing Receiver Buffer and Control Functions

Data is sampled into the 8251A on the rising edge of RxC.

#### NOTE:

In most communication systems, the 8251A will be handling both the transmission and reception operations of a single link. Consequently, the Receive and Transmit Baud Rates will be the same. Both TxC and RxC will require identical frequencies for this operation and can be tied together and connected to a single frequency source (Baud Rate Generator) to simplify the interface.

#### SYNDET (SYNC Detect/ BRKDET Break Detect)

This pin is used in Synchronous Mode for SYNDET and may be used as either input or output, programmable through the Control Word. It is reset to output mode low upon RESET. When used as an output (internal Sync mode), the SYNDET pin will go "high" to indicate that the 8251A has located the SYNC

character in the Receive mode. If the 8251A is programmed to use double Sync characters (bi-sync), then SYNDET will go "high" in the middle of the last bit of the second Sync character. SYNDET is automatically reset upon a Status Read operation.

When used as an input (external SYNC detect mode), a positive going signal will cause the 8251A to start assembling data characters on the rising edge of the next RxC. Once in SYNC, the "high" input signal can be removed. When External SYNC Detect is programmed, Internal SYNC Detect is disabled.

#### BREAK (Async Mode Only)

This output will go high whenever the receiver remains low through two consecutive stop bit sequences (including the start bits, data bits, and parity bits). Break Detect may also be read as a Status bit. It is reset only upon a master chip Reset or Rx Data returning to a "one" state.

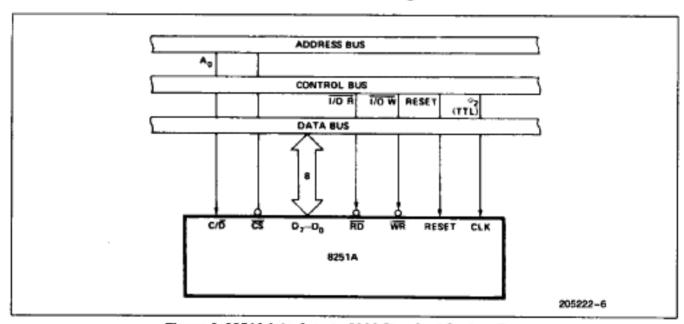

Figure 6. 8251A Interface to 8080 Standard System Bus

#### DETAILED OPERATION DESCRIPTION

#### General

The complete functional definition of the 8251A is programmed by the system's software. A set of control words must be sent out by the CPU to initialize the 8251A to support the desired communications format. These control words will program the: BAUD RATE, CHARACTER LENGTH, NUMBER OF STOP BITS, SYNCHRONOUS or ASYNCHRONOUS OPERATION, EVEN/ODD/OFF PARITY, etc. In the Synchronous Mode, options are also provided to select either internal or external character synchronization.

Once programmed, the 8251A is ready to perform its communication functions. The TxRDY output is raised "high" to signal the CPU that the 8251A is ready to receive a data character from the CPU. This output (TxRDY) is reset automatically when the CPU writes a character into the 8251A. On the other hand, the 8251A receives serial data from the MODEM or I/O device. Upon receiving an entire character, the RxRDY output is raised "high" to signal the CPU that the 8251A has a complete character ready for the CPU to fetch. RxRDY is reset automatically upon the CPU data read operation.

The 8251A cannot begin transmission until the Tx Enable (Transmitter Enable) bit is set in the Command Instruction and it has received a Clear To Send (CTS) input. The TxD output will be held in the marking state upon Reset.

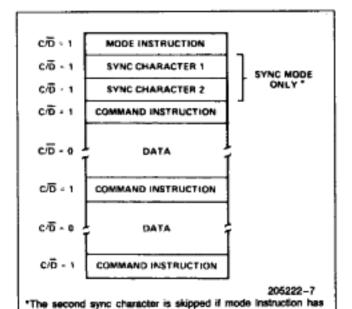

Figure 7. Typical Data Block

programmed the 8251A to single character sync mode. Both

sync characters are skipped if mode instruction has programmed

the 8251A to async mode.

#### Programming the 8251A

Prior to starting data transmission or reception, the 8251A must be loaded with a set of control words generated by the CPU. These control signals define the complete functional definition of the 8251A and must immediately follow a Reset operation (internal or external).

The control words are split into two formats:

- 1. Mode Instruction

- 2. Command Instruction

#### Mode Instruction

This instruction defines the general operational characteristics of the 8251A. It must follow a Reset operation (internal or external). Once the Mode Instruction has been written into the 8251A by the CPU, SYNC characters or Command Instructions may be written.

#### Command Instruction

This instruction defines a word that is used to control the actual operation of the 8251A.

Both the Mode and Command Instructions must conform to a specified sequence for proper device operation (see Figure 7). The Mode Instruction must be written immediately following a Reset operation, prior to using the 8251A for data communication.

All control words written into the 8251A after the Mode Instruction will load the Command Instruction. Command Instructions can be written into the 8251A at any time in the data block during the operation of the 8251A. To return to the Mode Instruction format, the master Reset bit in the Command Instruction word can be set to initiate an internal Reset operation which automatically places the 8251A back into the Mode Instruction format. Command Instructions must follow the Mode Instruction or Sync characters.

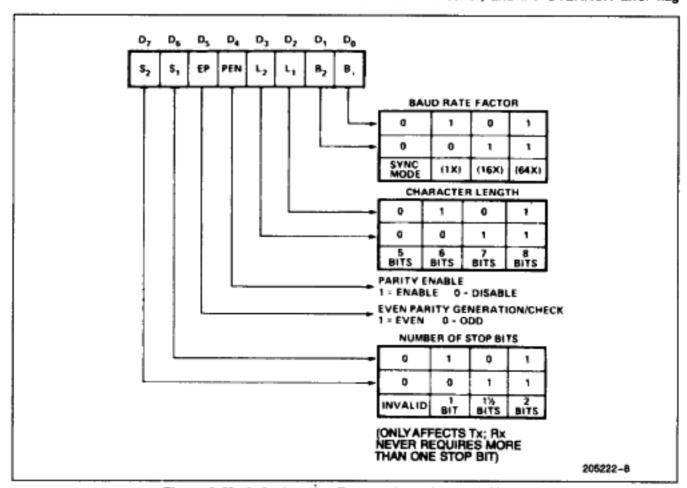

#### Mode Instruction Definition

The 8251A can be used for either Asynchronous or Synchronous data communication. To understand how the Mode Instruction defines the functional operation of the 8251A, the designer can best view the device as two separate components, one Asynchronous and the other Synchronous, sharing the same package. The format definition can be changed only after a master chip Reset. For explanation purposes the two formats will be isolated.

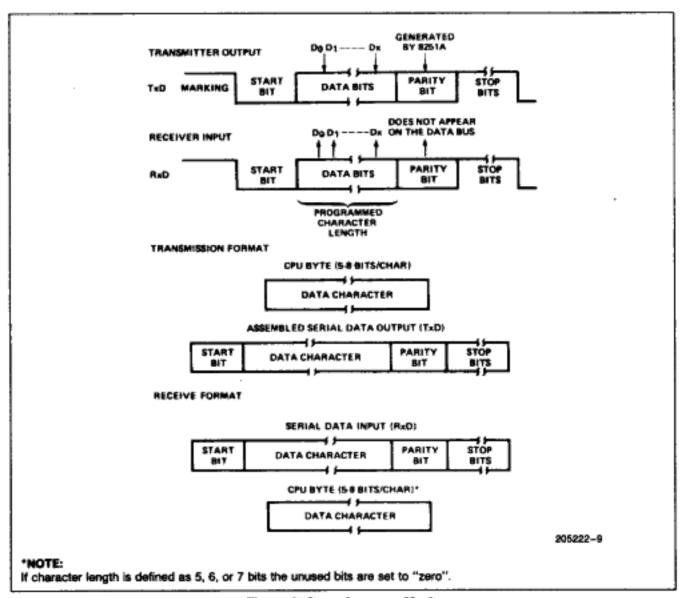

#### NOTE:

When parity is enabled it is not considered as one of the data bits for the purpose of programming word length. The actual parity bit received on the Rx Data line cannot be read on the Data Bus. In the case of a programmed character length of less than 8 bits, the least significant Data Bus bits will hold the data; unused bits are "don't care" when writing data to the 8251A, and will be "zeros" when reading the data from the 8251A.

#### Asynchronous Mode (Transmission)

Whenever a data character is sent by the CPU the 8251A automatically adds a Start bit (low level) followed by the data bits (least significant bit first), and the programmed number of Stop bits to each character. Also, an even or odd Parity bit is inserted prior to the Stop bit(s), as defined by the Mode Instruction. The character is then transmitted as a serial data stream on the TxD output. The serial data is shifted out on the falling edge of TxC at a rate equal to 1, ½, or 1/64 that of the TxC, as defined by the Mode Instruction. BREAK characters can be continuously sent to the TxD if commanded to do so.

When no data characters have been loaded into the 8251A the TxD output remains "high" (marking) unless a Break (continuously low) has been programmed.

#### Asynchronous Mode (Receive)

The RxD line is normally high. A falling edge on this line triggers the beginning of a START bit. The validity of this START bit is checked by again strobing this bit at its nominal center (16X or 64X mode only), If a low is detected again, it is a valid START bit, and the bit counter will start counting. The bit counter thus locates the center of the data bits, the parity bit (if it exists) and the stop bits. If parity error occurs, the parity error flag is set. Data and parity bits are sampled on the RxD pin with the rising edge of the RxC. If a low level is detected as the STOP bit the Framing Error flag will be set. The STOP bit signals the end of a character. Note that the receiver requires only one stop bit, regardless of the number of stop bits programmed. This character is then loaded into the parallel I/O buffer of the 8251A. The RxRDY pin is raised to signal the CPU that a character is ready to be fetched. If a previous character has not been fetched by the CPU, the present character replaces it in the I/O buffer, and the OVERRUN Error flag

Figure 8. Mode Instruction Format, Asynchronous Mode

is raised (thus the previous character is lost). All of the error flags can be reset by an Error Reset Instruction. The occurrence of any of these errors will not affect the operation of the 8251A.

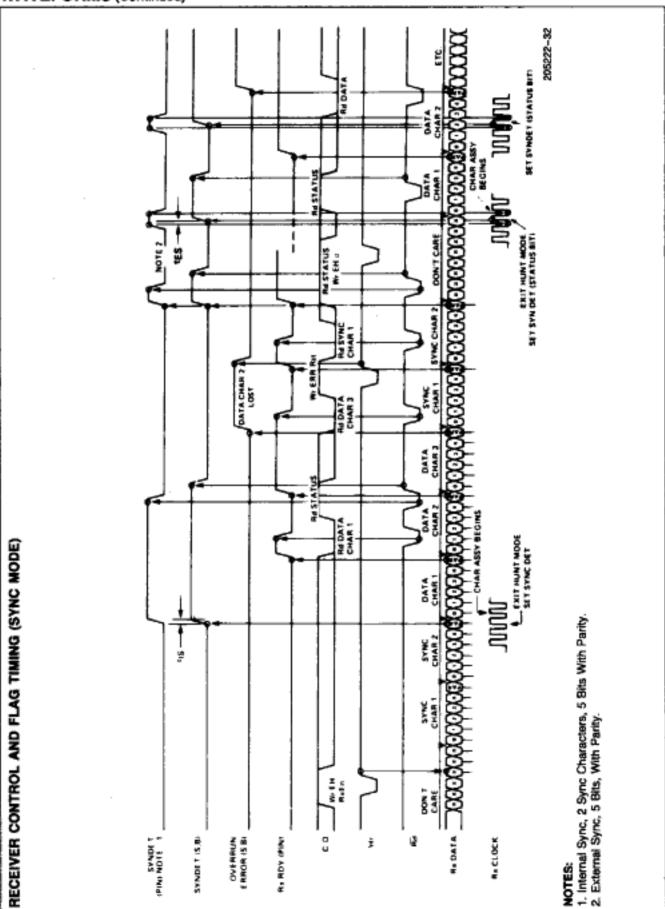

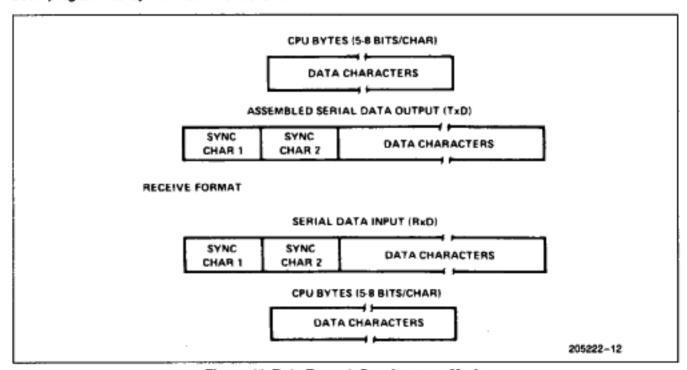

#### Synchronous Mode (Transmission)

The TxD output is continuously high until the CPU sends its first character to the 8251A which usually is a SYNC character. When the CTS line goes low, the first character is serially transmitted out. All characters are shifted out on the falling edge of TxC. Data is shifted out at the same rate as the TxC.

Once transmission has started, the data stream at the TxD output must continue at the TxC rate. If the CPU does not provide the 8251A with a data character before the 8251A Transmitter Buffers become empty, the SYNC characters (or character if in single SYNC character mode) will be automatically inserted in the TxD data stream. In this case, the TxEMPTY pin is raised high to signal that the 8251A is empty and SYNC characters are being sent out. TxEMPTY does not go low when the SYNC is being shifted out (see figure below). The TxEMPTY pin is internally reset by a data character being written into the 8251A.

Figure 9. Asynchronous Mode

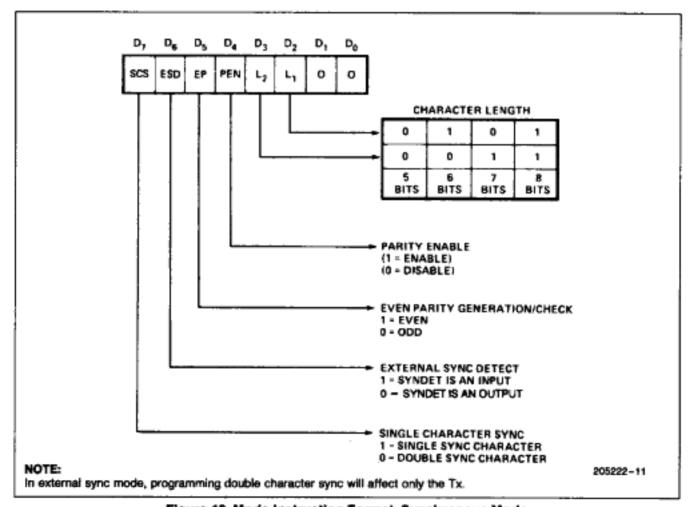

#### Synchronous Mode (Receive)

In this mode, character synchronization can be internally or externally achieved. If the SYNC mode has been programmed, ENTER HUNT command should be included in the first command instruction word written. Data on the RxD pin is then sampled on the rising edge of RxC. The content of the Rx buffer is compared at every bit boundary with the first SYNC character until a match occurs. If the 8251A has been programmed for two SYNC characters, the subsequent received character is also compared; when both SYNC characters have been detected,

the USART ends the HUNT mode and is in character synchronization. The SYNDET pin is then set high, and is reset automatically by a STATUS READ. If parity is programmed, SYNDET will not be set until the middle of the parity bit instead of the middle of the last data bit.

In the external SYNC mode, synchronization is achieved by applying a high level on the SYNDET pin, thus forcing the 8251A out of the HUNT mode. The high level can be removed after one RXC cycle. An ENTER HUNT command has no effect in the asynchronous mode of operation.

Figure 10. Mode Instruction Format, Synchronous Mode

Parity error and overrun error are both checked in the same way as in the Asynchronous Rx mode. Parity is checked when not in Hunt, regardless of whether the Receiver is enabled or not.

The CPU can command the receiver to enter the HUNT mode if synchronization is lost. This will also set all the used character bits in the buffer to a "one," thus preventing a possible false SYNDET caused by data that happens to be in the Rx Buffer at ENTER HUNT time. Note that the SYNDET F/F is reset at each Status Read, regardless of whether internal or external SYNC has been programmed. This does not cause the 8251A to return to the HUNT mode. When in SYNC mode, but not in HUNT, Sync Detection is still functional, but only occurs at the "known" word boundaries. Thus, if one Status Read indicates SYNDET and a second Status Read also indicates SYNDET, then the programmed SYNDET characters have been received since the previous Status Read. (If double character sync has been programmed, then both sync characters have been contiguously received to gate a SYN-DET indication). When external SYNDET mode is selected, internal Sync Detect is disabled, and the SYNDET F/F may be set at any bit boundary.

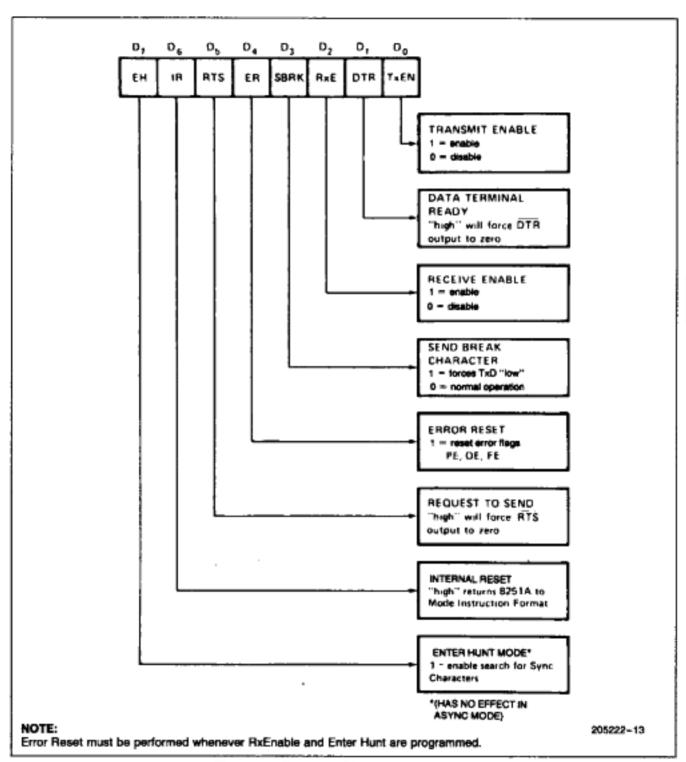

## COMMAND INSTRUCTION DEFINITION

Once the functional definition of the 8251A has been programmed by the Mode Instruction and the Sync characters are loaded (if in Sync Mode) then the device is ready to be used for data communication. The Command Instruction controls the actual operation of the selected format. Functions such as: Enable Transmit/Receive, Error Reset and Modem Controls are provided by the Command instruction.

Once the Mode Instruction has been written into the 8251A and Sync characters inserted, of necessary, then all further "control writes" ( $C/\overline{D}=1$ ) will load a Command Instruction. A Reset Operation (internal or external) will return the 8251A to the Mode Instruction format.

#### NOTE:

Internal Reset on Power-up:

When power is first applied, the 8251A may come up in the Mode, Sync character or Command format. To guarantee that the device is in the Command Instruction format before the Reset command is issued, it is safest to execute the worst-case initialization sequence (sync mode with two sync characters). Loading three 00Hs consecutively into the device with  $C/\overline{D}=1$  configures sync operation and writes two dummy 00H sync characters. An Internal Reset command (40H) may then be issued to return the device to the "idle" state.

Figure 11. Data Format, Synchronous Mode

Figure 12. Command Instruction Format

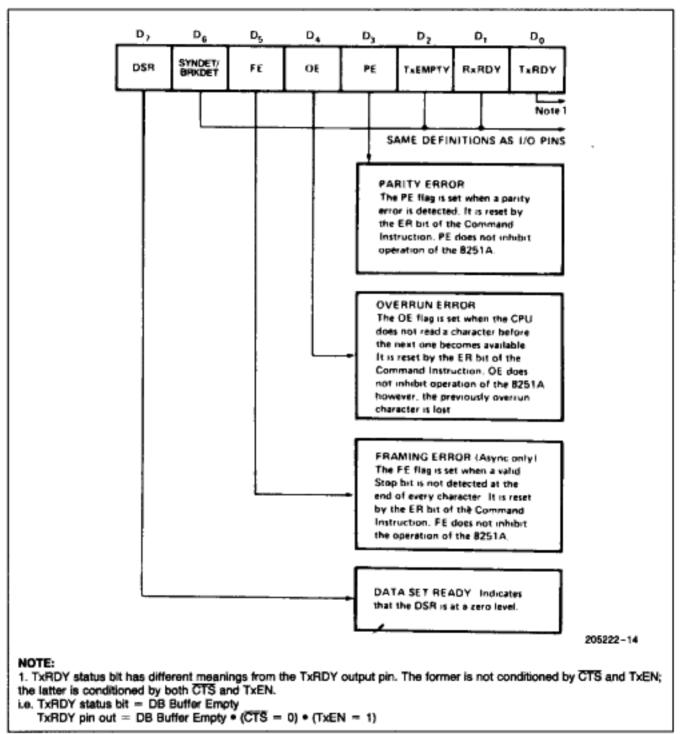

#### STATUS READ DEFINITION

In data communication systems it is often necessary to examine the "status" of the active device to ascertain if errors have occurred or other conditions that require the processor's attention. The 8251A has facilities that allow the programmer to "read" the status of the device at any time during the functional operation. (Status update is inhibited during status read.)

A normal "read" command is issued by the CPU with  $C/\overline{D}=1$  to accomplish this function.

Some of the bits in the Status Read Format have identical meanings to external output pins so that the 8251A can be used in a completely polled or interrupt-driven environment. TxRDY is an exception.

Note that status update can have a maximum delay of 28 clock periods from the actual event affecting the status.

Figure 13. Status Read Format

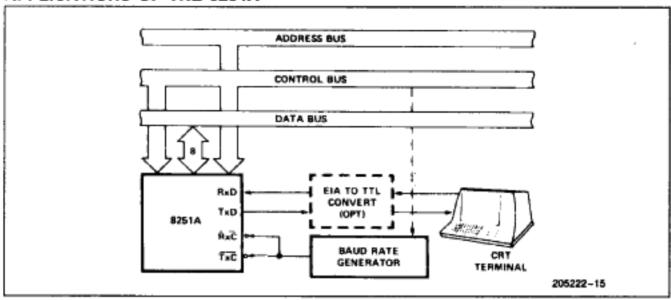

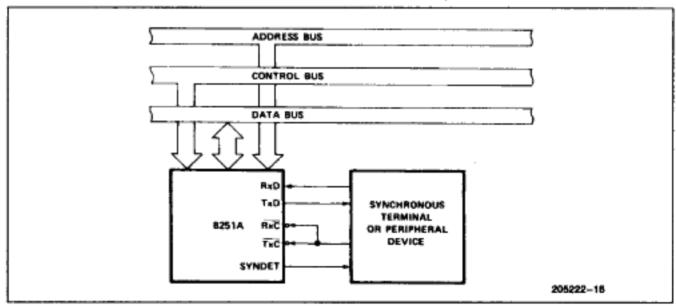

#### **APPLICATIONS OF THE 8251A**

Figure 14. Asynchronous Serial Interface to CRT Terminal, DC-9600 Baud

Figure 15. Synchronous Interface to Terminal or Peripheral Device

#### APPLICATIONS OF THE 8251A (Continued)

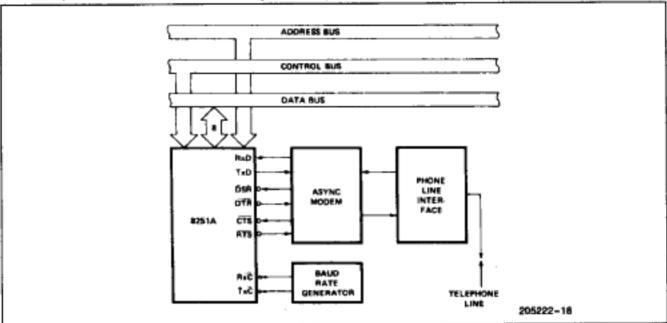

Figure 16. Asynchronous Interface to Telephone Lines

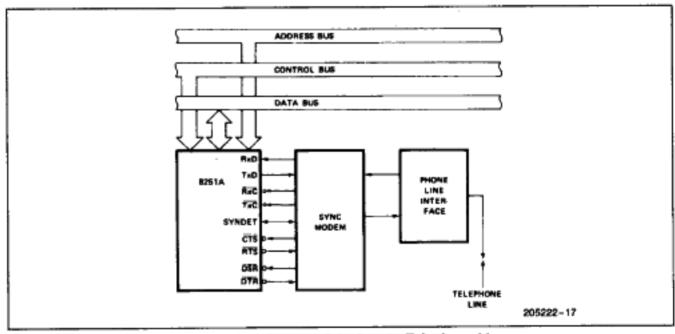

Figure 17. Synchronous Interface to Telephone Lines

#### NOTES:

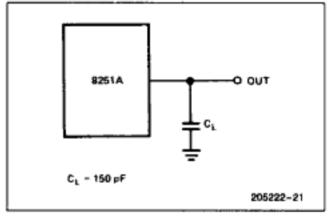

- AC timings measured V<sub>OH</sub> = 2.0 V<sub>OL</sub> = 0.8, and with load circuit of Figure 18.

Chip Select (CS) and Command/Data (C/D) are considered as Addresses.

- Assumes that Address is valid before R<sub>D</sub> ↓.

- 4. This recovery time is for Mode Initialization only. Write Data is allowed only when TxRDY = 1. Recovery Time between Writes for Asynchronous Mode is 8 toy and for Synchronous Mode is 16 toy.

- The TxC and RxC frequencies have the following limitations with respect to CLK: For 1x Baud Rate, f<sub>Tx</sub> or f<sub>Rx</sub> ≤

- 1/(30 t<sub>CY</sub>): For 16x and 64x Baud Rate, t<sub>Tx</sub> or f<sub>Rx</sub> ≤ 1/(4.5 t<sub>CY</sub>). This applies to Baud Rates less than or equal to 64K Baud.

- Reset Pulse Width = 6 t<sub>GY</sub> minimum; System clock must be running during Reset.

- Status update can have a maximum delay of 28 clock periods from the event affecting the status.

- 8. In external sync mode the tes spec, requires the ratio of the system clock (clock) to receive or transmit bit ratios to be greater than 34.

- 9. A float is defined as the point where the data bus falls below a logic 1 (2.0V @ IOH limit) or rises above a Logic 0 (0.8V @ loL limit).

#### ABSOLUTE MAXIMUM RATINGS\*

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### D.C. CHARACTERISTICS TA = 0°C to 70°C, VCC = 5.0V ±.10%, GND = 0V°

| Symbol          | Parameter            | Min  | Max  | Unit | Test Conditions                             |

|-----------------|----------------------|------|------|------|---------------------------------------------|

| V <sub>IL</sub> | Input Low Voltage    | -0.5 | 8.0  | ٧    |                                             |

| V <sub>IH</sub> | Input High Voltage   | 2.0  | Vcc  | ٧    |                                             |

| VOL             | Output Low Voltage   |      | 0.45 | ٧    | I <sub>OL</sub> = 2.2 mA                    |

| V <sub>OH</sub> | Output High Voltage  | 2.4  |      | ٧    | I <sub>OH</sub> = -400 μA                   |

| lofL            | Output Float Leakage |      | ±10  | μА   | V <sub>OUT</sub> = V <sub>CC</sub> to 0.45V |

| IL              | Input Leakage        |      | ±10  | μА   | V <sub>IN</sub> = V <sub>CC</sub> to 0.45V  |

| loc             | Power Supply Current |      | 100  | ma   | All Outputs = High                          |

#### CAPACITANCE TA = 25°C, VCC = GND = 0V

| Symbol           | Parameter         | Min | Max | Unit | Test Conditions                 |

|------------------|-------------------|-----|-----|------|---------------------------------|

| C <sub>IN</sub>  | Input Capacitance |     | 10  | pF   | fc = 1 MHz                      |

| G <sub>1/0</sub> | I/O Capacitance   |     | 20  | pF   | Unmeasured pins returned to GND |

#### A.C. CHARACTERISTICS $T_A = 0$ °C to 70°C, $V_{CC} = 5.0V \pm 10\%$ , GND = 0V°

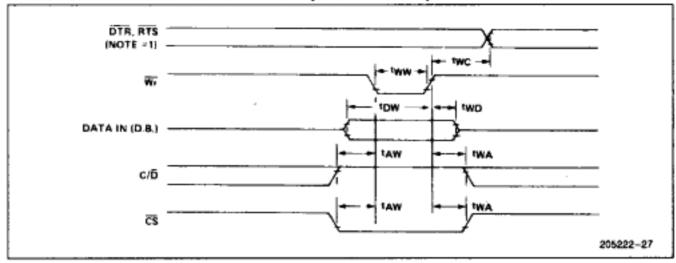

#### **Bus Parameters** (Note 1)

#### READ CYCLE

| Symbol          | Parameter                            | Min | Max | Unit | Test Conditions            |

|-----------------|--------------------------------------|-----|-----|------|----------------------------|

| t <sub>AR</sub> | Address Stable Before READ (CS, C/D) | 0   |     | ns   | (Note 2)                   |

| t <sub>RA</sub> | Address Hold Time for READ (CS, C/D) | 0   |     | ns   | (Note 2)                   |

| t <sub>RR</sub> | READ Pulse Width                     | 250 |     | ns   |                            |

| t <sub>RD</sub> | Data Delay from READ                 |     | 200 | ns   | 3, C <sub>L</sub> = 150 pF |

| tor             | READ to Data Floating                | 10  | 100 | กร   | (Note 1, 9)                |

#### WRITE CYCLE

| Symbol          | Parameter                    | Min | Max | Unit | Test Conditions |

|-----------------|------------------------------|-----|-----|------|-----------------|

| taw             | Address Stable Before WRITE  | 0   |     | ns   |                 |

| twa             | Address Hold Time for WRITE  | 0   |     | ns   |                 |

| tww             | WRITE Pulse Width            | 250 |     | ns   |                 |

| t <sub>DW</sub> | Data Set-Up Time for WRITE   | 150 |     | ns   |                 |

| t <sub>WD</sub> | Data Hold Time for WRITE     | 20  |     | ns   |                 |

| t <sub>RV</sub> | Recovery Time Between WRITES | 6   |     | tcy  | (Note 4)        |

## int<sub>e</sub>l.

#### A.C. CHARACTERISTICS (Continued)

#### OTHER TIMINGS

| Symbol                          | Parameter                                                                    | Min                | Max                 | Unit              | Test Conditions |

|---------------------------------|------------------------------------------------------------------------------|--------------------|---------------------|-------------------|-----------------|

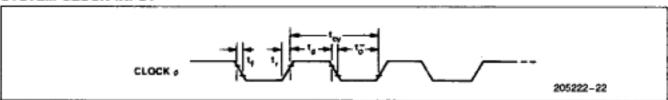

| tcy                             | Clock Period                                                                 | 320                | 1350                | ns                | (Note 5, 6)     |

| L <sub>p</sub>                  | Clock High Pulse Width                                                       | 120                | t <sub>CY</sub> -90 | ns ·              |                 |

| <del>i</del>                    | Clock Low Pulse Width                                                        | 90                 |                     | ns                |                 |

| t <sub>R</sub> , t <sub>F</sub> | Clock Rise and Fall Time                                                     |                    | 20                  | ns                |                 |

| ¹o⊤x                            | TxD Delay from Falling Edge of TxC                                           |                    | 1                   | μs                |                 |

| f <sub>Tx</sub>                 | Transmitter Input Clock Frequency 1x Baud Rate 16x Baud Rate 64x Baud Rate   | DC<br>DC           | 64<br>310<br>615    | kHz<br>kHz<br>kHz |                 |

| tүрw                            | Transmitter Input Clock Pulse Width 1x Baud Rate 16x and 64x Baud Rate       | 12<br>1            |                     | tcy<br>tcy        |                 |

| t <sub>TPD</sub>                | Transmitter Input Clock Pulse Delay<br>1x Baud Rate<br>16x and 64x Baud Rate | 15<br>3            |                     | tcy<br>tcy        |                 |

| f <sub>Rx</sub>                 | Receiver Input Clock Frequency 1x Baud Rate 16x Baud Rate 64x Baud Rate      | DC<br>DC<br>DC     | 64<br>310<br>615    | kHz<br>kHz<br>kHz |                 |

| tapw                            | Receiver Input Clock Pulse Width 1x Baud Rate 16x and 64x Baud Rate          | 12<br>1            |                     | tor<br>tor        |                 |

| <sup>t</sup> RPD                | Receiver Input Clock Pulse Delay<br>1x Baud Rate<br>16x and 64x Baud Rate    | 15<br>3            |                     | tor<br>tor        |                 |

| t <sub>TxRDY</sub>              | TxRDY Pin Delay from Center of Last Bit                                      |                    | 14                  | tcy               | (Note 7)        |

| TXRDY CLEAR                     | TxRDY ↓ from Leading Edge of WR                                              |                    | 400                 | ns                | (Note 7)        |

| †RxRDY                          | RxRDY Pin Delay from Center of Last Bit                                      |                    | 26                  | tcy               | (Note 7)        |

| TRANDY CLEAR                    | RxRDY ↓ from Leading Edge of RD                                              |                    | 400                 | ns                | (Note 7)        |

| t <sub>IS</sub>                 | Internal SYNDET Delay from Rising<br>Edge of RxC                             |                    | 26                  | toy               | (Note 7)        |

| tes                             | External SYNDET Set-Up Time After<br>Rising Edge of RxC                      | 16 t <sub>CY</sub> | tapd-icy            | ns                | (Note 7)        |

| t <sub>TxEMPTY</sub>            | TxEMPTY Delay from Center of Last Bit                                        |                    | 20                  | tcy               | (Note 7)        |

| twc                             | Control Delay from Rising Edge of WRITE (TxEn, DTR, RTS)                     |                    | 8                   | tcy               | (Note 7)        |

| tcr.                            | Control to READ Set-Up Time (DSR, CTS)                                       | 20                 |                     | tcy               | (Note 7)        |

'NOTE:

For Extended Temperature EXPRESS, use MIL 8251A electrical parameters.

#### A.C. CHARACTERISTICS (Continued)

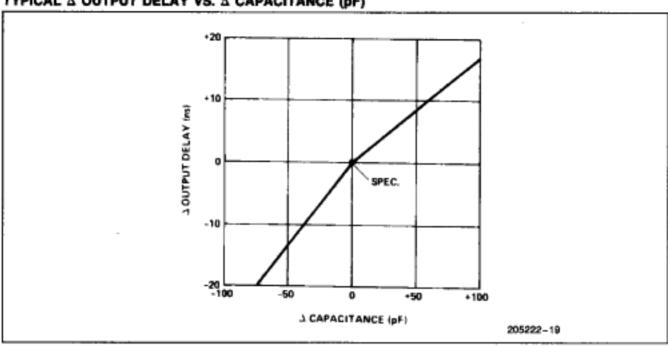

#### TYPICAL Δ OUTPUT DELAY VS. Δ CAPACITANCE (pF)

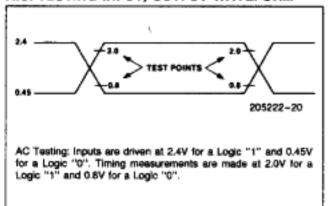

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

#### A.C. TESTING LOAD CIRCUIT

Figure 18

#### WAVEFORMS

#### SYSTEM CLOCK INPUT

## WAVEFORMS (Continued) 205222-23 205222-24 DATA BIT 9 (Rx BAUD COUNTER STARTS HERE) START BIT TRANSMITTER CLOCK AND DATA RECEIVER CLOCK AND DATA RxC (1x MODE) R<sub>K</sub> DATA Tx DATA TAC (1x MODE)

#### 9

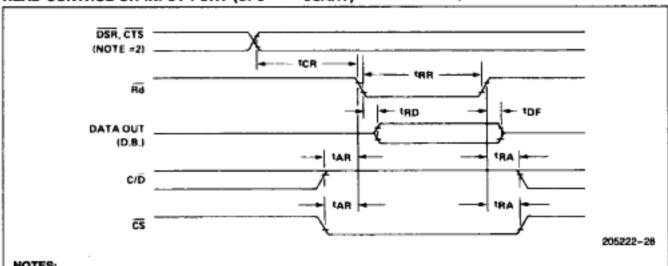

#### WAVEFORMS (Continued)

#### WRITE DATA CYCLE (CPU → USART)

#### READ DATA CYCLE (CPU ← USART)

#### WAVEFORMS (Continued)

#### WRITE CONTROL OR OUTPUT PORT CYCLE (CPU → USART)

#### READ CONTROL OR INPUT PORT (CPU ← USART)

#### NOTES:

- T<sub>WC</sub> includes the response timing of a control byte.

T<sub>CR</sub> includes the effect of CTS on the TxENBL circuitry.

#### WAVEFORMS (Continued)

# WAVEFORMS (Continued) Example Format - 5 Bit Character With Parity, 2 Sync Characters TRANSMITTER CONTROL AND FLAG TIMING (SYNC MODE) TAREADY STATUS BITT Ta READY ť To CAMPTY