### Single-Chip **System Controller**

GT-32011

Rev. 2, July 95 Preliminary

NOTE: Always contact Galileo Technology for possible updates before starting a design.

#### **FEATURES**

- Single Chip System Controller for the IDT R3051 family of processors

- Features facilitate the implementation of high-performance embedded control systems

- 16Mhz 33Mhz CPU interface to: R3041/51/52/71/81

- DRAM Controller

1 - 40 MB directly Device depth supported: 256K - 4M 1 - 3 banks directly Non-interleave

- ROM Controller

- 1 20MB

Address-space support bank size: 1-8MB Support for standard and burst ROMs Support for interleave or non interleave

- Direct Interface to External Agent/Coprocessor

- I/O Bus follows 8/16 Intel 80186 style

- I/O Controller

Two 8-bit and two 16-bit external channels DMA and non-DMA access for the 8-bit channels 8-32 packing and 32-8 unpacking logic for DMA access

Round robin arbitration

Programmable timing for I/O and control signals

Big and little endian support 16-32 packing and 32-16 unpacking for CPU/ External Co-processor accesses

**PCMCIA Support**

Through 16-bit I/O bus, using simple glue logic 16-bit to 32-bit packing and 32-bit to 16-bit unpacking Big and little endian support

256MB address space dedicated for 2 PCMCIA slots

Parallel Port

Supports control for reading and writing from a 16-bit parallel port

Centronics Interface

Bi-directional Centronics, compliant with IEEE1284 Supports DMA and CPU controlled transfers Supports the following modes: Compatible; Nibble; Byte; ECP; EPP

Interrupt Controller

6 external level interrupts (through the PIO pins) 10 internal interrupts Individual interrupt mask capability, enabling polling or interrupt-driven systems

General Purpose I/O

Six programmable Input (interrupts) or Output pins

- 24-bit Timer/Counter

- In-circuit testing capability

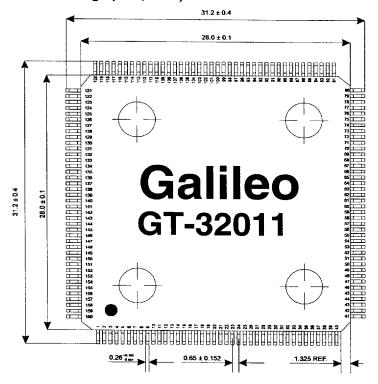

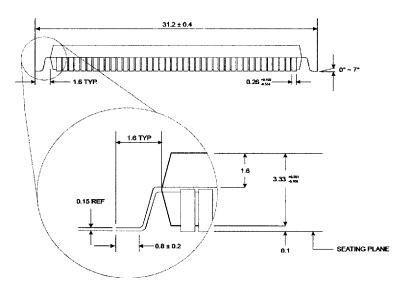

- Packaged in a 160-pin PQFP

1735 N. First St. #308, San Jose, CA 95112, Tel (408)451-1400, Fax (408)451-1404

#### GT-32011 Single Chip System Controller

#### **OVERVIEW**

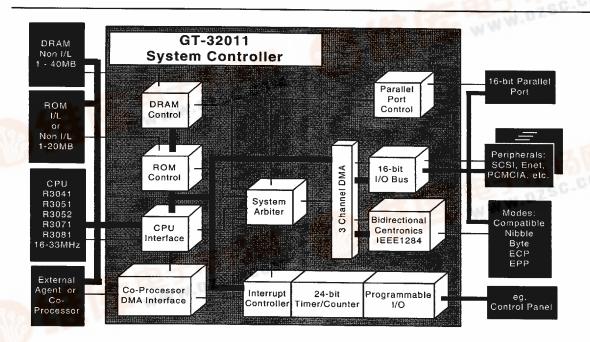

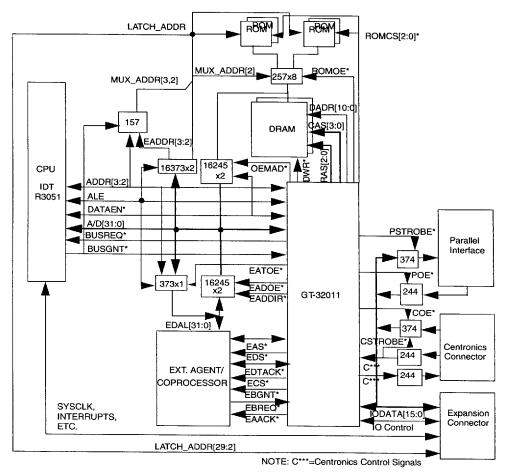

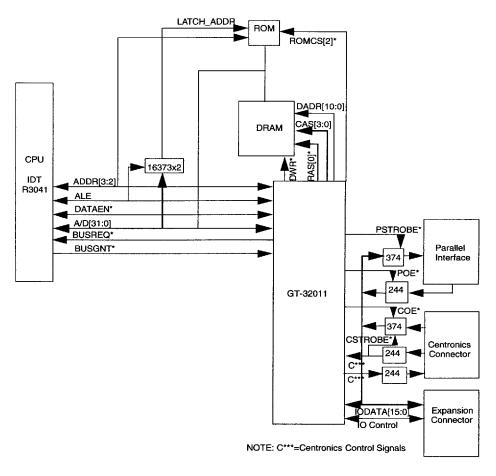

The GT-32011 is a single chip System Controller designed to complement IDT's R3051 family of 32-bit embedded processors. It has all the features necessary to implement high-performance, high-quality, embedded controllers. The GT-32011 is oriented towards data communications equipment, telecommunications equipment, office automation equipment, industrial and medical instrumentation, and industrial controllers.

The GT-32011 can move large amounts of data quickly without the need for processor intervention. It also achieves a significant reduction in system cost by its high level of integration. Additional savings come from the architecture of the I/O controller, which allows for the utilization of low cost peripheral components (disk controller, network controller, etc.), while attaining the higher level of performance only associated with costlier components.

Some of the architectural characteristics that result in very high performance include:

- incorporating a tightly coupled interface to a specific RISC processor architecture;

- minimizing latency to critical resources;

- partitioning the system in a balanced way to attain efficient use of shared resources;

- enabling several simultaneous operations in the system.

The GT-32011 is ideal for modular design of embedded control systems through a high level of programmability, and by incorporating the control logic for an industry standard interface to peripherals. This gives OEMs the ability to offer several products from the same basic design, as well as the ability to upgrade systems in the field.

#### 1 PIN INFORMATION

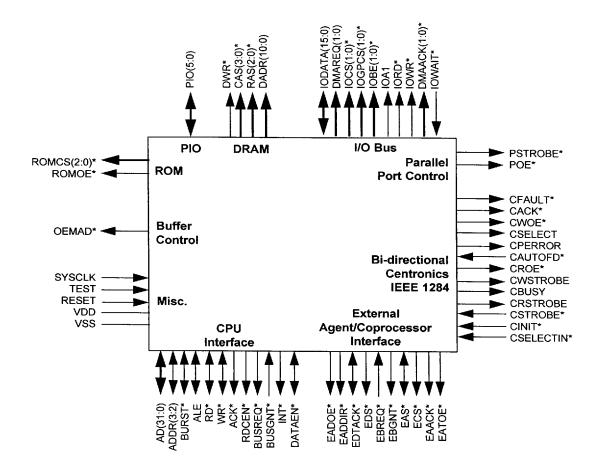

### 1.1 Logic Symbol

ma Pen

Fig. 1.1: Logic Symbol

### 1.2 Pin Assignment Table

| Pin Name      | Pull Up/<br>Pull Dn | Туре  | Drive | Description                                                                                                                                                                                                                                                            |  |

|---------------|---------------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU Interface |                     |       |       |                                                                                                                                                                                                                                                                        |  |

| A/D[31:0]     | P.U.                | 1/0   | 8mA   | Address/Data: Multiplexed address and data bus.                                                                                                                                                                                                                        |  |

|               |                     |       |       | In the Address phase: A/D[31:4] are address, A/D[3:0] are Byte Enable[3:0]. During Coprocessor Master cycles, A/D[3:2] contain address bits 3 and 2, and not Byte Enables.                                                                                             |  |

|               |                     |       |       | In the Data phase: Data[31:0]                                                                                                                                                                                                                                          |  |

| ADDR[3:2]     | P.U.                | I/O   | 4mA   | Non Multiplexed Address: Connected to the CPU ADDR[3:2]. In DMA cycles the GT-32011 drives these lines.                                                                                                                                                                |  |

| BURST*        | P.U.                | I/O   | 2mA   | Burst Transfer: Used only during read cycles, the BURST signal indicates that the current bus read is requesting a block of four continuous words from memory. The pin connects to the CPU's BURST/WRNEAR* signal. In DMA cycles the GT-32011 drives this signal HIGH. |  |

| ALE           | P.D.                | I/O   | 4mA   | Address Latch Enable: Used by the CPU to indicate that the A/D bus contains valid address information for the bus transaction. During Coprocessor DMA cycles, the GT-32011 asserts ALE to capture the address supplied by the Coprocessor.                             |  |

| SYSCLK        |                     | 1     |       | System Clock: Connected directly to the CPU SYSCLK* output.                                                                                                                                                                                                            |  |

| RD*           | P.U.                | I/O   | 2mA   | Read: Indicates a read access by the CPU. In DMA cycles the GT-32011 drives the signal HIGH.                                                                                                                                                                           |  |

| WR*           | P.U.                | I/O   | 2mA   | Write: Indicates a write access by the CPU or the Coprocessor. In a non-Coprocessor DMA cycle the GT-32011 drives this signal HIGH.                                                                                                                                    |  |

| ACK*          |                     | 0     | 2mA   | Acknowledge: Indicates that the memory system has sufficiently processed the bus transaction i.e. that the CPU may either terminate a write cycle or process read data.                                                                                                |  |

| RDCEN*        |                     | 0     | 2mA   | Read Buffer Clock Enable: Indicates to the CPU that there is valid data on the A/D bus.                                                                                                                                                                                |  |

| BUSREQ*       |                     | 0     | 2mA   | <b>Bus Request:</b> The GT-32011 requests the CPU bus which is required for I/O and Coprocessor DMA's.                                                                                                                                                                 |  |

| BUSGNT*       |                     | ı     |       | Bus Grant: Indicates that the CPU has relinquished the bus.                                                                                                                                                                                                            |  |

| INT*          |                     | 0     | 2mA   | Interrupt: "OR's" the internal and external interrupt sources.                                                                                                                                                                                                         |  |

| DATAEN*       |                     | 1/0   | 4mA   | <b>Data Enable:</b> indicates the data phase in CPU read cycles. In DMA the GT-32011 asserts DATAEN when the ROM/DRAM drives data onto A/D[31:0].                                                                                                                      |  |

| ROM           |                     | ····· |       |                                                                                                                                                                                                                                                                        |  |

| ROMCS[2:0]*   |                     | O     | 4mA   | ROM Chip Select: Select one of the 3 ROM banks. They can be connected to the ROM's Chip Select or Output Enable. ROMCS[2] is connected to the boot ROM, with a starting physical address 0x1fc00000.                                                                   |  |

ma Pan Garage

| Pin Name                                    | Pull Up/<br>Pull Dn | Туре | Drive | Description                                                                                                                                                                                                                         |

|---------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROMOE*                                      |                     | 0    | 4mA   | ROM Output Enable: Asserted when there is an access to any of the ROM banks. Used to output- enable the ROM data in systems where there is a buffer between ROM and DRAM data bus; eg. when using an interleaved ROM configuration. |

| DRAM                                        |                     |      |       |                                                                                                                                                                                                                                     |

| DADR[10:0]                                  |                     | 0    | 8ma   | DRAM Address: Multiplexed row and column address connected to the DRAM address.                                                                                                                                                     |

| RAS[2:0]*                                   |                     | 0    | 4mA   | Row Adress Select: Supports up to three banks of DRAM, connected to the RAS inputs of the DRAMs.                                                                                                                                    |

| CAS[3:0]*                                   |                     | 0    | 4mA   | Column Address Select: Connects a CAS to each of the four bytes in every bank.                                                                                                                                                      |

| DWR*                                        |                     | 0    | 12ma  | DRAM Write: Connects to the write pin of each of the DRAMs.                                                                                                                                                                         |

| Coprocessor/<br>External Agent<br>Interface |                     |      |       |                                                                                                                                                                                                                                     |

| EBREQ*                                      | P.U.                | l    |       | Ext. Agent Bus Request: An Ext. Agent bus request to make system resource access in master mode.                                                                                                                                    |

| EBGNT*                                      |                     | 0    | 2mA   | Ext. Agent Bus Grant: The GT-32011 asserts EBGNT* to grant the CPU bus to the Ext. Agent. Once the EBGNT* is asserted, it remains so until EBREQ* is deasserted.                                                                    |

| EAS*                                        | P.U.                | 1/0  | 2mA   | Ext. Agent Address Strobe:                                                                                                                                                                                                          |

|                                             |                     |      |       | Master Mode -The external agent indicates that it drives valid data on the A/D bus.                                                                                                                                                 |

|                                             |                     |      |       | Slave mode - The GT-32011 indicates that it drives valid data on the A/D bus.                                                                                                                                                       |

| EDS*                                        |                     | 0    | 2mA   | Ext. Agent Data Strobe:                                                                                                                                                                                                             |

|                                             |                     |      |       | Master mode - during Write indicates that there is valid data on the A/D bus. During Read indicates a request for data.                                                                                                             |

|                                             |                     |      |       | Slave mode - the GT-32011 drives EDS* to indicate that it is ready to accept data during reads or that valid data is available during writes on the A/D bus.                                                                        |

| EDTACK*                                     | P.U.                | I/O  | 2mA   | Ext. Agent Data acknowledge:                                                                                                                                                                                                        |

|                                             |                     |      |       | Master mode - The GT-32011 asserts EDTACK* to indicate that it is receiving or driving the requested data to/from the A/D bus.                                                                                                      |

|                                             |                     |      |       | Slave mode - The Ext. Agent asserts EDTACK* to signal that it has supplied or received data on its bus.                                                                                                                             |

| EAACK*                                      |                     | 0    | 2mA   | Ext. Agent Address Acknowledge: The GT-32011 asserts EAACK* one clock after asserting ALE for the Ext. Agent. This insures that the Ext. Agent continues driving the address until latched by the system.                           |

| ECS*                                        |                     | 0    | 2mA   | Ext. Agent Chip Select: When the CPU accesses the Ext. Agent, the GT-32011 asserts ECS*. It is active one clock before GT-32011 asserts EAS*.                                                                                       |

| Pin Name      | Pull Up/<br>Pull Dn | Туре | Drive | Description                                                                                                                                                   |  |

|---------------|---------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EADOE*        |                     | 0    | 4mA   | Ext. Agent A/D Output Enable: The GT-32011 asserts EADOE* when the Ext. Agent drives the address to the A/D bus, and in the data phases of the Ext. Agent.    |  |

| EADDIR*       |                     | 0    | 4mA   | Ext. Agent A/D Direction: The GT-32011 asserts EADDIR* (LOW) when the Ext. Agent drives the A/D bus.                                                          |  |

| EATOE*        |                     | 0    | 4mA   | Ext. Agent Address To Output Enable: The GT-32011 asserts EATOE* in the address phase of cycles in which the CPU accesses the Ext. Agent.                     |  |

| Buffer        |                     |      |       |                                                                                                                                                               |  |

| Control       |                     |      |       |                                                                                                                                                               |  |

| OEMAD*        |                     | 0    | 4mA   | Output Enable between Memory and A/D: Output enable for the data path transceiver, between the memory system and the A/D bus.                                 |  |

| I/O Bus       |                     |      |       |                                                                                                                                                               |  |

| IODATA[15:0]  | P.U.                | I/O  | 8mA   | Input/Output Data: Bidirectional 16-bit I/O Data bus.                                                                                                         |  |

| IORD*         |                     | 0    | 12mA  | Input/Output Read: Active during Read from an I/O device.                                                                                                     |  |

| IOWR*         |                     | 0    | 12mA  | Input/Output Write: Active during Write to an I/O device.                                                                                                     |  |

| IOCS[1:0]*    |                     | 0    | 2mA   | Input/Output Chip Selects: Chip selects for 8 bit I/O channels 0 and 1.                                                                                       |  |

| IOGPCS[1:0]*  |                     | 0    | 2mA   | Input/ Output Chip Selects: Chip select outputs for 16 bit I/O channels 0 and 1.                                                                              |  |

| DMAREQ[1:0]   | P.D.                | 1    |       | DMA Request: Requesting DMA service on channels 0 and 1.                                                                                                      |  |

| DMAACK*[1:0]* |                     | 0    | 2mA   | <b>DMA acknowledge:</b> Indicating that DMA access is granted on channels 0 and 1.                                                                            |  |

| IOA1          |                     | 0    | 8mA   | Input/Output Address bit 1: Provides a half word (16 bit) address on the I/O bus.                                                                             |  |

| IOBE[1:0]*    |                     | 0    | 2mA   | Input/Output Byte Enable: Indicates which byte data bus is valid on the 16 bit I/O bus.                                                                       |  |

| IOWAIT*       | P.U.                | 1    |       | Input/Output Wait: Indicates to the GT-32011 that a transfer cycle on the I/O bus needs to be extended.                                                       |  |

| PIO[5:0]      | P.U.                | 1/0  | 8mA   | Programmable Input/Output: Individually programmed pins for inputs, interrupt inputs or outputs.                                                              |  |

| Bidirectional |                     |      |       |                                                                                                                                                               |  |

| Centronics    |                     |      |       |                                                                                                                                                               |  |

| CWOE*         |                     | 0    | 2mA   | Centronics Write Output Enable: Controls the Output Enable signal of the data register -from the peripheral to the host.                                      |  |

| CROE*         |                     | 0    | 2mA   | Centronics Read Output Enable: Controls the OE of the Centronics external register in the direction from the host to the peripheral (to the IODATA(7:0) bus). |  |

| CWSTROBE      |                     | 0    | 2mA   | Centronics Write Strobe: Clocks data from the IODATA(7-0) into the Centronics register (from peripheral to host).                                             |  |

| CRSTROBE      |                     | 0    | 2mA   | Centronics Read Strobe: Clocks data from the host into the Centronics register (from host to peripheral).                                                     |  |

| CACK*  O 2mA Centronics acknowledge: Detailed description in section 4.3 the IEEE P1284 D2.00 specification.  CBUSY  O 2mA Centronics Busy: Detailed description in section 4.4 of the IEEE P1284 D2.00 specification.  CPERROR  O 2mA Centronics Printer Error: detailed description in section 4.5 the IEEE P1284 D2.00 specification.  CSELECT  O 2mA Centronics Select: Detailed description in section 4.6 of the IEEE P1284 D2.00 specification.  CAUTOFD*  P.U. I Centronics Autofeed: Detailed description in section 4.7 of the IEEE P1284 D2.00 specification.  CINIT*  P.U. I Centronics Initialize: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.  CFAULT*  O 2mA Centronics Fault: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.  CFAULT*  O 2mA Centronics Fault: Detailed description in section 4.10 of the IEEE P1284 D2.00 specification.  CSELECTIN*  P.U. I Centronics Select Input: Detailed description in section 4.11 the IEEE P1284 D2.00 specification.  Parallel Port Control  PSTROBE*  O 2mA Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE*  O 2mA Parallel Output Enable: When active (LOW), it controls the option of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET*  I Reset: Active low-will reset the GT-32011 to the initial state.                              | Pin Name   | Pull Up/<br>Pull Dn | Туре | Drive | Description                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBUSY  O 2mA  Centronics Busy: Detailed description in section 4.4 of the IEEE P1284 D2.00 specification.  CPERROR  O 2mA  Centronics Printer Error: detailed description in section 4.5 the IEEE P1284 D2.00 specification.  CSELECT  O 2mA  Centronics Select: Detailed description in section 4.6 of the IEEE P1284 D2.00 specification.  CAUTOFD*  P.U.  I Centronics Autofeed: Detailed description in section 4.7 of the IEEE P1284 D2.00 specification.  CINIT*  P.U.  I Centronics Initialize: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.  CFAULT*  O 2mA  Centronics Initialize: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.  CSELECTIN*  P.U.  I Centronics Fault: Detailed description in section 4.10 of the IEEE P1284 D2.00 specification.  CSELECTIN*  P.U.  I Centronics Select Input: Detailed description in section 4.11 the IEEE P1284 D2.00 specification.  CSELECTIN*  P.U.  I Centronics Select Input: Detailed description in section 4.11 the IEEE P1284 D2.00 specification.  Parallel Port Control  PSTROBE*  O 2mA  Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE*  O 2mA  Parallel Output Enable: When active (LOW), it controls the count of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST  P.D.  I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET*  I Reset: Active low-will reset the GT-32011 to the initial state. | CSTROBE*   | P.U.                | ı    |       | Centronics Strobe: Detailed description in section 4.1 of the IEEE P1284 D2.00 specification.                                                                  |

| Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CACK*      |                     | 0    | 2mA   | <b>Centronics acknowledge:</b> Detailed description in section 4.3 of the IEEE P1284 D2.00 specification.                                                      |

| the IEEE P1284 D2.00 specification.  CSELECT O 2mA Centronics Select: Detailed description in section 4.6 of the IEEE P1284 D2.00 specification.  CAUTOFD* P.U. I Centronics Autofeed: Detailed description in section 4.7 of the IEEE P1284 D2.00 specification.  CINIT* P.U. I Centronics Initialize: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.  CFAULT* O 2mA Centronics Fault: Detailed description in section 4.10 of the IEEE P1284 D2.00 specification.  CSELECTIN* P.U. I Centronics Select Input: Detailed description in section 4.11 the IEEE P1284 D2.00 specification.  Parallel Port Control  PSTROBE* O 2mA Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE* O 2mA Parallel Output Enable: When active (LOW), it controls the oput enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET* I Reset: Active low-will reset the GT-32011 to the initial state.  VDD +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                  | CBUSY      |                     | 0    | 2mA   | Centronics Busy: Detailed description in section 4.4 of the IEEE P1284 D2.00 specification.                                                                    |

| CAUTOFD* P.U. I Centronics Autofeed: Detailed description in section 4.7 of the IEEE P1284 D2.00 specification.  CINIT* P.U. I Centronics Initialize: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.  CFAULT* O 2mA Centronics Fault: Detailed description in section 4.10 of the IEEE P1284 D2.00 specification.  CSELECTIN* P.U. I Centronics Select Input: Detailed description in section 4.10 of the IEEE P1284 D2.00 specification.  Parallel Port Control  PSTROBE* O 2mA Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE* O 2mA Parallel Output Enable: When active (LOW), it controls the opten enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET* I Reset: Active low-will reset the GT-32011 to the initial state.  VDD +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPERROR    |                     | 0    | 2mA   | Centronics Printer Error: detailed description in section 4.5 of the IEEE P1284 D2.00 specification.                                                           |

| IEEE P1284 D2.00 specification.  CINIT* P.U. I Centronics Initialize: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.  CFAULT* O 2mA Centronics Fault: Detailed description in section 4.10 of the IEEE P1284 D2.00 specification.  CSELECTIN* P.U. I Centronics Select Input: Detailed description in section 4.11 the IEEE P1284 D2.00 specification.  Parallel Port Control  PSTROBE* O 2mA Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE* O 2mA Parallel Output Enable: When active (LOW), it controls the oput enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET* I Reset: Active low-will reset the GT-32011 to the initial state.  VDD +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CSELECT    |                     | 0    | 2mA   |                                                                                                                                                                |

| CFAULT*  O 2mA Centronics Fault: Detailed description in section 4.10 of the IEEE P1284 D2.00 specification.  CSELECTIN* P.U. I Centronics Select Input: Detailed description in section 4.11 the IEEE P1284 D2.00 specification.  Parallel Port Control  PSTROBE* O 2mA Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE* O 2mA Parallel Output Enable: When active (LOW), it controls the oput enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET* I Reset: Active low-will reset the GT-32011 to the initial state.  VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CAUTOFD*   | P.U.                | 1    |       | Centronics Autofeed: Detailed description in section 4.7 of the IEEE P1284 D2.00 specification.                                                                |

| CSELECTIN*   P.U.   I   Centronics Select Input: Detailed description in section 4.11   the IEEE P1284 D2.00 specification.    Parallel Port Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CINIT*     | P.U.                | ı    |       | Centronics Initialize: Detailed description in section 4.9 of the IEEE P1284 D2.00 specification.                                                              |

| Parallel Port Control  PSTROBE*  O 2mA  Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE*  O 2mA  Parallel Output Enable: When active (LOW), it controls the oput enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST  P.D.  I  Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET*  I Reset: Active low-will reset the GT-32011 to the initial state.  VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CFAULT*    |                     | 0    | 2mA   |                                                                                                                                                                |

| PSTROBE*  O 2mA Parallel Strobe: Clocks 8-bit or 16-bit parallel data from IODATA[15:0]  POE*  O 2mA Parallel Output Enable: When active (LOW), it controls the oput enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET*  I Reset: Active low-will reset the GT-32011 to the initial state.  VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CSELECTIN* | P.U.                | ı    |       | Centronics Select Input: Detailed description in section 4.11 of the IEEE P1284 D2.00 specification.                                                           |

| POE*  O 2mA  Parallel Output Enable: When active (LOW), it controls the oput enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST  P.D.  I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET*  I Reset: Active low-will reset the GT-32011 to the initial state.  VDD  +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                     |      |       |                                                                                                                                                                |

| put enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]  Misc.  TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET* I Reset: Active low-will reset the GT-32011 to the initial state.  VDD +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PSTROBE*   |                     | 0    | 2mA   |                                                                                                                                                                |

| TEST P.D. I Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  RESET* I Reset: Active low-will reset the GT-32011 to the initial state.  VDD +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | POE*       |                     | 0    | 2mA   | Parallel Output Enable: When active (LOW), it controls the output enable of a data buffer for8-bit or 16-bit wide parallel data into IODATA[15:0]              |

| RESET*  I Reset: Active low-will reset the GT-32011 to the initial state.  VDD  Active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND).  Reset: Active low-will reset the GT-32011 to the initial state.  +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Misc.      |                     |      |       |                                                                                                                                                                |

| VDD +5V (+/-5%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TEST       | P.D.                | ı    |       | Master Output Enable: When TEST is HIGH and RESET* is active, ALL the device outputs and I/Os are tri-stated (in a system, TEST should be pulled down to GND). |

| 107 (17 070)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                     |      |       | Reset: Active low-will reset the GT-32011 to the initial state.                                                                                                |

| VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                     |      |       | +5V (+/-5%)                                                                                                                                                    |

| Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VSS        |                     |      |       | Ground                                                                                                                                                         |

NOTE: Pull Up/Pull Dn designates those pins with internal Pull Up (P.U.) or Pull Down (P.D.) resistors

ma Pe

#### 2 FUNCTIONAL DESCRIPTION

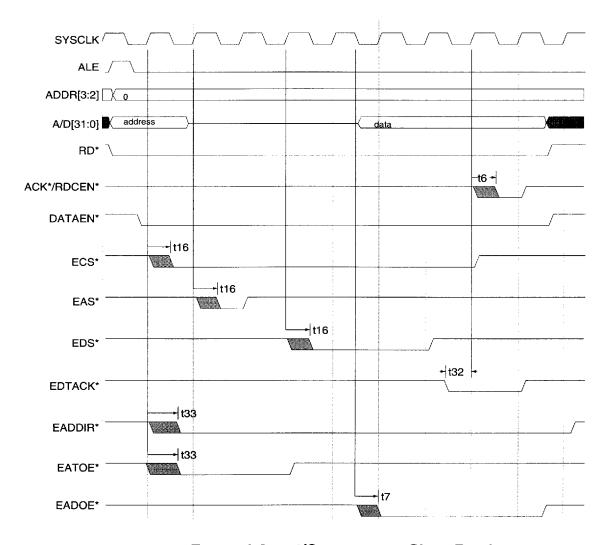

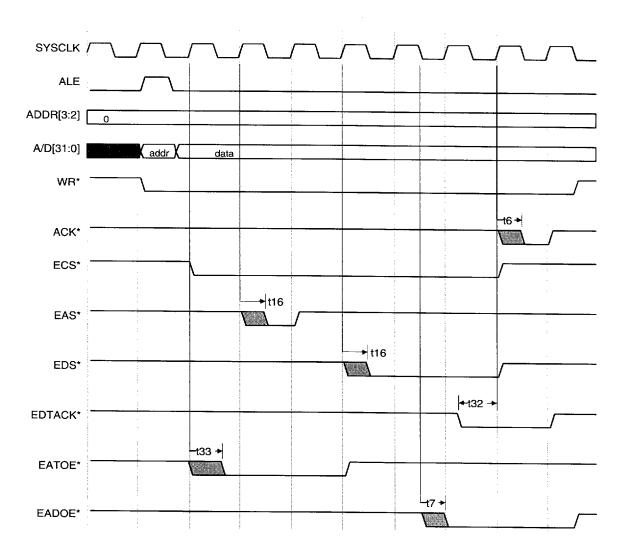

#### 2.1 Processor Interface

The GT-32011 has a glueless interface to the IDT R3041/51/52/71/81 family of RISC processors. It operates as a slave - supporting CPU access to memory and I/O devices, or as a master - handling access on the A/D bus.

As a slave the GT-32011 supports processor single transfer read or write, and burst read accesses. It supports processor access to the ROM, DRAM, devices on the I/O bus, the external agent/coprocessor and the GT-32011 internal registers. Burst read is supported only for DRAM or ROM read accesses. ACK\* and RDCEN\* timing is fixed for GT-32011 registers. DRAM access can be extended by one clock, and access timing for ROM and I/O is programmable.

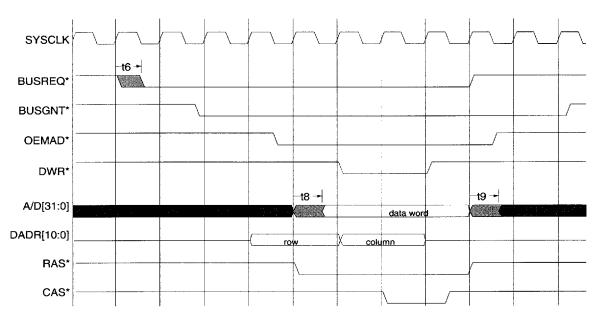

As a master the GT-32011 will request the bus by asserting BUSREQ\* when a DMA source (internal or external) needs to transfer data to or from the DRAM / ROM / I/O Channel. The priority between the DMA sources is in the following descending order: access in process; I/O DMA; external agent/coprocessor DMA.

In the default state, when there is no DMA request, the bus is owned by the CPU. The CPU will get ownership of the A/D bus for at least one cycle after three DMA accesses.

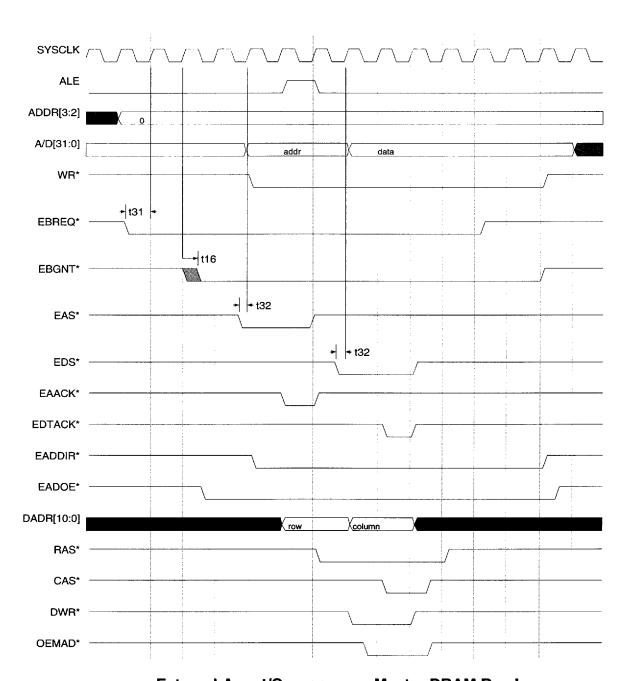

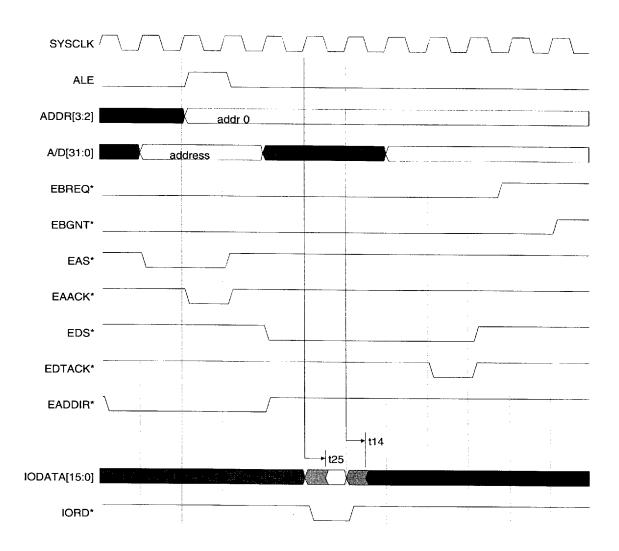

# 2.2 Co-Processor/External Agent Interface

The GT-32011 has a glueless interface to an external agent or coprocessor. It supports slave and master modes of operation. As a slave it supports the processor read and write accesses to the coprocessor, and as a master it enables coprocessor access to the DRAM, ROM, and 16 bit I/O bus. The GT-32011 directly controls the data buffers and the address needed to isolate the external agent/coprocessor from the A/D bus.

The GT-32011 decodes CPU accesses to the coprocessor and asserts ECS\*, EAS\* and EDS\*. The address is latched into an external transparent latch (373-type) when the processor asserts ALE and driven into the a coprocessor bus by EATOE\*. Data is driven to or from the coprocessor by transceivers controlled by EADDIR and EADOE. To end a coprocessor cycle the GT-32011 asserts RDCEN\* and ACK\* to the CPU, when the coprocessor asserts EDTACK\*.

In coprocessor master mode, the coprocessor requests the bus by asserting EBREQ\*. The GT-32011 will grant the bus by asserting EBGNT\* (provided no other DMA device has requested the bus and it was granted by the

CPU to the GT-32011). The coprocessor will assert EAS\* and EDS\* to initiate an access to a system resource (e.g. DRAM). The GT-32011 will assert EADOE\* and EADDIR\* to drive the coprocessor address and ALE to latch it. In the data phase it will assert EADDIR\* and EADOE\* according to the access direction (Read or Write). To end the cycle the GT-32011 will assert EDTACK\* to the coprocessor.

The coprocessor will release the bus by deasserting EBREQ\* when it does not require the bus any longer.

A coprocessor access to the DRAM takes 5 clocks from EAS\* to EDTACK\*. One clock can be added to this interval (for frequencies above 25Mhz) using the EAExtCas bit in the DRAM control register if necessary.

The coprocessor/external agent interface can support both multiplexed bus and non-multiplexed bus agents. By using glue logic, it is possible to interface to an even greater variety of buses and coprocessors.

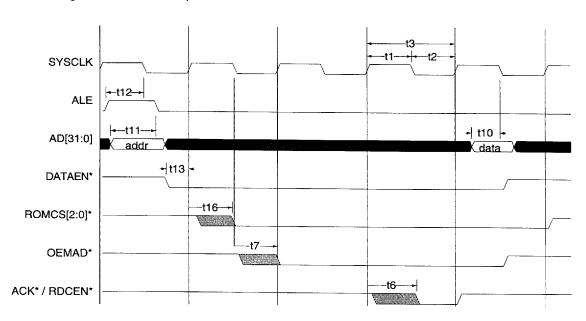

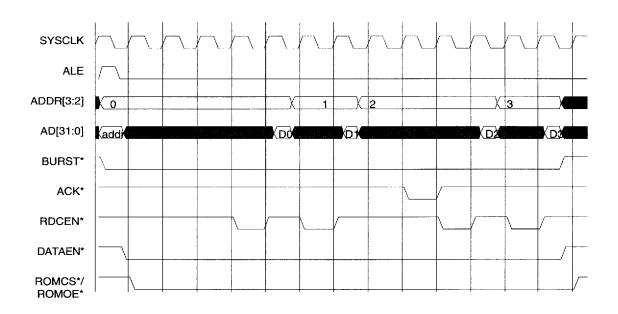

#### 2.3 ROM

The ROM controller supports up to 20 Mbyte of memory with several device types and system configurations. To support these system and device options, the assertion time of RDCEN\* and ACK\* by the GT-32011GT-32011 can be programmed, thus accommodating different types of memory architectures, including standard ROMs, interleaved ROMs, and burst ROMs. There are three CS signals to support up to three banks of ROM. The ROM can be either non interleaved or interleaved - composed of 2 banks of ROM differentiated by ADDR[2]. ROMCS[2]\* controls the boot bank and has a fixed address space of 4 Mbyte. Address space for ROMCS[1]\* and ROMCS[0]\* is programmable to 1, 2, 4, or 8 Mbyte. The GT-32011 puts the 3 ROM bank address ranges in a contiguous address space, ie. the start address of the next ROMCS[x]\* will follow the last address of the previous ROMCS[x-1]\*. For interleaved support, ROMOE\* is provided to control the OE of the interleave multiplexer. The GT-32011 also supports burst ROMs and the capability to write to the ROM space (for Flash or debug).

After reset, the GT-32011 is configured with the maximum number of wait states between each data transfer (16 clocks between each RDCEN\*) and 64 clocks between ROMCS[x]\* to ACK\*. The initial (reset) space size for ROMCS[1]\* and ROMCS[0]\* is 1 Mbyte, and 4Mbytes for ROMCS[2]\*.

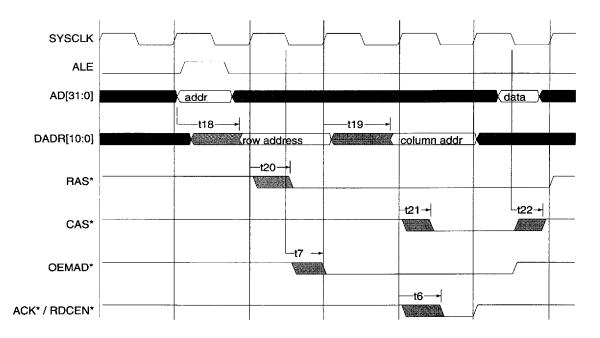

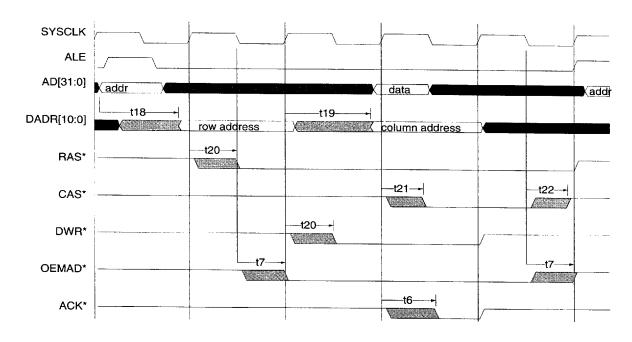

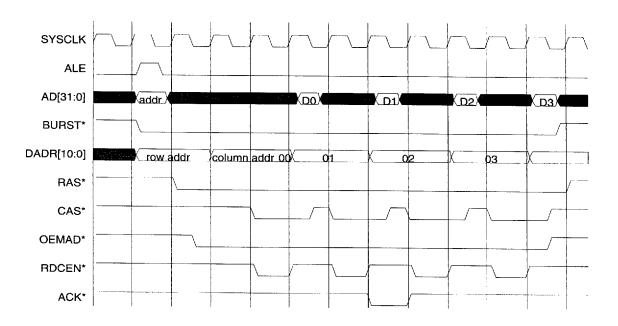

#### **2.4 DRAM**

The DRAM controller supports directly 1 to 40 Mbytes of DRAM, with up to three non-interleaved banks. The address space starts at physical address 0. The DRAM

device types supported have the following attributes: page mode, early write, and CAS before RAS refresh. The DRAM controller supports single transfer reads and writes and burst reads. Various DRAM device depths are supported and the address space is continuous for the selected configuration. The DRAM controller can be configured to support different device depth for the base bank (RAS 0) and the extension banks (RAS 1 and RAS 2). For systems running at 33Mhz there is an option to extend the CAS signal by an additional cycle. Since a coprocessor might sample data on the rising edge of SYSCLK, and the CPU on the falling edge, for systems above 20Mhz it may be necessary to extend the CAS by one cycle for coprocessor accesses. To minimize the refresh penalty it is recommended to program the refresh frequency to the value of SYSCLK.

The initial values of the GT-32011 at reset are shown in section 3.12.

#### 2.5 PIO Port

Each of the PIO[5:0] pins can be individually programmed to be an output or input pin by writing to the PIO Control register. When programmed as an input pin it can be used as a level (active LOW) interrupt. The PIO pins are synchronized and pulled up internally.

At reset, all PIOs are initialized as inputs.

#### 2.6 Interrupt Controller

Each interrupt source on the GT-32011 is maskable. The Cause register bit will reflect the cause of the interrupt, and writing a '0' into it will acknowledge the internal interrupt.

The external interrupts - PIO[5:0], are acknowledged at the source of the interrupt (the interrupt flag is set when PIO is inactive), the corresponding bits in the Interrupt Cause register are read only.

At reset, all interrupts are masked in the mask register.

### 2.7 Timer/Counter

The general purpose timer/counter can be programmed to function as a timer or as a counter. As a counter, it will cause an interrupt and stop counting when it reaches terminal count. Writing a new value to the counter will start the counter if the Enable bit is active. As a timer on terminal count, it will cause an interrupt, reload with the value stored in the Timer/Counter Value register and continue to count.

The Timer/Counter counting is enabled or disabled by the

enable bit. The value n should be written to the Counter in order to count to n clocks. At reset, the counter is disabled.

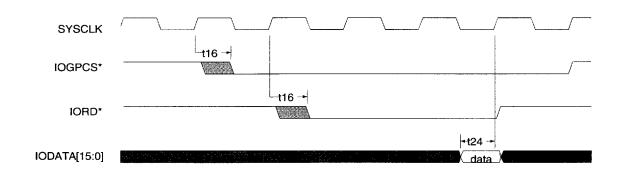

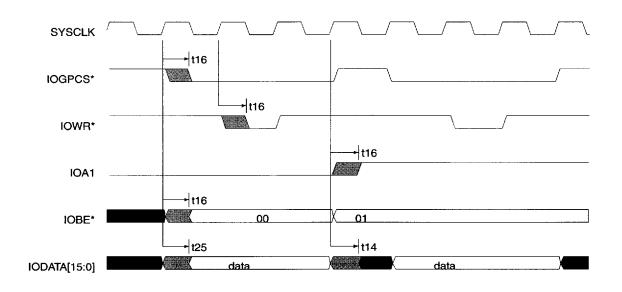

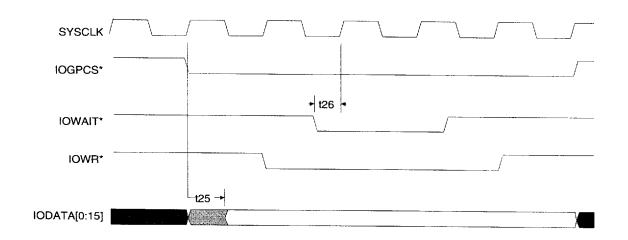

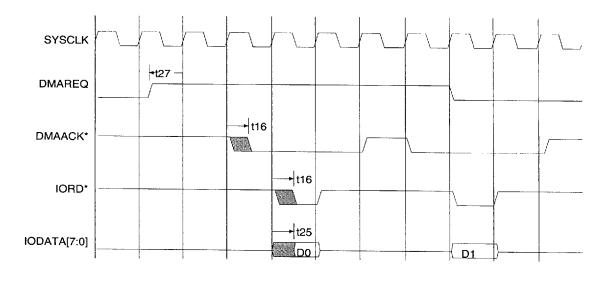

#### 2.8 I/O Bus

The GT-32011 supports two 8-bit (IOCS[1:0]\*) and two 16-bit (IOGPCS[1:0]\*) external I/O channels, that share the IODATA[15:0] pins. The two 8-bit I/O channels and the first 16-bit I/O channel (IOGPCS[0]\*) each has a 16 Mbyte address space. The second 16 bit I/O channel (IOGPCS[1]\*) has a 256Mbyte address space.

Timing of the control signals to an I/O channel is programmable. The user can specify the length of IORD\* and IOWR\* signals. The IOCS[1:0]\*, IOGPCS[1:0]\* or DMAACK[1:0]\* are asserted one cycle before the IORD\* or IOWR\* signals become active, and remain active for one cycle after IORD\* or IOWR\* are de-asserted. RDCEN\* and ACK\* will be asserted by the GT-32011 to end a processor (or EDTACK\* to end a coprocessor I/O cycle).

#### 8-bit I/O Channels

The GT-32011 supports processor byte accesses (reads and writes) to devices located on the two 8 bit I/O channels. These accesses can be made using any of the four bytes on the 32 bit data bus, the GT-32011 will transfer the correct byte (according to the 4 Byte Enables) to the 8 bit I/O bus (IODATA[7:0]).

The GT-32011 I/O channel unit operates as a DMA controller with the two 8 bit I/O channels. DMA operations between I/O devices and the DRAM are supported. Eight bit data is packed or unpacked during DMA access into a 32 bit register for I/O DMA read or write respectively.

Processor requests have priority over DMA requests. The priority for DMA operations is round robin for the Centronics and the two external 8-bit DMA engines. DMAREQ[1:0] can be masked by writing '0' to the enable bit of the channel. A channel will not participate in the arbitration if the channel is disabled or if the I/O BIU (Bus Interface Unit) is owned by another channel. The I/O BIU is emptied into memory in a DMA read access if the I/O BIU is full, or if there is no DMA request (DMAREQ[1:0]) from the channel which owns the I/O BIU for a time out period or the byte count reaches zero. In the write direction if the DMAREQ from the channel that owns the I/O BIU is not active for a time out period, and the I/O BIU is not empty, arbitration will resume on the I/O bus. The time out period is set to 32 clocks.

#### 16-bit I/O Channel s

The GT-32011 supports processor and coprocessor

accesses (reads and writes) to devices located on the two 16-bit I/O channels.

For 16-bit devices, the CPU can read or write to any byte or half word. Processor or coprocessor access to the 16bit I/O channels with any combination of byte enables active, will be performed in two consecutive I/O cycles in case of 3 or 4 byte accesses. In the two cycles, data will be packed or unpacked from a 32-bit register for an I/O read or write respectively. Conversion between big and little endian is supported for 16-bit devices.

The following signals support a parallel port interface: a) Parallel Strobe (PSTROBE\*) - Clocks data out from IODATA[15:0] and b) Parallel Output Enable (POE\*) controls the output enable of an external buffer.

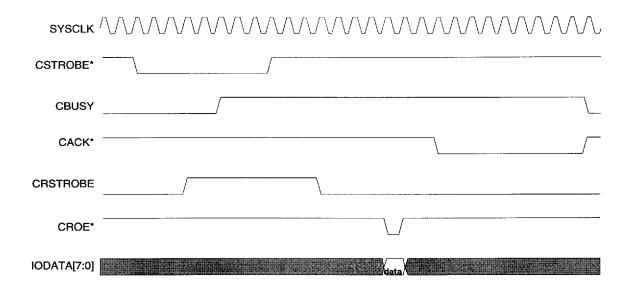

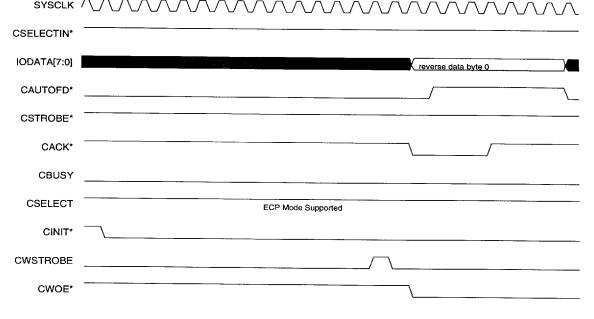

#### 2.9 Centronics IEEE 1284 Communication

NOTE: Due to the scope of this data sheet, it would be impossible to cover every aspect of the IEEE 1284 bidirectional Centronics standard. Designers are urged to study the IEEE1284 Rev. 2 specification.

The Centronics implementation meets the IEEE 1284 definition of a compliant device. It supports the following modes: Compatible, Nibble, Byte, ECP and EPP, as well as the negotiation necessary for transition between different modes. Support for the Compatible mode includes the following three variations: Standard, IBM Epson, and Classic. There are two ways to handle the Centronics protocol: In the first option, data is transferred in DMA fashion and is only applicable in the Compatible, ECP, and EPP modes. The second option is interrupt driven, and applies to all modes. That is, Byte and Nibble modes

are only interrupt driven. There is support for special character detection in the Centronics incoming data. Control data characters like ^C or ^T can be detected and the CPU will be interrupted.

#### Negotiation

The GT-32011 defaults after reset to Compatible mode. The negotiation phase starts when the host sets CSE-LECTIN\* HIGH and CAUTOFD\* LOW. The GT-32011 interrupts the CPU by asserting the CentWrInt interrupt. The CPU interrupt routine includes reading the extensibility request value from the Centronics External register (0a000000), and writing to the Centronics Control register to specify the supported mode. Note that the interpretation of the CenRdInt and CentWrInt interrupts, and the interrupt handler response, will be different in each mode. Table 2.1 summarizes the values of host requests and the CPU interrupt routine response.

#### Compatible Mode

The CPU needs to configure the Compatible mode to one of the three supported modes: IBM, Classic or Standard, and to a data transfer option (DMA or interrupt per byte). Setting the modes and options is done by writing to the mode register (values are specified in the Centronics Mode register table).

In the interrupt per byte mode, the CPU will read data from the Centronics External register every time it responds to the CentRdInt interrupt. In DMA mode the CPU will initialize the DMA registers (addresses 1d0000a0, 1d000080 & 1d00098) before starting the DMA operation. The GT-32011 will assert interrupt Cent-DMAInt when the DMA counter will reach terminal count.

|     | •       |                     |          |

|-----|---------|---------------------|----------|

| est | Request | Interrupt response: | Interrup |

Table 2.1: Interrupt Responses During Negotiation Phase

| Request<br>mode    | Request<br>value | Interrupt response:<br>mode supported<br>value | Interrupt response:<br>mode not<br>supported value |

|--------------------|------------------|------------------------------------------------|----------------------------------------------------|

| Extensibility link | 1000 0000        | 1110                                           | 0111                                               |

| first byte         | XXXX XXXX        | 1xxx                                           | 0110                                               |

| EPP                | 0100 0000        | 1100                                           | 0111                                               |

| ECP with RLE       | 0011 0000        | 1011                                           | 0111                                               |

| ECP                | 0001 0000        | 1011                                           | 0111                                               |

| Device ID:         |                  |                                                |                                                    |

| -Nibble            | 0000 0100        | 1001                                           | 0111                                               |

| -Byte              | 0000 0101        | 1010                                           | 0111                                               |

| -ECP with RLE      | 0001 0100        | 1011                                           | 0111                                               |

| -ECP without RLE   | 0011 0100        | 1011                                           | 0111                                               |

| Byte               | 0000 0001        | 1010                                           | 0111                                               |

| Nibble             | 0000 0000        | 0001                                           | 1111                                               |

A host request to return to compatibility mode from any of the other modes is indicated to the CPU by the assertion of the CentRstInt interrupt.

#### Nibble Mode

The GT-32011 will interrupt the CPU by asserting Cent-Wrint when the host requests a byte transfer. The CPU will respond by writing data to the Nibble data register. The GT-32011 sends the byte to the host over the control lines in two consecutive nibble transactions.

#### **Byte Mode**

The GT-32011 will interrupt the CPU by asserting Cent-WrInt when the host requests a byte transfer. The CPU will respond by writing data to Centronics External register.

#### **Extensibility Link**

Assertion of CentWrInt interrupt while in Compatibility mode indicates to the CPU an extensibility request. The CPU will read from the Centronics External register the extensibility request value, and write to the control register the next mode and proper response.

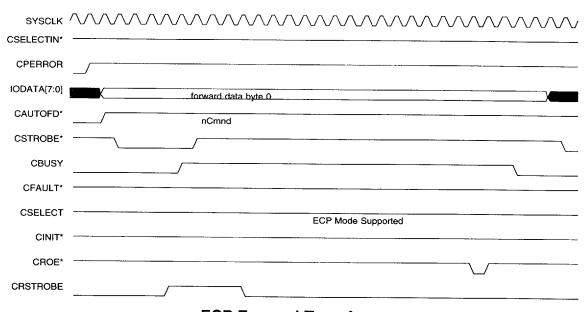

#### **ECP Mode**

DMA and interrupt per byte options are supported for the ECP mode.

In the interrupt per byte option, the GT-32011 will assert CentRdInt for host read requests, and will assert Cent-WrInt for host write requests. The CPU will read or write from the Centronics External register in response to the interrupt.

In reverse transfer, in response to CentWrInt, the CPU must first write to the Centronics status register (to the Busy bit). This indicates whether the CPU sends a command or data byte, and then write the data to the Centronics External register.

In forward transfer, in response to CentRdInt the CPU needs to read from the Centronics host register (Autofeed bit) to know whether the host is sending data or command, and then read the data from the Centronics register.

RLE compression is supported only in interrupt per byte mode

In the DMA transfer option, data will be transferred by the DMA as long as the direction of the host requests matches the direction of the DMA. CentWrInt will be asserted when the host requests data and the DmaDir bit in the Mode register indicates a read direction (From the IEEE1284 port to memory). CentRdInt will be asserted when the host sends data and the DmaDir bit indicates a write direction or when the host sends a command byte.

#### **EPP Mode**

DMA and interrupt per byte options are supported for the EPP mode.

In the interrupt per byte option, the GT-32011 will assert CentRdInt for host read requests, and will assert Cent-WrInt for host write requests. The CPU will read or write from the Centronics External register in response to the interrupt. It will distinguish between data and address by the contents of the strobe Selectin and AutoFd bits in the host

buffer.

In the DMA transfer option, data will be transferred by the DMA as long as the direction of the host requests matches the direction of the DMA. CentWrInt will be asserted when the host requests data

and the DmaDir bit in the Mode register indicates a read direction (from the Centronics port to memory) or when the host asks for an address byte. CentRdInt will be asserted when the host sends data and the DmaDir bit indicates a write direction or when the host sends an address byte.

#### **CPU Control**

This mode enables the CPU to set the values of the Centronics status register, and communicate with the host in compatible mode.

#### Character Detection.

The value of the three CentDetect 8-bit registers is constantly compared to the Centronics incoming data. When a match occurs the CPU is interrupted. Characters as ^C or ^T can be detected during Centronics DMA operations and the CPU can respond without the need to wait to the end of the DMA operation.

#### **Programmable Timing**

To allow for higher than specified (by the IEEE1284 standard) data rates, the minimum delay can be programmed to values lower than the minimum required by this standard.

### **3 REGISTER TABLES**

#### 3.1 Register Map

| Description            | Address    | Description              | Address    |

|------------------------|------------|--------------------------|------------|

| ROM Configuration      | 0x1d000000 | DMA Centronics Count     | 0x1d000098 |

| Reserved               | 0x1d000020 | I/O Channel Timing       | 0x1d0000a0 |

| PIO Value              | 0x1d000040 | Reserved                 | 0x1d0000c0 |

| PIO Control            | 0x1d000044 | Reserved                 | 0x1d0000c4 |

| PIO Read Pins          | 0x1d00005c | Reserved                 | 0x1d0000c8 |

| Timer/Counter Value    | 0x1d000048 | Reserved                 | 0x1d0000cc |

| Timer/Counter Control  | 0x1d00004c | Reserved                 | 0x1d0000do |

| Interrupt Cause        | 0x1d000050 | Centronics Status        | 0x1d000100 |

| Interrupt Mask         | 0x1d000054 | Centronics Control       | 0x1d000104 |

| Interrupt Write        | 0x1d000060 | Centronics Nibble Data   | 0x1d000108 |

| Test                   | 0x1d000064 | Centronics Host          | 0x1d00010c |

| DRAM Control           | 0x1d000058 | Centronics Mode          | 0x1d000110 |

| DMA Address 0          | 0x1d000080 | Centronics Minimum Delay | 0x1d000114 |

| DMA Address 1          | 0x1d000084 | Centronics Data Detect 0 | 0x1d0000a4 |

| DMA Centronics Address | 0x1d000088 | Centronics Data Detect 1 | 0x1d0000a8 |

| DMA Count 0            | 0x1d000090 | Centronics Data Detect 2 | 0x1d0000ac |

| DMA Count 1            | 0x1d000094 |                          |            |

#### NOTES:

- a) In all the following Tables, bit 0 is the Least Significant Bit.

- b) Most counters need to be loaded with the value n-1 in order to count to n. Please keep this in mind and take careful note of the few exceptions.

- c) Reads and writes from/to the GT-32011 internal registers should be word (32-bit) accesses.

- d) The 0x notation indicates hexadecimal values, as in C language notation.

#### 3.2 ROM Configuration

This register is used to set the ROM address space for the 2 configurable ROM banks (ROMCS[1:0]\*) and to set the

number of wait state cycles inserted between data phases.

#### Address: 1d000000

| Bits  | Field name | Function                                                                                                                                                     | Initial Value |

|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 0-3   | First      | The gap (number of cycles) from ROMCS* active to the first RDCEN*. The range is 16 cycles.  0000 - 16 cycles  0001 - 1 cycle  n - n cycles (except for 0000) | 0xf           |

| 4-7   | Gap1       | The gap between the first RDCEN* and the second RDCEN*. The range is 16 cycles. 0000 - 16 cycles 0001 - 1 cycle n - n cycles (except for 0000)               | Oxf           |

| 8-11  | Gap2       | The gap between the second RDCEN* and the third RDCEN*. The range is 16 cycles.  0000 - 16 cycles  0001 - 1 cycle  n - n cycles (except for 0000)            | Oxf           |

| 12-15 | Gap3       | The gap between the third RDCEN* and the fourth RDCEN* The range is 16 cycles.  0000 - 16 cycles  0001 - 1 cycle n - n cycles (except for 0000)              | 0xf           |