# 2.7V 12-Bit A/D Converter with SPI® Serial Interface

### **FEATURES**

- · 12-bit resolution

- · ±1 LSB max DNL

- ±1 LSB max INL (MCP3201-B)

- ±2 LSB max INL (MCP3201-C)

- · On-chip sample and hold

- SPI<sup>®</sup> serial interface (modes 0,0 and 1,1)

- · Single supply operation: 2.7V 5.5V

- 100ksps max. sampling rate at V<sub>DD</sub> = 5V

- 50ksps max. sampling rate at  $V_{DD} = 2.7V$

- · Low power CMOS technology

- 500nA typical standby current, 2μA max.

- 400μA max. active current at 5V

- Industrial temp range: -40°C to +85°C

- 8-pin PDIP, SOIC and TSSOP packages

#### **APPLICATIONS**

- Sensor Interface

- · Process Control

- · Data Acquisition

- · Battery Operated Systems

### **DESCRIPTION**

The Microchip Technology Inc. MCP3201 is a successive approximation 12-bit Analog-to-Digital (A/D) Converter with on-board sample and hold circuitry. The device provides a single pseudo-differential input. Differential Nonlinearity (DNL) is specified at ±1 LSB, and Integral Nonlinearity (INL) is offered in ±1 LSB (MCP3201-B) and ±2 LSB (MCP3201-C) versions. Communication with the device is done using a simple serial interface compatible with the SPI protocol. The device is capable of sample rates of up to 100ksps at a clock rate of 1.6MHz. The MCP3201 operates over a broad voltage range (2.7V - 5.5V). Low current design permits operation with typical standby and active currents of only 500nA and 300µA, respectively. The device is offered in 8-pin PDIP, TSSOP and 150mil SOIC packages.

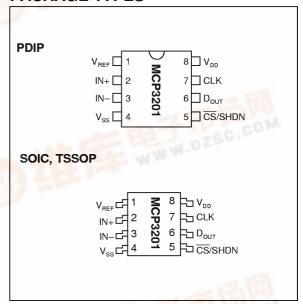

#### **PACKAGE TYPES**

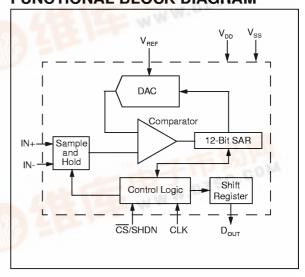

### **FUNCTIONAL BLOCK DIAGRAM**

# 1.0 ELECTRICAL CHARACTERISTICS

### 1.1 Maximum Ratings\*

| V <sub>DD</sub> 7.0V                                          |

|---------------------------------------------------------------|

| All inputs and outputs w.r.t. $V_{SS}$ 0.6V to $V_{DD}$ +0.6V |

| Storage temperature65°C to +150°C                             |

| Ambient temp. with power applied65°C to +125°C                |

| Soldering temperature of leads (10 seconds) +300 °C           |

| ESD protection on all pins> 4kV                               |

\*Notice: Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### **PIN FUNCTION TABLE**

| NAME            | FUNCTION                   |  |  |  |  |  |  |

|-----------------|----------------------------|--|--|--|--|--|--|

| V <sub>DD</sub> | +2.7V to 5.5V Power Supply |  |  |  |  |  |  |

| $V_{SS}$        | Ground                     |  |  |  |  |  |  |

| IN+             | Positive Analog Input      |  |  |  |  |  |  |

| IN-             | Negative Analog Input      |  |  |  |  |  |  |

| CLK             | Serial Clock               |  |  |  |  |  |  |

| $D_OUT$         | Serial Data Out            |  |  |  |  |  |  |

| CS/SHDN         | Chip select/Shutdown Input |  |  |  |  |  |  |

| $V_{REF}$       | Reference Voltage Input    |  |  |  |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

| All parameters apply at $V_{DD}$ = 5V, $V_{SS}$ = 0V, $V_{REF}$ = 5V, $T_{AMB}$ = -40°C to +85°C, $f_{AMPLE}$ = 100ksps and $f_{CLK}$ = 16* $f_{SAMPLE}$ unless otherwise noted. |                     |                      |             |                       |                          |                                                           |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|-------------|-----------------------|--------------------------|-----------------------------------------------------------|--|--|--|

| PARAMETER                                                                                                                                                                        | SYMBOL              | MIN.                 | TYP.        | MAX.                  | UNITS                    | CONDITIONS                                                |  |  |  |

| Conversion Rate                                                                                                                                                                  |                     |                      |             |                       |                          |                                                           |  |  |  |

| Conversion Time                                                                                                                                                                  | t <sub>CONV</sub>   |                      |             | 12                    | clock<br>cycles          |                                                           |  |  |  |

| Analog Input Sample Time                                                                                                                                                         | t <sub>SAMPLE</sub> |                      | 1.5         |                       | clock<br>cycles          |                                                           |  |  |  |

| Throughput Rate                                                                                                                                                                  | f <sub>SAMPLE</sub> |                      |             | 100<br>50             | ksps<br>ksps             | $V_{DD} = V_{REF} = 5V$<br>$V_{DD} = V_{REF} = 2.7V$      |  |  |  |

| DC Accuracy                                                                                                                                                                      |                     |                      |             |                       |                          |                                                           |  |  |  |

| Resolution                                                                                                                                                                       |                     |                      | 12          |                       | bits                     |                                                           |  |  |  |

| Integral Nonlinearity                                                                                                                                                            | INL                 |                      | ±0.75<br>±1 | ±1<br>±2              | LSB<br>LSB               | MCP3201-B<br>MCP3201-C                                    |  |  |  |

| Differential Nonlinearity                                                                                                                                                        | DNL                 |                      | ±0.5        | ±1                    | LSB                      | No missing codes over tem-<br>perature                    |  |  |  |

| Offset Error                                                                                                                                                                     |                     |                      | ±1.25       | ±3                    | LSB                      |                                                           |  |  |  |

| Gain Error                                                                                                                                                                       |                     |                      | ±1.25       | ±5                    | LSB                      |                                                           |  |  |  |

| Dynamic Performance                                                                                                                                                              |                     |                      |             |                       |                          |                                                           |  |  |  |

| Total Harmonic Distortion                                                                                                                                                        |                     |                      | -82         |                       | dB                       | V <sub>IN</sub> = 0.1V to 4.9V@1kHz                       |  |  |  |

| Signal to Noise and Distortion (SINAD)                                                                                                                                           |                     |                      | 72          |                       | dB                       | V <sub>IN</sub> = 0.1V to 4.9V@1kHz                       |  |  |  |

| Spurious Free Dynamic Range                                                                                                                                                      |                     |                      | 86          |                       | dB                       | V <sub>IN</sub> = 0.1V to 4.9V@1kHz                       |  |  |  |

| Reference Input                                                                                                                                                                  |                     |                      |             |                       |                          |                                                           |  |  |  |

| Voltage Range                                                                                                                                                                    |                     | 0.25                 |             | V <sub>DD</sub>       | V                        | Note 2                                                    |  |  |  |

| Current Drain                                                                                                                                                                    |                     |                      | 100<br>.001 | 150<br>3              | μ <b>Α</b><br>μ <b>Α</b> | $\overline{\text{CS}} = \text{V}_{\text{DD}} = 5\text{V}$ |  |  |  |

| Analog Inputs                                                                                                                                                                    |                     |                      |             | •                     | •                        |                                                           |  |  |  |

| Input Voltage Range (IN+)                                                                                                                                                        |                     | IN-                  |             | V <sub>REF</sub> +IN- | V                        |                                                           |  |  |  |

| Input Voltage Range (IN-)                                                                                                                                                        |                     | V <sub>ss</sub> -100 |             | V <sub>SS</sub> +100  | mV                       |                                                           |  |  |  |

| Leakage Current                                                                                                                                                                  |                     |                      | 0.001       | ±1                    | μΑ                       |                                                           |  |  |  |

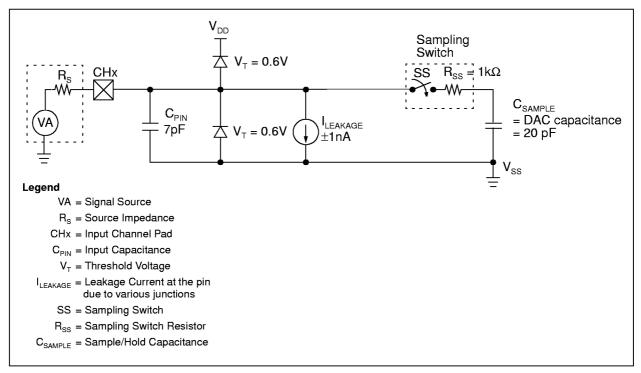

| Switch Resistance                                                                                                                                                                | R <sub>ss</sub>     |                      | 1K          |                       | Ω                        | See Figure 4-1                                            |  |  |  |

| Sample Capacitor                                                                                                                                                                 | C <sub>SAMPLE</sub> |                      | 20          |                       | pF                       | See Figure 4-1                                            |  |  |  |

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| All parameters apply at $V_{DD}$ = 5V, $V_{SS}$ = 0V, $V_{REF}$ = 5V, $T_{AMB}$ = -40°C to +85°C, $f_{AMPLE}$ = 100ksps and $f_{CLK}$ = 16* $f_{SAMPLE}$ unless otherwise noted. |                                    |                     |            |                     |                          |                                                                         |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------|------------|---------------------|--------------------------|-------------------------------------------------------------------------|--|--|

| PARAMETER                                                                                                                                                                        | SYMBOL                             | MIN.                | TYP.       | MAX.                | UNITS                    | CONDITIONS                                                              |  |  |

| Digital Input/Output                                                                                                                                                             | •                                  |                     |            |                     | •                        |                                                                         |  |  |

| Data Coding Format                                                                                                                                                               |                                    | St                  | raight Bin | ary                 |                          |                                                                         |  |  |

| High Level Input Voltage                                                                                                                                                         | V <sub>IH</sub>                    | 0.7 V <sub>DD</sub> |            |                     | V                        |                                                                         |  |  |

| Low Level Input Voltage                                                                                                                                                          | V <sub>IL</sub>                    |                     |            | 0.3 V <sub>DD</sub> | V                        |                                                                         |  |  |

| High Level Output Voltage                                                                                                                                                        | V <sub>OH</sub>                    | 4.1                 |            |                     | V                        | $I_{OH} = -1 \text{ mA}, V_{DD} = 4.5 \text{ V}$                        |  |  |

| Low Level Output Voltage                                                                                                                                                         | V <sub>OL</sub>                    |                     |            | 0.4                 | V                        | $I_{OL} = 1 \text{ mA}, \ V_{DD} = 4.5 \text{ V}$                       |  |  |

| Input Leakage Current                                                                                                                                                            | I <sub>LI</sub>                    | -10                 |            | 10                  | μΑ                       | $V_{IN} = V_{SS}$ or $V_{DD}$                                           |  |  |

| Output Leakage Current                                                                                                                                                           | I <sub>LO</sub>                    | -10                 |            | 10                  | μΑ                       | $V_{OUT} = V_{SS}$ or $V_{DD}$                                          |  |  |

| Pin Capacitance (all inputs/outputs)                                                                                                                                             | C <sub>IN</sub> , C <sub>OUT</sub> |                     |            | 10                  | pF                       | V <sub>DD</sub> = 5.0V (Note 1)<br>T <sub>AMB</sub> = 25 °C, f = 1 MHz  |  |  |

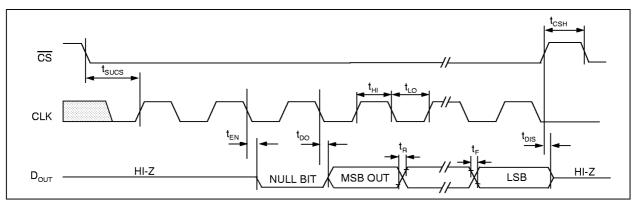

| Timing Parameters                                                                                                                                                                |                                    |                     |            |                     |                          |                                                                         |  |  |

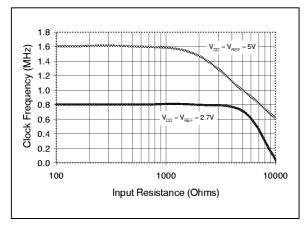

| Clock Frequency                                                                                                                                                                  | f <sub>CLK</sub>                   |                     |            | 1.6<br>0.8          | MHz<br>MHz               | V <sub>DD</sub> = 5V (Note 3)<br>V <sub>DD</sub> = 2.7V (Note 3)        |  |  |

| Clock High Time                                                                                                                                                                  | t <sub>HI</sub>                    | 312                 |            |                     | ns                       |                                                                         |  |  |

| Clock Low Time                                                                                                                                                                   | t <sub>LO</sub>                    | 312                 |            |                     | ns                       |                                                                         |  |  |

| CS Fall To First Rising CLK Edge                                                                                                                                                 | t <sub>sucs</sub>                  | 100                 |            |                     | ns                       |                                                                         |  |  |

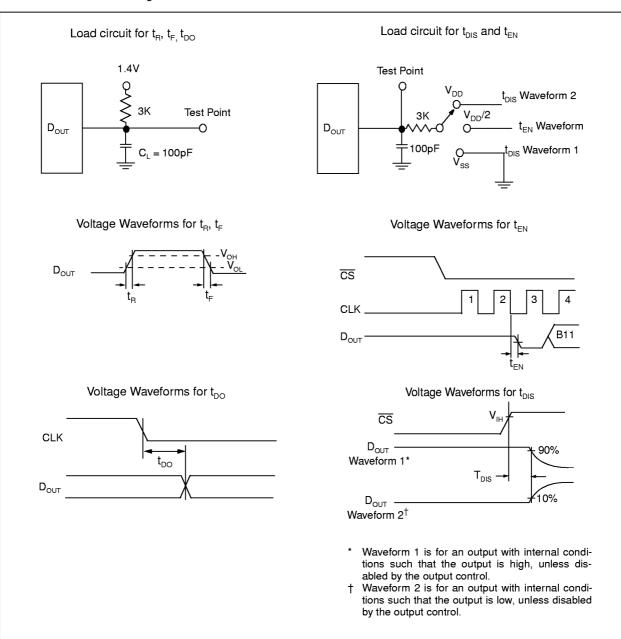

| CLK Fall To Output Data Valid                                                                                                                                                    | t <sub>DO</sub>                    |                     |            | 200                 | ns                       | See Test Circuits, Figure 1-2                                           |  |  |

| CLK Fall To Output Enable                                                                                                                                                        | t <sub>EN</sub>                    |                     |            | 200                 | ns                       | See Test Circuits, Figure 1-2                                           |  |  |

| CS Rise To Output Disable                                                                                                                                                        | t <sub>DIS</sub>                   |                     |            | 100                 | ns                       | See Test Circuits, Figure 1-2 (Note 1)                                  |  |  |

| CS Disable Time                                                                                                                                                                  | t <sub>csh</sub>                   | 625                 |            |                     | ns                       |                                                                         |  |  |

| D <sub>OUT</sub> Rise Time                                                                                                                                                       | t <sub>R</sub>                     |                     |            | 100                 | ns                       | See Test Circuits, Figure 1-2 (Note 1)                                  |  |  |

| D <sub>OUT</sub> Fall Time                                                                                                                                                       | t <sub>F</sub>                     |                     |            | 100                 | ns                       | See Test Circuits, Figure 1-2 (Note 1)                                  |  |  |

| Power Requirements                                                                                                                                                               | •                                  |                     |            |                     |                          |                                                                         |  |  |

| Operating Voltage                                                                                                                                                                | V <sub>DD</sub>                    | 2.7                 |            | 5.5                 | V                        |                                                                         |  |  |

| Operating Current                                                                                                                                                                | I <sub>DD</sub>                    |                     | 300<br>210 | 400                 | μ <b>Α</b><br>μ <b>Α</b> | $V_{DD}$ = 5.0V, $D_{OUT}$ unloaded $V_{DD}$ = 2.7V, $D_{OUT}$ unloaded |  |  |

| Standby Current                                                                                                                                                                  | I <sub>DDS</sub>                   |                     | 0.5        | 2                   | μΑ                       | $\overline{\text{CS}} = \text{V}_{\text{DD}} = 5.0\text{V}$             |  |  |

|                                                                                                                                                                                  |                                    |                     |            |                     |                          |                                                                         |  |  |

- Note 1: This parameter is guaranteed by characterization and not 100% tested.

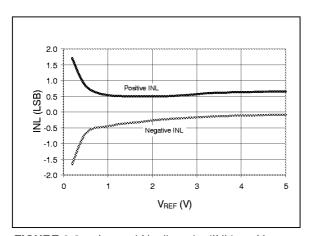

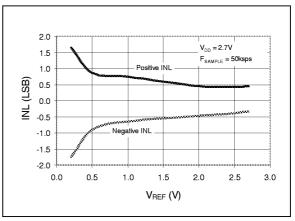

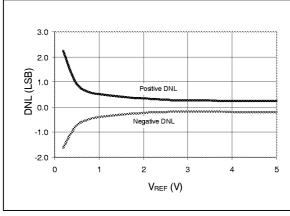

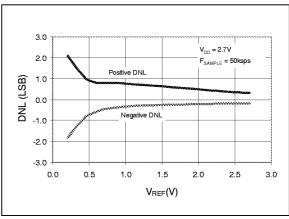

- **2:** See graph that relates linearity performance to  $V_{\text{REF}}$  level.

- 3: Because the sample cap will eventually lose charge, effective clock rates below 10kHz can affect linearity performance, especially at elevated temperatures. See Section 6.2 for more information.

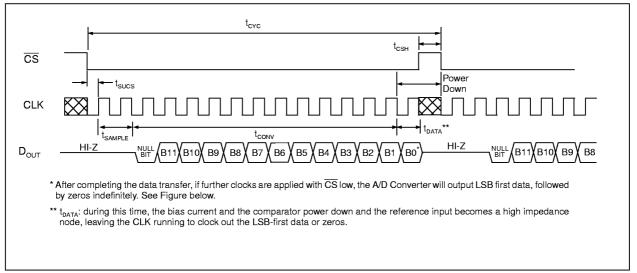

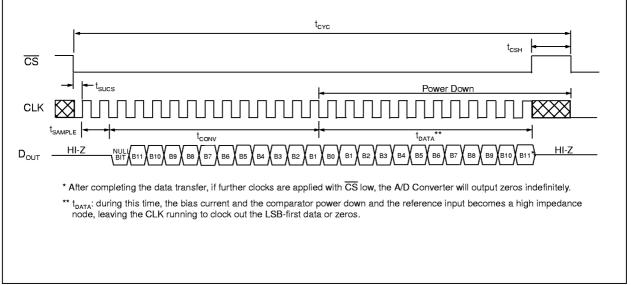

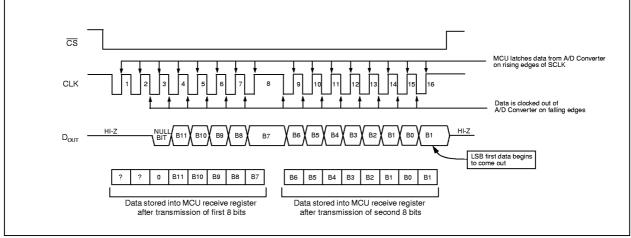

FIGURE 1-1: Serial Timing.

FIGURE 1-2: Test Circuits.

## 2.0 TYPICAL PERFORMANCE CHARACTERISTICS

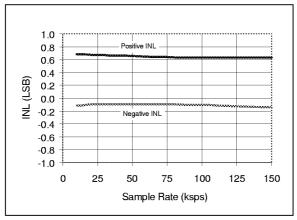

FIGURE 2-1: Integral Nonlinearity (INL) vs. Sample Rate.

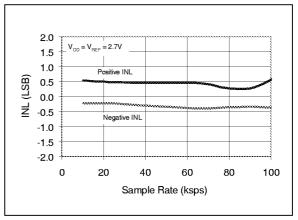

**FIGURE 2-4:** Integral Nonlinearity (INL) vs. Sample Rate  $(V_{DD} = 2.7V)$ .

FIGURE 2-2: Integral Nonlinearity (INL) vs. V<sub>REF.</sub>

**FIGURE 2-5:** Integral Nonlinearity (INL) vs.  $V_{REF}$  ( $V_{DD} = 2.7V$ ).

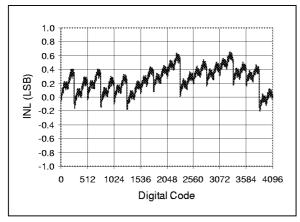

**FIGURE 2-3:** Integral Nonlinearity (INL) vs. Code (Representative Part).

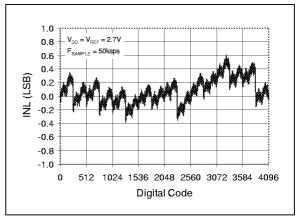

**FIGURE 2-6:** Integral Nonlinearity (INL) vs. Code (Representative Part,  $V_{DD} = 2.7V$ ).

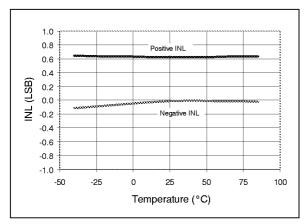

**FIGURE 2-7:** Integral Nonlinearity (INL) vs. Temperature.

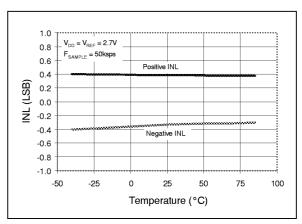

**FIGURE 2-10:** Integral Nonlinearity (INL) vs. Temperature  $(V_{DD} = 2.7V)$ .

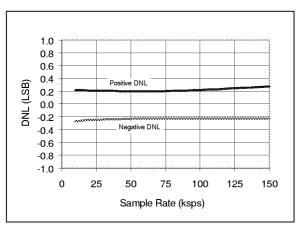

**FIGURE 2-8:** Differential Nonlinearity (DNL) vs. Sample Rate.

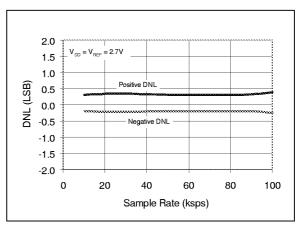

**FIGURE 2-11:** Differential Nonlinearity (DNL) vs. Sample Rate  $(V_{DD} = 2.7V)$ .

**FIGURE 2-9:** Differential Nonlinearity (DNL) vs.  $V_{REF.}$

**FIGURE 2-12:** Differential Nonlinearity (DNL) vs.  $V_{REF}$  ( $V_{DD} = 2.7V$ ).

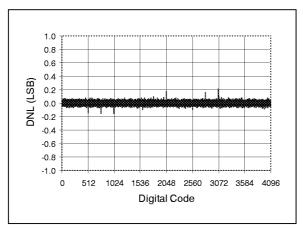

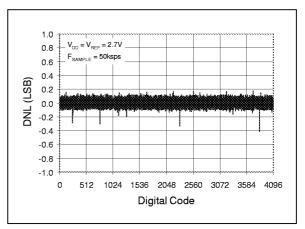

**FIGURE 2-13:** Differential Nonlinearity (DNL) vs. Code (Representative Part).

**FIGURE 2-16:** Differential Nonlinearity (DNL) vs. Code (Representative Part,  $V_{\rm DD} = 2.7V$ ).

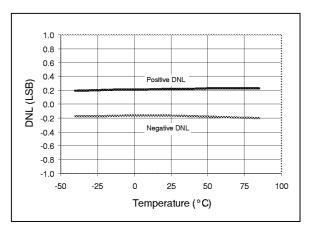

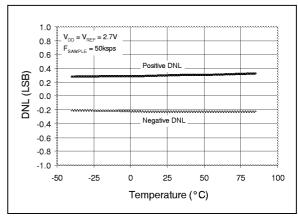

**FIGURE 2-14:** Differential Nonlinearity (DNL) vs. Temperature.

**FIGURE 2-17:** Differential Nonlinearity (DNL) vs. Temperature  $(V_{DD} = 2.7V)$ .

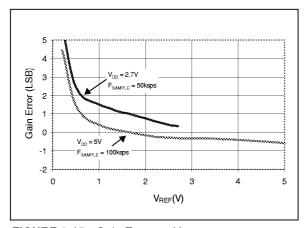

FIGURE 2-15: Gain Error vs. V<sub>REF.</sub>

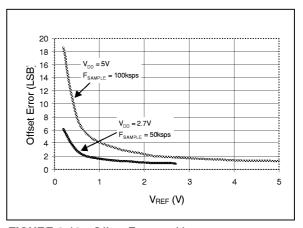

FIGURE 2-18: Offset Error vs. V<sub>REF.</sub>

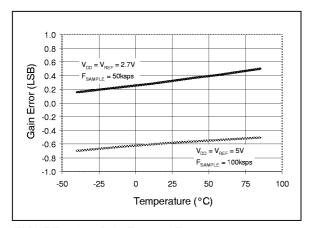

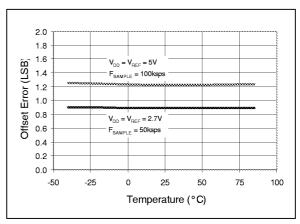

FIGURE 2-19: Gain Error vs. Temperature.

FIGURE 2-22: Offset Error vs. Temperature.

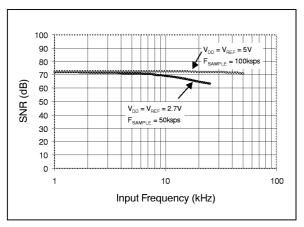

**FIGURE 2-20:** Signal to Noise Ratio (SNR) vs. Input Frequency.

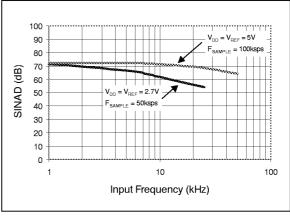

**FIGURE 2-23:** Signal to Noise and Distortion (SINAD) vs. Input Frequency.

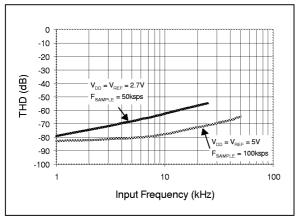

**FIGURE 2-21:** Total Harmonic Distortion (THD) vs. Input Frequency.

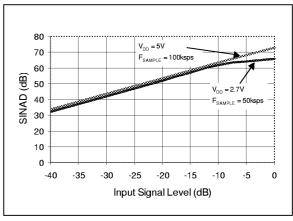

FIGURE 2-24: Signal to Noise and Distortion (SINAD) vs. Input Signal Level.

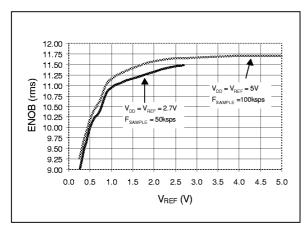

**FIGURE 2-25:** Effective Number of Bits (ENOB) vs.  $V_{REF.}$

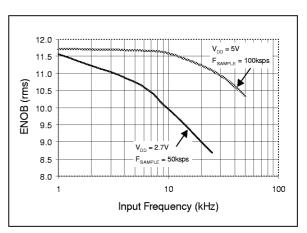

**FIGURE 2-28:** Effective Number of Bits (ENOB) vs. Input Frequency.

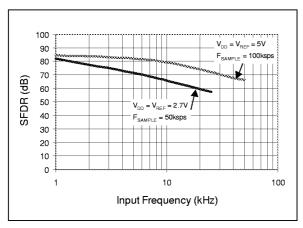

FIGURE 2-26: Spurious Free Dynamic Range (SFDR) vs. Input Frequency.

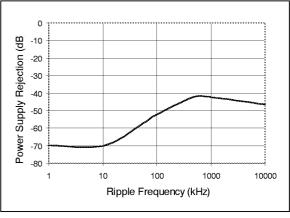

**FIGURE 2-29:** Power Supply Rejection (PSR) vs. Ripple Frequency.

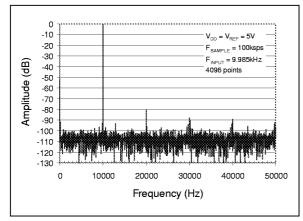

**FIGURE 2-27:** Frequency Spectrum of 10kHz input (Representative Part).

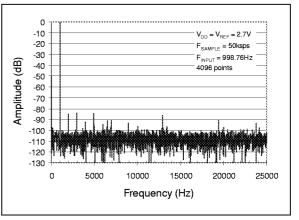

**FIGURE 2-30:** Frequency Spectrum of 1kHz input (Representative Part,  $V_{\rm DD}$  = 2.7V).

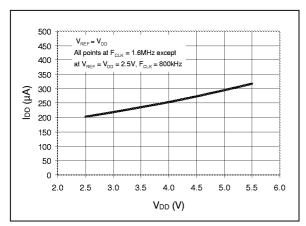

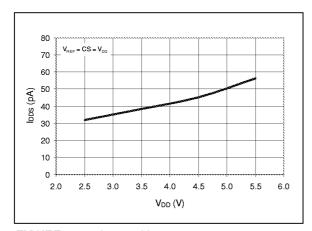

FIGURE 2-31:  $I_{DD}$  vs.  $V_{DD.}$

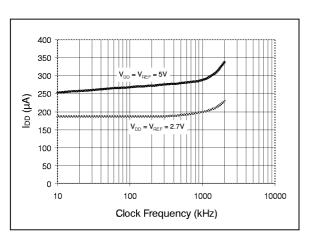

**FIGURE 2-32:**  $I_{DD}$  vs. Clock Frequency.

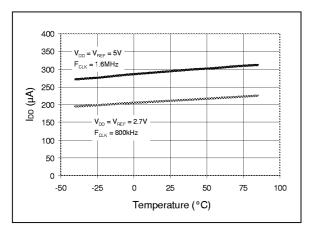

**FIGURE 2-33:**  $I_{DD}$  vs. Temperature.

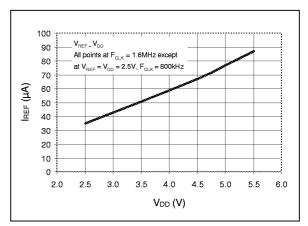

FIGURE 2-34:  $I_{REF}$  vs.  $V_{DD.}$

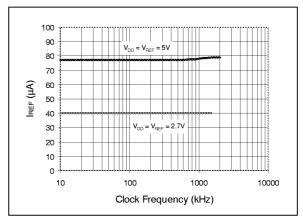

FIGURE 2-35: I<sub>REF</sub> vs. Clock Frequency.

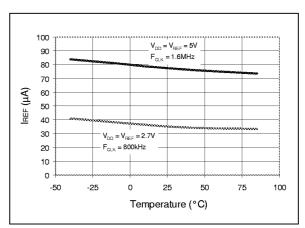

FIGURE 2-36: I<sub>REF</sub> vs. Temperature.

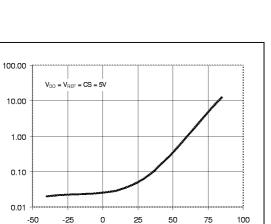

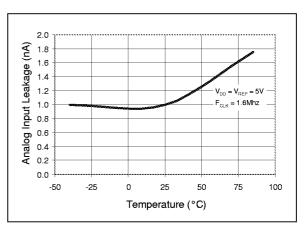

$\textbf{Note:} \ \, \textbf{Unless otherwise indicated,} \ \, \textbf{V}_{\text{DD}} = \textbf{V}_{\text{REF}} = 5 \textbf{V}, \ \, \textbf{V}_{\text{SS}} = 0 \textbf{V}, \ \, \textbf{f}_{\text{SAMPLE}} = 100 \text{ksps}, \ \, \textbf{f}_{\text{CLK}} = 16^* \textbf{f}_{\text{SAMPLE}}, \\ \textbf{T}_{\text{A}} = 25\,^{\circ}\,\text{C}$

FIGURE 2-37:  $I_{DDS}$  vs.  $V_{DD.}$

loos (nA)

Temperature (°C)

**FIGURE 2-38:**  $I_{DDS}$  vs. Temperature.

**FIGURE 2-39:** Analog Input Leakage Current vs. Temperature.

### 3.0 PIN DESCRIPTIONS

#### 3.1 IN+

Positive analog input. This input can vary from IN- to  $\ensuremath{V_{\text{REF}}}$  + IN-.

#### 3.2 IN-

Negative analog input. This input can vary  $\pm 100 \text{mV}$  from  $V_{\rm SS}$ .

#### 3.3 <u>CS/SHDN(Chip Select/Shutdown)</u>

The  $\overline{\text{CS}}/\text{SHDN}$  pin is used to initiate communication with the device when pulled low and will end a conversion and put the device in low power standby when pulled high. The  $\overline{\text{CS}}/\text{SHDN}$  pin must be pulled high between conversions.

#### 3.4 CLK (Serial Clock)

The SPI clock pin is used to initiate a conversion and to clock out each bit of the conversion as it takes place. See Section 6.2 for constraints on clock speed.

#### 3.5 <u>DOUT (Serial Data output)</u>

The SPI serial data output pin is used to shift out the results of the A/D conversion. Data will always change on the falling edge of each clock as the conversion takes place.

#### 4.0 DEVICE OPERATION

The MCP3201 A/D Converter employs a conventional SAR architecture. With this architecture, a sample is acquired on an internal sample/hold capacitor for 1.5 clock cycles starting on the first rising edge of the serial clock after  $\overline{CS}$  has been pulled low. Following this sample time, the input switch of the converter opens and the device uses the collected charge on the internal sample and hold capacitor to produce a serial 12-bit digital output code. Conversion rates of 100ksps are possible on the MCP3201. See Section 6.2 for information on minimum clock rates. Communication with the device is done using a 3-wire SPI-compatible interface.

#### 4.1 Analog Inputs

The MCP3201 provides a single pseudo-differential input. The IN+ input can range from IN- to  $V_{\text{REF}}$  ( $V_{\text{REF}}$  +IN-). The IN- input is limited to ±100mV from the  $V_{\text{SS}}$  rail. The IN- input can be used to cancel small signal common-mode noise which is present on both the IN+ and IN- inputs.

For the A/D Converter to meet specification, the charge holding capacitor ( $C_{\text{SAMPLE}}$ ) must be given enough time to acquire a 12-bit accurate voltage level during the 1.5 clock cycle sampling period. The analog input model is shown in Figure 4-1.

In this diagram, it is shown that the source impedance  $(R_{\rm S})$  adds to the internal sampling switch  $(R_{\rm SS})$  impedance, directly affecting the time that is required to charge the capacitor ( $C_{\rm SAMPLE}$ ). Consequently, a larger source impedance increases the offset, gain, and integral linearity errors of the conversion.

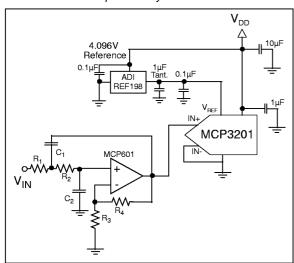

Ideally, the impedance of the signal source should be near zero. This is achievable with an operational amplifier such as the MCP601, which has a closed loop output impedance of tens of ohms. The adverse affects of higher source impedances are shown in Figure 4-2.

If the voltage level of IN+ is equal to or less than IN-, the resultant code will be 000h. If the voltage at IN+ is equal to or greater than  $\{[V_{\text{REF}} + (\text{IN-})] - 1 \text{ LSB}\}$ , then the output code will be FFFh. If the voltage level at IN- is more than 1 LSB below  $V_{\text{SS}}$ , then the voltage level at the IN+ input will have to go below  $V_{\text{SS}}$  to see the 000h output code. Conversely, if IN- is more than 1 LSB above Vss, then the FFFh code will not be seen unless the IN+ input level goes above  $V_{\text{REF}}$  level.

#### 4.2 Reference Input

The reference input ( $V_{\text{REF}}$ ) determines the analog input voltage range and the LSB size, as shown below.

$$LSB \ Size = \frac{V_{REF}}{4096}$$

As the reference input is reduced, the LSB size is reduced accordingly. The theoretical digital output code produced by the A/D Converter is a function of the analog input signal and the reference input as shown below.

$$Digital\ Output\ Code = \frac{4096\ ^*\ V_{IN}}{V_{REF}}$$

where:

$$V_{IN}$$

= analog input voltage =  $V(IN+)$  -  $V(IN-)$

$V_{RFF}$  = reference voltage

When using an external voltage reference device, the system designer should always refer to the manufacturer's recommendations for circuit layout. Any instability in the operation of the reference device will have a direct effect on the operation of the A/D Converter.

FIGURE 4-1: Analog Input Model.

**FIGURE 4-2:** Maximum Clock Frequency vs. Input Resistance  $(R_s)$  to maintain less than a 0.1 LSB deviation in INL from nominal conditions.

#### 5.0 SERIAL COMMUNICATIONS

Communication with the device is done using a standard SPI-compatible serial interface. Initiating communication with the MCP3201 begins with the  $\overline{CS}$  going low. If the device was powered up with the  $\overline{CS}$  pin low, it must be brought high and back low to initiate communication. The device will begin to sample the analog input on the first rising edge after  $\overline{CS}$  goes low. The sample period will end in the falling edge of the second clock, at which time the device will output a low null bit. The next 12 clocks will output the result of the conver-

sion with MSB first, as shown in Figure 5-1. Data is always output from the device on the falling edge of the clock. If all 12 data bits have been transmitted and the device continues to receive clocks while the  $\overline{\text{CS}}$  is held low, the device will output the conversion result LSB first, as shown in Figure 5-2. If more clocks are provided to the device while  $\overline{\text{CS}}$  is still low (after the LSB first data has been transmitted), the device will clock out zeros indefinitely.

FIGURE 5-1: Communication with MCP3201 using MSB first Format.

FIGURE 5-2: Communication with MCP3201 using LSB first Format.

#### 6.0 APPLICATIONS INFORMATION

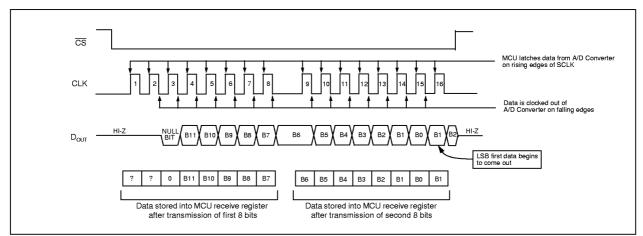

#### 6.1 <u>Using the MCP3201 with</u> Microcontroller SPI Ports

With most microcontroller SPI ports, it is required to clock out eight bits at a time. If this is the case, it will be necessary to provide more clocks than are required for the MCP3201. As an example, Figure 6-1 and Figure 6-2 show how the MCP3201 can be interfaced to a microcontroller with a standard SPI port. Since the MCP3201 always clocks data out on the falling edge of clock, the MCU SPI port must be configured to match this operation. SPI Mode 0,0 (clock idles low) and SPI Mode 1,1 (clock idles high) are both compatible with the MCP3201. Figure 6-1 depicts the operation shown in SPI Mode 0,0, which requires that the CLK from the microcontroller idles in the 'low' state. As shown in the diagram, the MSB is clocked out of the A/D Converter on the falling edge of the third clock pulse. After the first eight clocks have been sent to the device, the microcontroller's receive buffer will contain two unknown bits

(the output is at high impedance for the first two clocks), the null bit and the highest order five bits of the conversion. After the second eight clocks have been sent to the device, the MCU receive register will contain the lowest order seven bits and the B1 bit repeated as the A/D Converter has begun to shift out LSB first data with the extra clock. Typical procedure would then call for the lower order byte of data to be shifted right by one bit to remove the extra B1 bit. The B7 bit is then transferred from the high order byte to the lower order byte, and then the higher order byte is shifted one bit to the right as well. Easier manipulation of the converted data can be obtained by using this method.

Figure 6-2 shows the same thing in SPI Mode 1,1 which requires that the clock idles in the high state. As with mode 0,0, the A/D Converter outputs data on the falling edge of the clock and the MCU latches data from the A/D Converter in on the rising edge of the clock.

FIGURE 6-1: SPI Communication using 8-bit segments (Mode 0,0: SCLK idles low).

FIGURE 6-2: SPI Communication using 8-bit segments (Mode 1,1: SCLK idles high).

#### 6.2 Maintaining Minimum Clock Speed

When the MCP3201 initiates the sample period, charge is stored on the sample capacitor. When the sample period is complete, the device converts one bit for each clock that is received. It is important for the user to note that a slow clock rate will allow charge to bleed off the sample cap while the conversion is taking place. At 85°C (worst case condition), the part will maintain proper charge on the sample capacitor for at least 1.2ms after the sample period has ended. This means that the time between the end of the sample period and the time that all 12 data bits have been clocked out must not exceed 1.2ms (effective clock frequency of 10kHz). Failure to meet this criteria may induce linearity errors into the conversion outside the rated specifications. It should be noted that during the entire conversion cycle, the A/D Converter does not require a constant clock speed or duty cycle, as long as all timing specifications are met.

#### 6.3 <u>Buffering/Filtering the Analog Inputs</u>

If the signal source for the A/D Converter is not a low impedance source, it will have to be buffered or inaccurate conversion results may occur. See Figure 4-2. It is also recommended that a filter be used to eliminate any signals that may be aliased back into the conversion results. This is illustrated in Figure 6-3 where an op amp is used to drive the analog input of the MCP3201. This amplifier provides a low impedance source for the converter input and a low pass filter, which eliminates unwanted high frequency noise.

Low pass (anti-aliasing) filters can be designed using Microchip's interactive **FilterLab™** software. **FilterLab** will calculate capacitor and resistor values, as well as determine the number of poles that are required for the application. For more information on filtering signals, see the application note AN699 "Anti-Aliasing Analog Filters for Data Acquisition Systems."

**FIGURE 6-3:** The MCP601 Operational Amplifier is used to implement a 2nd order anti-aliasing filter for the signal being converted by the MCP3201.

#### 6.4 Layout Considerations

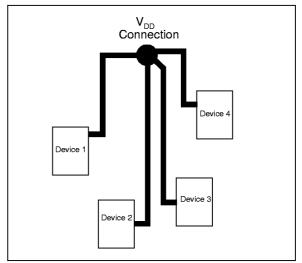

When laying out a printed circuit board for use with analog components, care should be taken to reduce noise wherever possible. A bypass capacitor should always be used with this device and should be placed as close as possible to the device pin. A bypass capacitor value of 1µF is recommended.

Digital and analog traces should be separated as much as possible on the board and no traces should run underneath the device or the bypass capacitor. Extra precautions should be taken to keep traces with high frequency signals (such as clock lines) as far as possible from analog traces.

Use of an analog ground plane is recommended in order to keep the ground potential the same for all devices on the board. Providing V<sub>DD</sub> connections to devices in a "star" configuration can also reduce noise by eliminating current return paths and associated errors. See Figure 6-4. For more information on layout tips when using A/D Converter, refer to AN688 "Layout Tips for 12-Bit A/D Converter Applications".

**FIGURE 6-4:**  $V_{DD}$  traces arranged in a 'Star' configuration in order to reduce errors caused by current return paths.

FilterLab is a trademark of Microchip Technology Inc. in the U.S.A and other countries. All rights reserved.

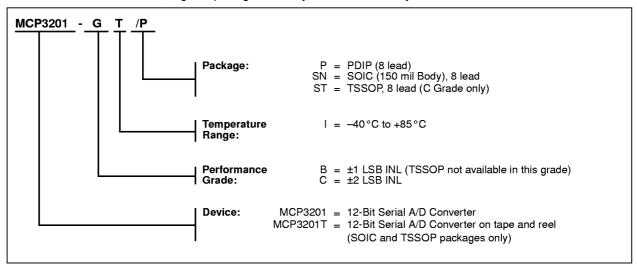

#### MCP3201 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

#### **Sales and Support**

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277. After September 1, 1999, (480) 786-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.