**PRODUCTS**

Semiconductor IC

BD3533EKN

TYPE

PAGE

1/4

**STRUCTURE**

**FEATURES**

Silicon Monolithic Integrated Circuit

**TYPE**

Regulator IC for Memory termination

PRODUCT SERIES

BD3533EKN

·Incorporates a push-pull power supply for termination (VTT)

·Incorporates a reference voltage circuit (VREF)

-Compatible with Dual Channel (DDR-II)

### O ABSOLUTE MAXIMUM RATINGS (Ta=100°C)

| Parameter                    | Symbol | Limit    | Unit |

|------------------------------|--------|----------|------|

| Input Voltage                | VCC    | 7 '1"2   | V    |

| Enable Input Voltage         | VEN    | 7 '1'2   | V    |

| Termination Input Voltage    | VTT_IN | 7 12     | V    |

| VDDQ Reference Voltage       | VDDQ   | 7 12     | V    |

| Output Current               | ĪΠ     | 3        | Α    |

| Power Dissipation 1          | Pd1    | 0.5 '3   | W    |

| Power Dissipation 2          | Pd2    | 0.75     | W    |

| Power Dissipation 3          | Pd3    | 1.75 5   | W    |

| Power Dissipation 4          | Pd4    | 2.0 6    | W    |

| Operating Temperature Range  | Topr   | -20~+100 | °C   |

| Storage Temperature Range    | Tstg   | -55~+150 | °C   |

| Maximum Junction Temperature | Tjmax  | +150     | °C   |

<sup>\*1</sup> Should not exceed Pd.

#### O RECOMMENDED OPERATING CONDITIONS (Ta=25°C)

| PARAMETER                 | SYMBOL | MIN  | MAX  | UNIT |

|---------------------------|--------|------|------|------|

| Input Voltage             | VCC    | 2.7  | 5.5  | V    |

| Termination Input Voltage | VTT_IN | 1.0  | 5.5  | V    |

| VDDQ Reference Voltage    | VDDQ   | 1.0  | 2.75 | V    |

| VDDQ Reference Voltage    | VEN    | -0.3 | 5.5  | ٧    |

<sup>★</sup> No radiation-resistant design is adopted for the present product.

#### Status of this document

The Japanese version of this document is the official specification.

This translated version is intended only as a reference, to aid in understanding the official version.

If there are any differences between the original and translated versions of this document, the official Japanese language version takes priority.

#### Application example

· ROHM cannot provide adequate confirmation of patents.

• The product described in this specification is designed to be used with ordinary electronic equipment or devices (such as audio-visual equipment, office-automation equipment, communications devices, electrical appliances, and electronic toys).

Should you intend to use this product with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

• ROHM assumes no responsibility for use of any circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement.

| DESIGN | CHECK | APPROVAL | DATE: | MAY/13/2005 | SPECIFICATION No. : TSZ02201- BD3533EKN -1-2 |

|--------|-------|----------|-------|-------------|----------------------------------------------|

| Willey | They, | Junahush | REV.  | В .         | ROHM CO., LTD.                               |

<sup>\*2</sup> Instantaneous surge voltage, back electromotive force and voltage under less than 10% duty cycle.

<sup>\*3</sup> Ta≥25°C (no heat sink)4mW/°C increase.

<sup>\*4</sup> Ta≥25°C (when mounted on 70mm x 70mm x 1.6mm Glass-epoxy PCB which does not have copper on the back side)

<sup>\*5</sup> Ta≥25°C (when mounted on 70mm x 70mm x 1.6mm Glass-epoxy PCB which has 1 layer

<sup>( 60</sup>mm x 60mm ) of copper on the back side) 14mW/°C increase.

<sup>\*6</sup> Ta≥25\*C (When mounted on board 70mm x 70mm x 1.6mm Glass-epoxy PCB which has 2 layers (60mm x 60mm) of copper on the back side )16mW/C increase.

2/4

O ELECTRICAL CHARACTERISTICS (Unless otherwise specified, Ta=25°C VCC=3.3V VEN=3V VDDQ=1.8V VTT\_IN=1.8V)

|                                    |             | ss otherwise specified, 1a=25°C VCC=3.3°C LIMIT |            |                    |      |                                                                             |

|------------------------------------|-------------|-------------------------------------------------|------------|--------------------|------|-----------------------------------------------------------------------------|

| PARAMETER                          | SYMBOL      | MIN                                             | TYP        | MAX                | UNIT | CONDITIONS                                                                  |

| Standby Current                    | IST         | •                                               | 0.8        | 1.6                | mA   | VEN=0V                                                                      |

| Bias Current                       | ICC         | -                                               | 2          | 4                  | mA   | VEN=3V                                                                      |

| [Enable]]                          |             |                                                 |            |                    |      |                                                                             |

| High Level Enable Input<br>Voltage | VENHIG<br>H | 2.3                                             | -          | 5.5                | ٧    |                                                                             |

| Low Level Enable Input<br>Voltage  | VENLOW      | -0.3                                            | -          | 0.8                | ٧    |                                                                             |

| Enable Pin Input<br>Current        | IEN         | -                                               | 7          | 10                 | uA   | VEN=3V                                                                      |

| [Termination]                      |             |                                                 |            |                    |      |                                                                             |

| Termination Output Voltage 1       | VTT1        | VREF-30m                                        | VREF       | VREF+30m           | ٧    | Ta=0°C to 100°C                                                             |

| Termination Output<br>Voltage 1    | VTT2        | VREF-30m                                        | VREF       | VREF+30m           | ٧    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V<br>ITT=-1.0A to 1.0A<br>Ta=0°C to 100°C '7 |

| Source Current                     | ITT+        | 1.0                                             | •          | -                  | Α    |                                                                             |

| Sink Current                       | ITT-        | -                                               | ٠          | -1.0               | Α    |                                                                             |

| Load Regulation                    | ZVIT        | -                                               | •          | 50                 | mV   | ITT=-1.0A to 1.0A                                                           |

| Line Regulation                    | Reg.l       |                                                 | 20         | 40                 | mV   |                                                                             |

| Upper Side ON Resistance 1         | HRON1       | -                                               | 0.45       | 0.9                | Ω    |                                                                             |

| Lower Side ON Resistance 1         | LRON1       | -                                               | 0.45       | 0.9                | Ω    |                                                                             |

| Upper Side ON<br>Resistance 2      | HRON2       | •                                               | 0.4        | 0.8                | Ω    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V                                            |

| Lower Side ON Resistance 2         | LRON2       | •                                               | 0.4        | 0.8                | Ω    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V                                            |

| [Input of Reference Volta          | agei        | <u> </u>                                        |            |                    |      |                                                                             |

| Input Impedance                    | ZVDDQ       | 70                                              | 100        | 130                | kΩ   |                                                                             |

| [Reference voltage]                |             |                                                 |            |                    |      |                                                                             |

| Output Voltage 1                   | VREF1       | 1/2 × VDDQ<br>-30m                              | 1/2×VDDQ   | 1/2 × VDDQ<br>+30m | ٧    | IREF=0mA                                                                    |

| Output Voltage 2                   | VREF2       | 1/2 × VDDQ<br>-40m                              | 1/2 × VUUQ | 1/2 × VDDQ<br>+40m | ٧    | IREF=-10mA to 10mA<br>Ta=0°C to 100°C <sup>7</sup>                          |

| Output Voltage 3                   | VREF3       | 1/2 × VDDQ<br>-30m                              | 1/2×VDDQ   | 1/2 × VDDQ<br>+30m | ٧    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V, IREF=0m                                   |

| Output Voltage 4                   | VREF4       | 1/2 × VDDQ<br>-40m                              | 1/2×VDDQ   | 1/2 × VDDQ<br>+40m | ٧    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V<br>ITT=-10mA to 10mA<br>Ta=0°C to 100°C '7 |

| Source Current                     | IREF+       | 20                                              | -          | •                  | mA   |                                                                             |

| Sink Current                       | IREF-       | -                                               | -          | -20                | mA   |                                                                             |

| [UVLO]                             | L           |                                                 |            |                    |      |                                                                             |

| UVLO OFF Voltage                   | VUVLO       | 2.40                                            | 2.55       | 2.70               | ٧    | VCC : sweep up                                                              |

| Hysteresis Voltage                 | ⊿vuvlo      | 100                                             | 160        | 220                | mV   | VCC : sweep down                                                            |

\*7 Design Guarantee

ROHM CO., LTD.

REV. :

В

SPECIFICATION No. :

TSZ02201- BD3533EKN -1-2

PAGE 3/4

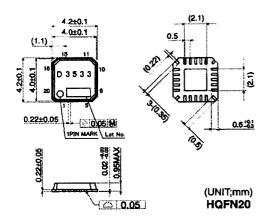

## O PHYSICAL DIMENSIONS

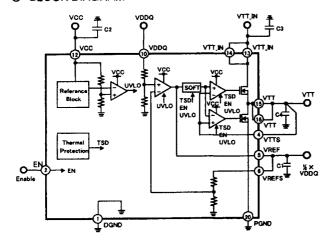

# O BLOCK DIAGRAM

# O Pin number Pin name

| PIN | Pin name    |

|-----|-------------|

| No. | i iii nanie |

| 1   | DGND        |

| 2   | EN          |

| 3   | N.C         |

| 4   | VTTS        |

| 5   | VREF        |

| 6   | VREFS       |

| 7   | N.C         |

| 8   | N.C         |

| 9   | N.C         |

| 10  | VDDQ        |

| 11  | N.C         |

| 12  | VCC         |

| 13  | VTT_IN      |

| 14  | VTT_IN      |

| 15  | VTT         |

| 16  | VΠ          |

| 17  | N.C         |

| 18  | N.C         |

| 19  | N.C         |

| 20  | PGND        |

| -   | FIN         |

|     |             |

ROHM CO., LTD.

REV. :

В

SPECIFICATION No. :

TSZ02201- BD3533EKN -1-2

# **ONOTES FOR USE**

(1) Absolute maximum range

Although the quality of this product is rigorously controlled, and circuit operation is guaranteed within the operation ambient temperature range, the device may be destroyed when applied voltage or operating temperature exceeds its absolute maximum rating. Because the failure mode (such as short mode or open mode) cannot be identified in this instance, it is important to take physical safety measures such as fusing if a specific mode in excess of absolute rating limits is considered for implementation.

Ground potential (2)

Make sure the potential for the GND pin is always kept lower than the potentials of all other pins, regardless of the operating mode, including transient conditions.

Thermal Design (3)

Provide sufficient margin in the thermal design to account for the allowable power dissipation (Pd) expected in actual use.

Using in the strong electromagnetic field

Use in strong electromagnetic fields may cause malfunctions.

ASO

Be sure that the output transistor for this IC does not exceed the absolute maximum ratings or ASO value.

Thermal shutdown circuit

The IC is provided with a built-in thermal shutdown (TSD) circuit. When chip temperature reaches the threshold temperature shown below, output goes to a cut-off (open) state. Note that the TSD circuit is designed exclusively to shut down the IC in abnormal thermal conditions. It is not intended to protect the IC per se or guarantee performance when extreme heat occurs. Therefore, the TSD circuit should not be employed with the expectation of continued use or subsequent operation once TSD is operated.

| TSD ON temperature [°C] (typ.) | Hysteresis temperature [°C] (typ.) |

|--------------------------------|------------------------------------|

| 175                            | 15                                 |

(7) GND pattern

When both a small-signal GND and high current GND are present, single-point grounding (at the set standard point) is recommended, in order to separate the small-signal and high current patterns, and to be sure the voltage change stemming from the wiring resistance and high current does not cause any voltage change in the small-signal GND. In the same way, care must be taken to avoid wiring pattern fluctuations in any connected external component GND.

(B) Output Capacitor (C1)

Mount an output capacitor between VREF and GND for stability purposes. The VREF output capacitor is for the open loop gain phase compensation. If the capacitor value is not large enough, the output voltage may oscillate. A ceramic 1.0 - 10uF capacitor with minimal susceptibility to temperature is recommended. However, this stability depends on the characteristics of temperature and load. Please confirm operation across a variety of temperature and load conditions.

Output Capacitor (C4)

Mount an output capacitor between VTT and GND for stability purposes. The output capacitor is for the open loop gain phase compensation and reduces the output voltage load regulation. If the capacitor value is not large enough, the output voltage may oscillate. And if the equivalent series resistance (ESR) is too large, the output voltage rise/drop increases during a sudden load change. A 47 - 220uF polymer capacitor is recommended. However, the stability depends on the characteristics of temperature and load conditions. And if a small ESR capacitor such as a ceramic capacitor is utilized, the output voltage may oscillate due to lack of phase margin. In this case, measures can be taken by adding a resistor in series with this capacitor. Please confirm operation across a variety of temperature and load conditions.

The input capacitor reduces the output impedence of the voltage supply source connected in the VCC and VTT\_IN. If the output impedence of this power supply increases, the input voltage (VCC,VTT\_IN) may become unstable. This may result in the output voltage oscillation or lowering ripple rejection. A low ESR 1uF capacitor in VCC and 10uF capacitor in VTT IN with minimal susceptibility to temperature are preferable, but stability depends on power supply characteristics and the substrate wiring pattern (a parasitic capacitance and impedance). Please confirm operation across a variety of temperature and load conditions.

(11) Input (VCC, VDDQ, VTT\_IN, EN)

The VCC, VDDQ, VTT\_IN, and EN are isolated. The UVLO function is integrated to protect faulty operation due to low voltage levels of VCC. VTT output voltage starts up when VCC reaches the UVLO threshold level and EN reaches the threshold level respectively regardless of the start up order in those inputs. And also VREF output voltage starts up when VCC reaches the UVLO threshold level. When the VDDQ and VTT\_IN has the same voltage and are supposed to connect each other, VDDQ pin voltage may change due to the voltage drop on the VTT\_IN and VDDQ common wiring caused by VTT\_IN input current change. This may result in the voltage change of the VTT output. Avoid drawing wiring pattern of VDDQ and VTT\_IN so that they do not have common wiring. If the common wiring is inevitable due to limited PCB area, it is recommended that CR filter be added between VTT\_IN and VDDQ.

(12) VTTS

VTTS is to improve load regulation of VTT output. For precise load regulation, VTTS is connected close by VTT to avoid common impedance.

(13) Heat Sink (FIN)

Since the heat sink (FIN) is connected with the Sub, short it to the GND. It is possible to minimize the thermal resistance by soldering it to GND plane of PCB.

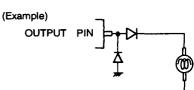

(14) Short-circuits between pins and and mounting errors

Do not short-circuit between output pin (Vo) and supply pin (Vcc) or ground (GND), or between supply pin (Vcc) and ground (GND). Mounting errors, such as incorrect positioning or orientation, may destroy the device.

Please add a protection diode when a large inductance component is connected to the output terminal, and reverse-polarity power is possible at startup or in output OFF condition.

ROHM CO., LTD.

REV. :

В

SPECIFICATION No. :

TSZ02201- BD3533EKN -1-2