19-2829; Rev 1; 7/03

##

## Anything-to-LVDS Dual 2 x 2 **Crosspoint Switches**

#### **General Description**

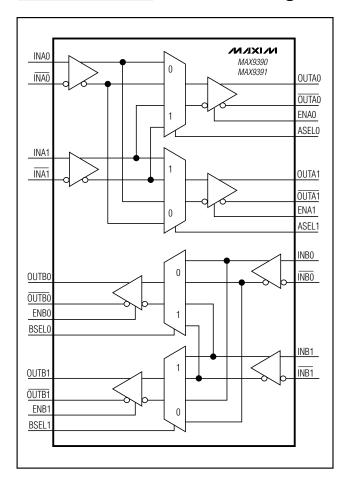

The MAX9390/MAX9391 dual 2 x 2 crosspoint switches perform high-speed, low-power, and low-noise signal distribution. The MAX9390/MAX9391 multiplex one of two differential input pairs to either or both low-voltage differential signaling (LVDS) outputs for each channel. Independent enable inputs turn on or turn off each differential output pair.

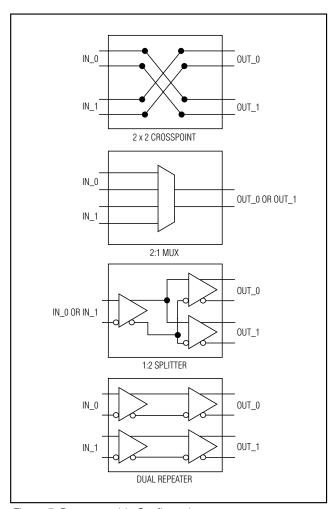

Four LVCMOS/LVTTL logic inputs (two per channel) control the internal connections between inputs and outputs. This flexibility allows for the following configurations: 2 x 2 crosspoint switch, 2:1 mux, 1:2 splitter, or dual repeater. This makes the MAX9390/MAX9391 ideal for protection switching in fault-tolerant systems, loopback switching for diagnostics, fanout buffering for clock/data distribution, and signal regeneration.

Fail-safe circuitry forces the outputs to a differential low condition for undriven inputs or when the commonmode voltage exceeds the specified range. The MAX9390 provides high-level input fail-safe detection for LVDS, HSTL, and other GND-referenced differential inputs. The MAX9391 provides low-level input fail-safe detection for LVPECL, CML, and other VCC-referenced differential inputs.

Ultra-low 82ps(P-P) (max) pseudorandom bit sequence (PRBS) jitter ensures reliable communications in highspeed links that are highly sensitive to timing error, especially those incorporating clock-and-data recovery, or serializers and deserializers. The high-speed switching performance guarantees 1.5GHz operation and less than 65ps (max) skew between channels.

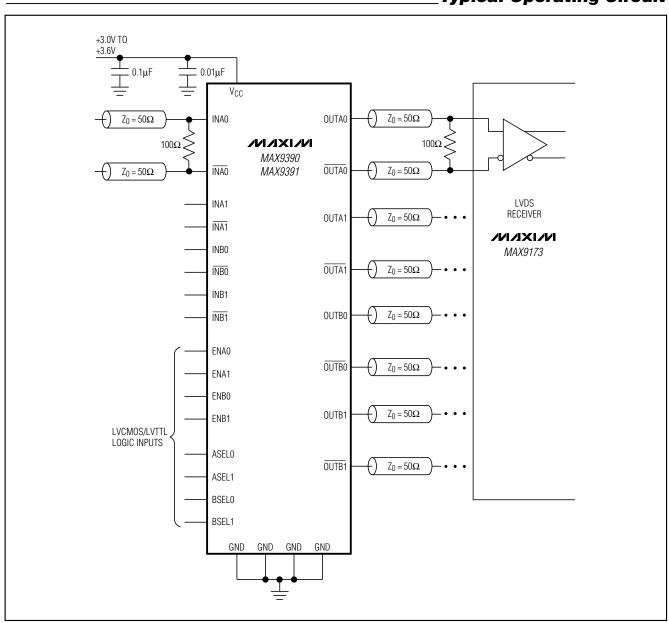

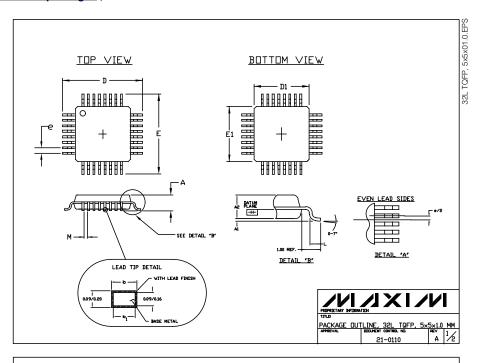

LVDS inputs and outputs are compatible with the TIA/EIA-644 LVDS standard. The LVDS outputs drive  $100\Omega$  loads. The MAX9390/MAX9391 are offered in a 32-pin TQFP and 5mm x 5mm thin QFN package with exposed paddle and operate over the extended temperature range (-40°C to +85°C).

Also refer to the MAX9392/MAX9393 with flow-through pinout.

#### **Applications**

High-Speed Telecom/Datacom Equipment Central-Office Backplane Clock Distribution

DSLAM

Protection Switching Fault-Tolerant Systems

Functional Diagram and Typical Operating Circuit appear at

end of data sheet.

#### **Features**

- ♦ 1.5GHz Operation with 250mV Differential Output

- ◆ 2ps(RMS) (max) Random Jitter

- ♦ AC Specifications Guaranteed for 150mV **Differential Input**

- ♦ Signal Inputs Accept Any Differential Signaling Standard

- ◆ LVDS Outputs for Clock or High-Speed Data

- ♦ High-Level Input Fail-Safe Detection (MAX9390)

- ♦ Low-Level Input Fail-Safe Detection (MAX9391)

- ♦ +3.0V to +3.6V Supply Voltage Range

- LVCMOS/LVTTL Logic Inputs Control Signal Routing

#### Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX9390EHJ  | -40°C to +85°C | 32 TQFP     |

| MAX9390ETJ* | -40°C to +85°C | 32 Thin QFN |

| MAX9391EHJ  | -40°C to +85°C | 32 TQFP     |

| MAX9391ETJ* | -40°C to +85°C | 32 Thin QFN |

<sup>\*</sup>Future product—contact factory for availability.

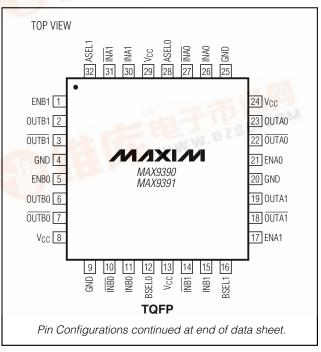

#### Pin Configurations

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +4.1V IN , IN , OUT , OUT , EN , |

|----------------------------------------------------------------|

| _SEL_ to GND0.3V to (V <sub>CC</sub> + 0.3V)                   |

| IN to IN±3V                                                    |

| Short-Circuit Duration (OUT, OUT)Continuous                    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )          |

| 32-Pin QFP (derate 13.1mW/°C                                   |

| above +70°C)1047mW                                             |

| 32-Pin 5mm x 5mm Thin QFN (derate 21.3mW/°C                    |

| above +70°C)1702mW                                             |

| Junction-to-Ambient Thermal Resistance in Still Air            |

| 32-Pin QFP+76.4°C/W                                            |

| 32-Pin 5mm x 5mm Thin QFN+47°C/W                               |

| Junction-to-Case Thermal Resistance |                |

|-------------------------------------|----------------|

| 32-Pin 5mm x 5mm Thin QFN           | +2°C/W         |

| Operating Temperature Range         | 40°C to +85°C  |

| Junction Temperature                | +150°C         |

| Storage Temperature Range           | 65°C to +150°C |

| ESD Protection (Human Body Model)   |                |

| (IN, ĪN, OUT, OUT, EN               | , SEL)±2kV     |

| Soldering Temperature (10s)         | +300°C         |

|                                     |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 100 \Omega \pm 1\%, EN_{-} = V_{CC}, V_{CM} = 0.05 \text{V to } (V_{CC} - 0.6 \text{V}) \text{ (MAX9390)}, V_{CM} = 0.6 \text{V to } (V_{CC} - 0.05 \text{V}) \text{ (MAX9391)}$   $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3 \text{V}$ ,  $|V_{ID}| = 0.2 \text{V}$ ,  $V_{CM} = +1.2 \text{V}$ ,  $T_A = +25 ^{\circ}\text{C}$ .) (Notes 1, 2, and 3)

| PARAMETER                                                                        | SYMBOL            | C                             | CONDITIONS                                    | MIN   | TYP  | MAX                    | UNITS |

|----------------------------------------------------------------------------------|-------------------|-------------------------------|-----------------------------------------------|-------|------|------------------------|-------|

| LVCMOS/LVTTL INPUTS (EN, _SE                                                     | L_)               | •                             |                                               |       |      |                        |       |

| Input High Voltage                                                               | V <sub>IH</sub>   |                               |                                               | 2.0   |      | Vcc                    | V     |

| Input Low Voltage                                                                | V <sub>IL</sub>   |                               |                                               | 0     |      | 0.8                    | V     |

| Input High Current                                                               | lıH               | $V_{IN} = +2.0V \text{ to}$   | VCC                                           | 0     |      | 20                     | μΑ    |

| Input Low Current                                                                | I <sub>IL</sub>   | $V_{IN} = 0 \text{ to } +0.8$ | 3V                                            | 0     |      | 10                     | μΑ    |

| DIFFERENTIAL INPUTS (IN, IN                                                      | )                 |                               |                                               |       |      |                        |       |

| Differential Input Voltage                                                       | $V_{ID}$          | V <sub>ILD</sub> ≥ 0 and V    | / <sub>IHD</sub> ≤ V <sub>CC</sub> , Figure 1 | 0.1   |      | 3.0                    | V     |

| Input Common Mada Danga                                                          | Vari              | MAX9390                       |                                               | 0.05  |      | V <sub>C</sub> C - 0.6 | V     |

| Input Common-Mode Range                                                          | V <sub>CM</sub>   | MAX9391                       |                                               | 0.6   | \    | / <sub>CC</sub> - 0.05 |       |

| Input Current                                                                    | I <sub>IN</sub> , | MAX9390                       | IV <sub>ID</sub> I <u>≤</u> 3.0V              | -75   |      | +10                    | ^     |

| Input Current                                                                    | I <sub>IN</sub>   | MAX9391                       | IV <sub>ID</sub> I <u>≤</u> 3.0V              | -10   |      | +100                   | μΑ    |

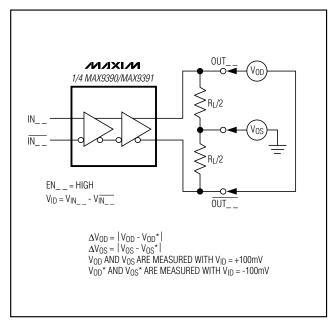

| LVDS OUTPUTS (OUT, $\overline{\text{OUT}}$ _)                                    |                   |                               |                                               |       |      |                        |       |

| Differential Output Voltage                                                      | V <sub>OD</sub>   | $R_L = 100\Omega$ , Fig       | gure 2                                        | 250   | 350  | 450                    | mV    |

| Change in Magnitude of V <sub>OD</sub><br>Between Complementary Output<br>States | ΔV <sub>OD</sub>  | Figure 2                      |                                               |       | 1.0  | 50                     | mV    |

| Offset Common-Mode Voltage                                                       | Vos               | Figure 2                      |                                               | 1.125 | 1.25 | 1.375                  | V     |

| Change in Magnitude of VOS<br>Between Complementary Output<br>States             | ΔV <sub>OS</sub>  | Figure 2                      |                                               |       | 1.0  | 50                     | mV    |

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 100 \Omega \pm 1\%, EN_L = V_{CC}, V_{CM} = 0.05 \text{V to } (V_{CC} - 0.6 \text{V}) \text{ (MAX9390)}, V_{CM} = 0.6 \text{V to } (V_{CC} - 0.05 \text{V}) \text{ (MAX9391)}$   $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3 \text{V}$ ,  $|V_{ID}| = 0.2 \text{V}$ ,  $V_{CM} = +1.2 \text{V}$ ,  $T_A = +25 ^{\circ}\text{C}$ .) (Notes 1, 2, and 3)

| PARAMETER                                               | SYMBOL              | C                                                                      | MIN                                    | TYP | MAX | UNITS |      |

|---------------------------------------------------------|---------------------|------------------------------------------------------------------------|----------------------------------------|-----|-----|-------|------|

| Output Short-Circuit Current                            | llosl               | $V_{ID} = \pm 100 \text{mV}$                                           | $V_{OUT}$ or $V_{\overline{OUT}} = 0$  |     | 30  | 40    | mA   |

| (Either Output Shorted to GND)                          | IIOSI               | (Note 4)                                                               | $V_{OUT} = V_{\overline{OUT}} = 0$     |     | 18  | 24    | IIIA |

| Output Short-Circuit Current (Outputs Shorted Together) | II <sub>OSB</sub> I | V <sub>ID</sub> = ±100mV, V <sub>OUT</sub> = V <del>OUT</del> (Note 4) |                                        |     | 5.0 | 12    | mA   |

| SUPPLY CURRENT                                          |                     |                                                                        |                                        |     |     |       |      |

|                                                         |                     | $R_L = 100\Omega$ , EN                                                 | _ = VCC                                |     | 68  | 98    |      |

| Supply Current                                          | Icc                 | $R_L = 100\Omega$ , EN 670MHz (1.340                                   | = V <sub>CC</sub> , switching at Gbps) |     | 68  | 98    | mA   |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 V \ to \ +3.6 V, \ f_{IN} \le 1.34 GHz, \ t_{R\_IN} = t_{F\_IN} = 125 ps, \ R_L = 100 \Omega \ \pm1\%, \ |V_{ID}| \ge 150 mV, \ V_{CM} = +0.075 V \ to \ (V_{CC} - 0.6 V) \ (MAX9390 \ only), \ V_{CM} = +0.6 V \ to \ (V_{CC} - 0.075 V) \ (MAX9391 \ only), \ EN_{\_} = V_{CC}, \ T_A = -40 ^{\circ}C \ to \ +85 ^{\circ}C, \ unless \ otherwise \ noted. \ Typical values are at V_{CC} = +3.3 V, \ |V_{ID}| = 0.2 V, \ V_{CM} = +1.2 V, \ f_{IN} = 1.34 GHz, \ T_A = +25 ^{\circ}C.) \ (Note 5)$

| PARAMETER                                          | SYMBOL           | CONDITIONS                                        | MIN  | TYP  | MAX | UNITS   |

|----------------------------------------------------|------------------|---------------------------------------------------|------|------|-----|---------|

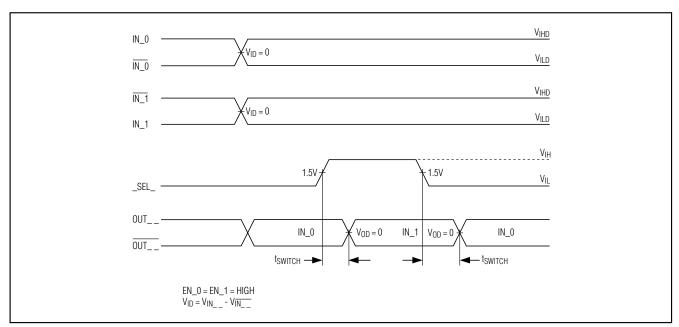

| _SEL_ to Switched Output                           | tswitch          | Figure 3                                          |      |      | 1.1 | ns      |

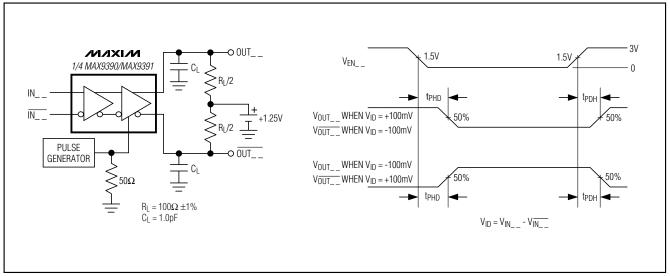

| Disable, Time to Differential Output Low           | <sup>t</sup> PHD | Figure 4                                          |      |      | 1.7 | ns      |

| Enable, Time to Differential<br>Output High        | tpDH             | Figure 4                                          |      |      | 1.7 | ns      |

| Switching Frequency                                | f <sub>MAX</sub> | V <sub>OD</sub> ≥ 250mV                           | 1.50 | 2.20 |     | GHz     |

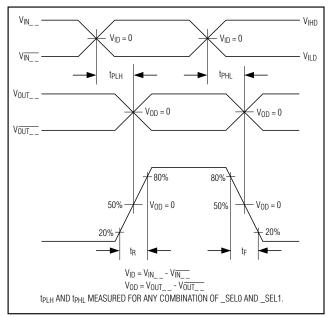

| Low-to-High Propagation Delay                      | tplH             | Figures 1, 5                                      | 294  | 409  | 565 | ps      |

| High-to-Low Propagation Delay                      | tphl             | Figures 1, 5                                      | 286  | 402  | 530 | ps      |

| Pulse Skew ItpLH - tpHLI                           | tskew            | Figures 1, 5 (Note 6)                             |      | 7    | 97  | ps      |

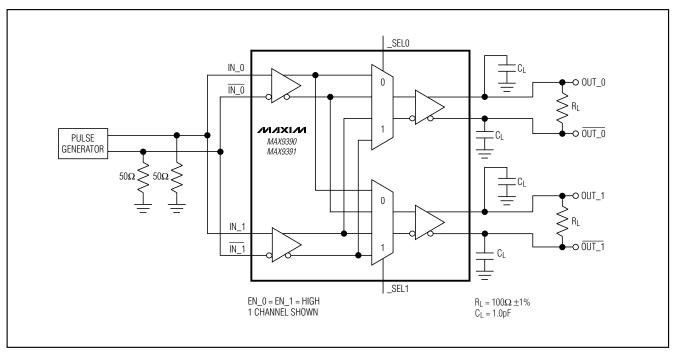

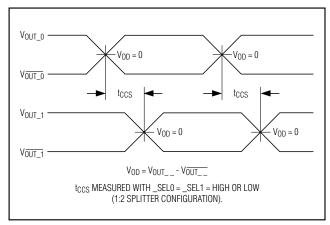

| Output-to-Output Skew                              | tccs             | Figures 5, 6 (Note 7)                             |      | 10   | 65  | ps      |

| Output Low-to-High Transition<br>Time (20% to 80%) | tR               | Figures 1, 5; f <sub>IN</sub> = 100MHz            | 112  | 153  | 185 | ps      |

| Output High-to-Low Transition<br>Time (80% to 20%) | tF               | Figures 1, 5; f <sub>IN</sub> = 100MHz            | 112  | 153  | 185 | ps      |

| Added Random Jitter                                | t <sub>RJ</sub>  | f <sub>IN</sub> = 1.34GHz, clock pattern (Note 8) |      |      | 2   | ps(RMS) |

| Added Deterministic Jitter                         | t <sub>DJ</sub>  | 1.34Gbps, 2 <sup>23</sup> - 1 PRBS (Note 8)       |      | 55   | 82  | ps(P-P) |

- Note 1: Measurements obtained with the device in thermal equilibrium. All voltages referenced to GND except VID, VOD, and  $\Delta$ VOD.

- Note 2: Current into the device defined as positive. Current out of the device defined as negative.

- Note 3: DC parameters tested at T<sub>A</sub> = +25°C and guaranteed by design and characterization for T<sub>A</sub> = -40°C to +85°C.

- Note 4: Current through either output.

- Note 5: Guaranteed by design and characterization. Limits set at ±6 sigma.

- Note 6: tskew is the magnitude difference of differential propagation delays for the same output over same conditions. tskew = ltpHL tpLHl.

- Note 7: Measured between outputs of the same device at the signal crossing points for a same-edge transition, under the same conditions.

- Note 8: Device jitter added to the differential input signal.

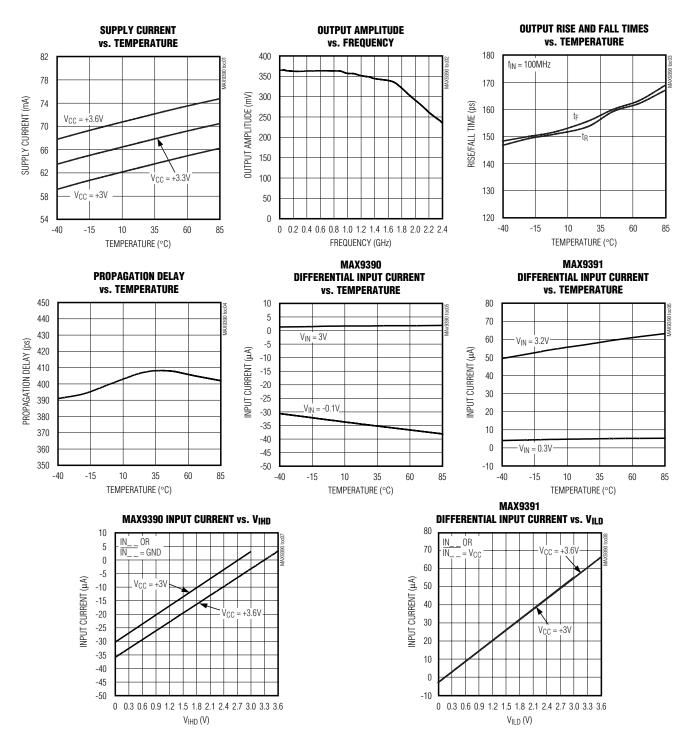

#### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, |V_{ID}| = 0.2V, V_{CM} = +1.2V, f_{IN} = 1.34GHz, T_A = +25^{\circ}C.)$

## Pin Description

| PIN              | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | ENB1            | B1 Output Enable. Drive ENB1 high to enable the B1 LVDS outputs. An internal $435k\Omega$ resistor pulls ENB1 low when unconnected.                                                                                                                                                                                                                                            |

| 2                | OUTB1           | B1 LVDS Noninverting Output. Connect a $100\Omega$ termination resistor between OUTB1 and $\overline{\text{OUTB1}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                         |

| 3                | OUTB1           | B1 LVDS Inverting Output. Connect a $100\Omega$ termination resistor between OUTB1 and $\overline{\text{OUTB1}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                            |

| 4, 9,<br>20, 25  | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                         |

| 5                | ENB0            | B0 Output Enable. Drive ENB0 high to enable the B0 LVDS outputs. An internal $435k\Omega$ resistor pulls ENB0 low when unconnected.                                                                                                                                                                                                                                            |

| 6                | OUTB0           | B0 LVDS Noninverting Output. Connect a $100\Omega$ termination resistor between OUTB0 and $\overline{\text{OUTB0}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                         |

| 7                | OUTB0           | B0 LVDS Inverting Output. Connect a $100\Omega$ termination resistor between OUTB0 and $\overline{\text{OUTB0}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                            |

| 8, 13,<br>24, 29 | V <sub>CC</sub> | Power-Supply Input. Bypass each V <sub>CC</sub> to GND with 0. 1µF and 0.01µF ceramic capacitors. Install both bypass capacitors as close to the device as possible, with the 0.01µF capacitor closest to the device.                                                                                                                                                          |

| 10               | ĪNB0            | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Inverting Input. An internal $128k\Omega$ resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9390). An internal $68k\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                     |

| 11               | INB0            | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Noninverting Input. An internal 128k $\Omega$ resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9390). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                |

| 12               | BSEL0           | Input Select for B0 Output. Selects the differential input to reproduce at the B0 differential outputs. Connect BSEL0 to GND or leave open to select the INB0 $(\overline{\text{INB0}})$ set of inputs. Connect BSEL0 to $V_{CC}$ to select the INB1 $(\overline{\text{INB1}})$ set of inputs. An internal 435k $\Omega$ resistor pulls BSEL0 low when unconnected.            |

| 14               | ĪNB1            | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Inverting Input. An internal $128k\Omega$ resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9390). An internal $68k\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                     |

| 15               | INB1            | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Noninverting Input. An internal 128k $\Omega$ resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9390). An internal 68k $\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                |

| 16               | BSEL1           | Input Select for B1 Output. Selects the differential input to reproduce at the B1 differential outputs. Connect BSEL1 to GND or leave open to select the INB0 ( $\overline{\text{INB0}}$ ) set of inputs. Connect BSEL1 to V <sub>CC</sub> to select the INB1 ( $\overline{\text{INB1}}$ ) set of inputs. An internal 435k $\Omega$ resistor pulls BSEL1 low when unconnected. |

## Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17  | ENA1  | A1 Output Enable. Drive ENA1 high to enable the A1 LVDS outputs. An internal $435k\Omega$ resistor pulls ENA1 low when unconnected.                                                                                                                                                                                                                                            |

| 18  | OUTA1 | A1 LVDS Inverting Output. Connect a $100\Omega$ termination resistor between OUTA1 and $\overline{\text{OUTA1}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                            |

| 19  | OUTA1 | A1 LVDS Noninverting Output. Connect a $100\Omega$ termination resistor between OUTA1 and $\overline{\text{OUTA1}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                         |

| 21  | ENA0  | A0 Output Enable. Drive ENA0 high to enable the A0 LVDS outputs. An internal $435 k\Omega$ resistor pulls ENA0 low when unconnected.                                                                                                                                                                                                                                           |

| 22  | OUTA0 | A0 LVDS Inverting Output. Connect a $100\Omega$ termination resistor between OUTA0 and $\overline{\text{OUTA0}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                            |

| 23  | OUTA0 | A0 LVDS Noninverting Output. Connect a $100\Omega$ termination resistor between OUTA0 and $\overline{\text{OUTA0}}$ at the receiver inputs to ensure proper operation.                                                                                                                                                                                                         |

| 26  | INAO  | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Noninverting Input. An internal $128k\Omega$ resistor to $V_{CC}$ pulls the input high when unconnected (MAX9390). An internal $68k\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                         |

| 27  | ĪNĀŌ  | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Inverting Input. An internal $128k\Omega$ resistor to V <sub>CC</sub> pulls the input high when unconnected (MAX9390). An internal $68k\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                     |

| 28  | ASEL0 | Input Select for A0 Output. Selects the differential input to reproduce at the A0 differential outputs. Connect ASEL0 to GND or leave open to select the INA0 ( $\overline{\text{INA0}}$ ) set of inputs. Connect ASEL0 to V <sub>CC</sub> to select the INA1 ( $\overline{\text{INA1}}$ ) set of inputs. An internal 435k $\Omega$ resistor pulls ASEL0 low when unconnected. |

| 30  | INA1  | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Noninverting Input. An internal $128k\Omega$ resistor to $V_{CC}$ pulls the input high when unconnected (MAX9390). An internal $68k\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                         |

| 31  | ĪNA1  | LVDS/HSTL (MAX9390) or LVPECL/CML (MAX9391) Inverting Input. An internal $128k\Omega$ resistor to $V_{CC}$ pulls the input high when unconnected (MAX9390). An internal $68k\Omega$ resistor to GND pulls the input low when unconnected (MAX9391).                                                                                                                            |

| 32  | ASEL1 | Input Select for A1 Output. Selects the differential input to reproduce at the A1 differential outputs. Connect ASEL1 to GND or leave open to select the INA0 ( $\overline{\text{INA0}}$ ) set of inputs. Connect ASEL1 to V <sub>CC</sub> to select the INA1 ( $\overline{\text{INA1}}$ ) set of inputs. An internal 435k $\Omega$ resistor pulls ASEL1 low when unconnected. |

| _   | EP    | Exposed Paddle (QFN Package Only). Connect to GND for optimal thermal and EMI characteristics.                                                                                                                                                                                                                                                                                 |

Figure 1. Output Transition Time and Propagation Delay Timing Diagram

Figure 2. Test Circuit for VOD and VOS

Figure 3. Input to Rising/Falling Edge Select and Mux Switch Timing Diagram

Figure 4. Output Active-to-Disable and Disable-to-Active Test Circuit and Timing Diagram

Figure 5. Output Transition Time, Propagation Delay, and Output Channel-to-Channel Skew Test Circuit

Figure 6. Output Channel-to-Channel Skew

#### Detailed Description

The LVDS interface standard provides a signaling method for point-to-point communication over a controlled-impedance medium as defined by the ANSI TIA/EIA-644 standard. LVDS utilizes a lower voltage swing than other communication standards, achieving higher data rates with reduced power consumption, while reducing EMI emissions and system susceptibility to noise.

The MAX9390/MAX9391 1.5GHz dual 2 x 2 crosspoint switches optimize high-speed, low-power, point-to-point interfaces. The MAX9390 accepts LVDS and HSTL signals, while the MAX9391 accepts LVPECL and CML signals. Both devices route the input signals to either or both LVDS outputs.

When configured as a 1:2 splitter, the outputs repeat the selected inputs. This configuration creates copies of signals for protection switching. When configured as a repeater, the device operates as a two-channel buffer. Repeating restores signal amplitude, allowing isolation of media segments or longer media drive. When configured as a 2:1 mux, select primary or backup signals to provide a protection-switched, fault-tolerant application.

#### Input Fail-Safe

The differential inputs of the MAX9390/MAX9391 possess internal fail-safe protection. Fail-safe circuitry forces the outputs to a differential low condition for undriven inputs or when the common-mode voltage exceeds the specified range. The MAX9390 provides high-level input fail-safe detection for LVDS, HSTL, and other GND-referenced differential inputs. The MAX9391 provides low-level input fail-safe detection for LVPECL, CML, and other VCC-referenced differential inputs.

Figure 7. Programmable Configurations

#### **Select Function**

The \_SEL\_ logic inputs control the input and output signal connections. Two logic inputs control the signal routing for each channel. \_SEL0 and \_SEL1 allow the devices to be configured as a differential crosspoint switch, 2:1 mux, dual repeater, or 1:2 splitter (Figure 7). See Table 1 for mode-selection settings (insert A or B for the \_). Channels A and B possess separate select inputs, allowing different configurations for each channel.

#### **Enable Function**

The EN\_ logic inputs enable and disable each set of differential outputs. Connect EN\_ 0 to VCC to enable the OUT\_0/OUT\_0 differential output pair. Connect EN\_0 to GND to disable the OUT\_0/OUT\_0 differential output pairs. The differential output pairs assert to a differential low condition when disabled.

**Table 1. Input/Output Function Table**

| _SEL0 | _SEL1 | OUT_0 / OUT_0                       | OUT_1 / OUT_1                       | MODE         |

|-------|-------|-------------------------------------|-------------------------------------|--------------|

| 0     | 0     | IN_0 / <del>I</del> N_ <del>0</del> | IN_0 / <del>I</del> N_ <del>0</del> | 1:2 splitter |

| 0     | 1     | IN_0 / <del>I</del> N_ <del>0</del> | IN_1 / <del>I</del> N_1             | Repeater     |

| 1     | 0     | IN_1 / ĪN_1                         | IN_0 / <del>I</del> N_ <del>0</del> | Switch       |

| 1     | 1     | IN_1 / ĪN_1                         | IN_1 / <del>I</del> N_ <del>1</del> | 1:2 splitter |

### Applications Information

#### **Differential Inputs**

The MAX9390/MAX9391 inputs accept any differential signaling standard within the specified common-mode voltage range. The fail-safe feature detects common-mode input signal levels and generates a differential output low condition for undriven inputs or when the common-mode voltage exceeds the specified range. Leave unused inputs unconnected or connect to VCC for the MAX9390 or to GND for the MAX9391.

## Expanding the Number of LVDS Output Ports

Cascade devices to make larger switches. Consider the total propagation delay and total jitter when determining the maximum allowable switch size.

#### **Power-Supply Bypassing**

Bypass each V<sub>CC</sub> to GND with high-frequency surface-mount ceramic  $0.1\mu F$  and  $0.01\mu F$  capacitors in parallel as close to the device as possible. Install the  $0.01\mu F$  capacitor closest to the device.

#### **Differential Traces**

Input and output trace characteristics affect the performance of the MAX9390/MAX9391. Connect each input and output to a  $50\Omega$  characteristic impedance trace. Maintain the distance between differential traces and eliminate sharp corners to avoid discontinuities in differential impedance and maximize common-mode noise immunity. Minimize the number of vias on the differential input and output traces to prevent impedance discontinuities. Reduce reflections by maintaining the  $50\Omega$  characteristic impedance through connectors and across cables. Minimize skew by matching the electrical length of the traces.

#### **Output Termination**

Terminate LVDS outputs with a  $100\Omega$  resistor between the differential outputs at the receiver inputs. LVDS outputs require  $100\Omega$  termination for proper operation.

Ensure that the output currents do not exceed the current limits specified in the *Absolute Maximum Ratings*. Observe the total thermal limits of the MAX9390/MAX9391 under all operating conditions.

#### **Cables and Connectors**

Use matched differential impedance for transmission media. Use cables and connectors with matched differential impedance to minimize impedance discontinuities. Avoid the use of unbalanced cables. Balanced cables such as twisted pair offer superior signal quality and tend to generate less EMI due to canceling effects.

#### **Board Layout**

Use a four-layer printed circuit (PC) board providing separate signal, power, and ground planes for high-speed signaling applications. Bypass  $V_{\rm CC}$  to GND as close to the device as possible. Install termination resistors as close to receiver inputs as possible. Match the electrical length of the differential traces to minimize signal skew.

#### **Typical Operating Circuit**

#### Functional Diagram

#### Pin Configurations (continued)

**Chip Information**

**TRANSISTOR COUNT: 1565**

PROCESS: Bipolar

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

|        |      |          |      |           | OMMO      | LDIME     | NEIO | VIC.      |           |      |         |      |

|--------|------|----------|------|-----------|-----------|-----------|------|-----------|-----------|------|---------|------|

|        |      |          |      |           | JIVIIVIOI | N DIIVIE  |      |           |           |      |         |      |

| PKG.   |      | 16L 5x5  |      |           | 20L 5x5   |           |      | 28L 5x5   |           |      | 32L 5x5 |      |

| SYMBOL | MIN. | NOM.     | MAX. | MIN.      | NOM.      | MAX.      | MIN. | NOM.      | MAX.      | MIN. | NOM.    | MAX. |

| Α      | 0.70 | 0.75     | 0.80 | 0.70      | 0.75      | 0.80      | 0.70 | 0.75      | 0.80      | 0.70 | 0.75    | 0.80 |

| A1     | 0    | 0.02     | 0.05 | 0         | 0.02      | 0.05      | 0    | 0.02      | 0.05      | 0    | 0.02    | 0.05 |

| A3     | - (  | 0.20 REF |      | 0.20 REF. |           | 0.20 REF. |      |           | 0.20 REF. |      |         |      |

| р      | 0.25 | 0.30     | 0.35 | 0.25      | 0.30      | 0.35      | 0.20 | 0.25      | 0.30      | 0.20 | 0.25    | 0.30 |

| D      | 4.90 | 5.00     | 5.10 | 4.90      | 5.00      | 5.10      | 4.90 | 5.00      | 5.10      | 4.90 | 5.00    | 5.10 |

| Е      | 4.90 | 5.00     | 5.10 | 4.90      | 5.00      | 5.10      | 4.90 | 5.00      | 5.10      | 4.90 | 5.00    | 5.10 |

| 0      |      | 0.80 BS  | Э.   | 0.65 BSC. |           | 0.50 BSC. |      | 0.50 BSC. |           |      |         |      |

| k      | 0.25 | -        | -    | 0.25      | -         | -         | 0.25 | -         | -         | 0.25 | -       | -    |

| ٦      | 0.45 | 0.55     | 0.65 | 0.45      | 0.55      | 0.65      | 0.45 | 0.55      | 0.65      | 0.30 | 0.40    | 0.50 |

| N      |      | 16       |      |           | 20        |           | 28   |           |           | 32   |         |      |

| ND     | 4    |          | 5    |           | 7         |           | 8    |           |           |      |         |      |

| NE     | 4    |          | 5    |           | 7         |           | 8    |           |           |      |         |      |

| JEDEC  |      | WHHB     |      | WHHC      |           | WHHD-1    |      | WHHD-2    |           |      |         |      |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |  |

|------------------------|------|------|------|------|------|------|--|--|

| PKG.                   | D2   |      |      | E2   |      |      |  |  |

| CODES                  | MIN. | NOM. | MAX. | MIN. | NOM. | MAX. |  |  |

| T1655-1                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2855-1                | 3.15 | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-2                | 2.60 | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T3255-2                | 3.00 | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

- DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

- 2. NLS THE TOTAL NUMBER OF TERMINALS.

▲ THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- ♠ ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS

- 9 DRAWING CONFORMS TO JEDEC MO220

- 10. WARPAGE SHALL NOT EXCEED 0.10 mm.

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

# NOTES: 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5-1982. 2. DATUM PLANE EHE IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BIDDY AT BOITTOM OF PARTING LINE. 3. DIMENSIONS DI AND EL DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.854 MM CN DI AND EL DIMENSION BY DESCRIPTION OF PACKAGE IS MALLER THAN THE BOITTOM OF PACKAGE BY 0.15 MILLIMETERS. 5. DIMENSION AT MAXIMUM MATERIAL CONDITION. 6. CONTROLLING DIMENSION HALL BE 0.09 MM TOTAL IN EXCESS OF THE BURNATURE CONDITION. 7. THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95, REGISTRATION MO-136. 8. LEADS SHALL BE COPLANAR WITHIN .004 INCH. 1. THE SHAPE OF THE

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.