# NIXIN

# 8 Digit LED Display Driver

#### **General Description**

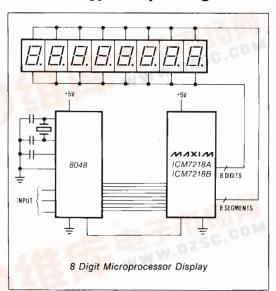

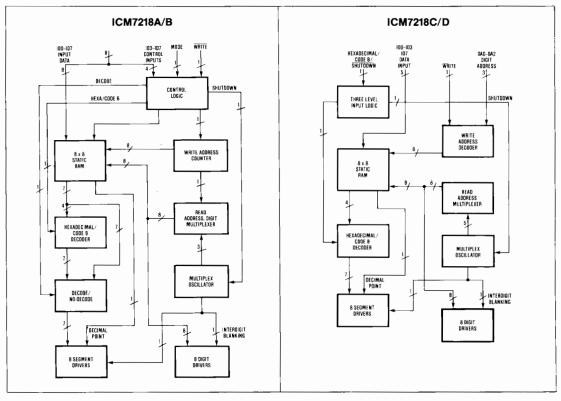

The Maxim ICM7218 display driver interfaces microprocessors to an 8 digit, 7 segment, numeric LED display. Included on chip are two types of 7 segment decoders, multiplex scan circuitry, segment and digit drivers, and an 8 × 8 static memory.

The ICM7218A and ICM7218B accept data in a serial format and drive common anode (ICM7218A) or common cathode (ICM7218B) displays. The ICM7218C and ICM7218D accept data in a parallel format and drive common anode (ICM7218C) or common cathode (ICM7218D) displays. All four versions can display the data in either hexadecimal or code B format. The ICM7218A and ICM7218B also feature a No Decode mode where each individual segment can be independently controlled. This is particularly useful in driving bar graphs.

The Maxim ICM7218 is an alternative for both the Intersil ICM7218 and ICM7228. When ordering, specify ICM7218 for both devices.

#### **Applications**

Instrumentation

Test Equipment

Hand Held Instruments

Bargraph Displays

Panel Meters

#### **Typical Operating Circuit**

#### Features

- ♦ Improved 2nd Source! See 3rd page of this data sheet for our "Maxim Advantage"

- ◆ Fast Access Time: 200ns Write Pulse Width

- ♦ Microprocessor Compatible

- Hexadecimal and Code B Decoders

- Individual Segment Control with "No Decode" Feature

- ♦ Digit and Segment Drivers On-Chip

- ♦ Common Anode and Common Cathode LED versions available

- **♦ Low Power CMOS**

#### **Ordering Information**

| PART        | TEMP. RANGE    | PACKAGE*            |

|-------------|----------------|---------------------|

| ICM7218AIPI | -20°C to +85°C | 28 Lead Plastic DIP |

| ICM7218AIJI | -20°C to +85°C | 28 Lead CERDIP      |

| ICM7218BIPI | -20°C to +85°C | 28 Lead Plastic DIP |

| ICM7218BIJI | -20°C to +85°C | 28 Lead CERDIP      |

| ICM7218CIPI | -20°C to +85°C | 28 Lead Plastic DIP |

| ICM7218CIJI | -20°C to +85°C | 28 Lead CERDIP      |

| ICM7218DIPI | -20°C to +85°C | 28 Lead Plastic DIP |

| ICM7218DIJI | -20°C to +85°C | 28 Lead CERDIP      |

|             |                |                     |

(Ordering Information Continued on Last Page.)

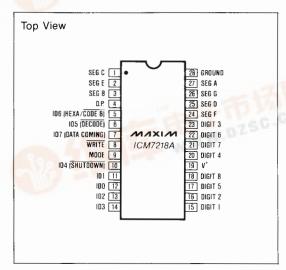

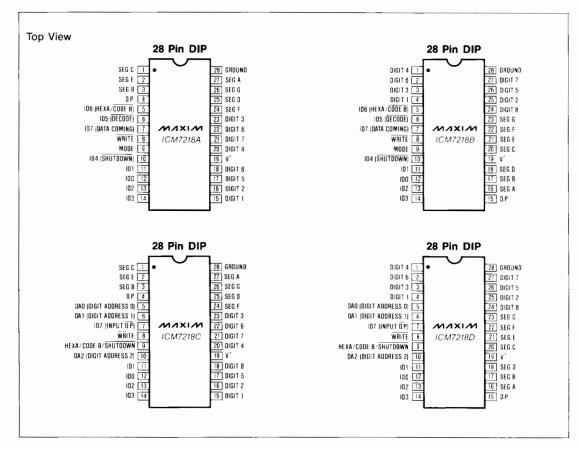

### Pin Configuration

MIXIM

Maxim Integrated Products

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                                | 6V      |

|-----------------------------------------------|---------|

| Digit Output Current                          | 500mA   |

| Segment Output Current                        | 100mA   |

| Input Voltage (any terminal) V+ + 0.3V to GNI | O.3V    |

| (1                                            | Note 1) |

Power Dissipation (28 Pin CERDIP) ..... 1.0W (Note 2)

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS** $(V^{+} = 5V \pm 10\%, T_A = 25^{\circ}C)$

| PARAMETER                                                                                     | SYMBOL                                                   | CONDITIONS                                                                                    | MIN        | TYP              | MAX         | UNITS |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------|------------------|-------------|-------|

| Operating Voltage                                                                             | V <sup>+</sup>                                           | Power Down Mode                                                                               | 4 2        |                  | 6<br>6      | v     |

| Quiescent Supply Current                                                                      | Io                                                       | Shutdown (Note 3)                                                                             | 6          | 10               | 300         | μΑ    |

| Operating Supply Current                                                                      | I <sub>OP</sub>                                          | Decoder On, Outputs Open Ckt<br>No Decode, Outputs Open Ckt                                   | 250<br>200 |                  | 950<br>450  | μΑ    |

| Digit Drive Current                                                                           | I <sub>DIG</sub>                                         | Common Anode $V_{OUT} = V^* - 2.0V$<br>Common Cathode $V_{OUT} = V^- + 1V$                    | -170<br>50 | _                |             | mA    |

| Digit Leakage Current                                                                         | I <sub>DLK</sub>                                         |                                                                                               |            |                  | 100         | μΑ    |

| Peak Segment Drive Current                                                                    | I <sub>SEG</sub>                                         | Common Anode $V_{OUT} = V^{-} + 1.5V$<br>Common Cathode $V_{OUT} = V^{+} - 2.0V$              | 20<br>-10  | 25               |             | mA    |

| Segment Leakage Current                                                                       | I <sub>SLK</sub>                                         |                                                                                               |            | _                | 50          | μΑ    |

| Display Scan Rate                                                                             | f <sub>MUX</sub>                                         | Per Digit                                                                                     |            | 250              |             | Hz    |

| Three Level Input<br>Logical "1" Input Voltage<br>Floating Input<br>Logical "0" Input Voltage | V <sub>INH</sub><br>V <sub>INF</sub><br>V <sub>INL</sub> | Hexadecimal ICM7218C, D (Pin 9)<br>Code B ICM7218C, D (Pin 9)<br>Shutdown ICM7218C, D (Pin 9) | 4.0<br>2.0 |                  | 3.0<br>1.75 | V     |

| Three Level Input Impedance                                                                   | Z <sub>IN</sub>                                          | Note 3                                                                                        |            | 100              |             | kΩ    |

| Logical "1" Input Voltage<br>Logical "0" Input Voltage                                        | V <sub>IH</sub><br>V <sub>IL</sub>                       |                                                                                               | 3.5        |                  | 0.8         | v     |

| Write Pulse Width (Negative) Write Pulse Width (Positive)                                     | t <sub>w</sub>                                           | 7218A, B                                                                                      | 550<br>550 | 400<br>400       |             | ns    |

| Write Pulse Width (Negative)<br>Write Pulse Width (Positive)                                  | t <sub>w</sub>                                           | 7218C, D                                                                                      | 400<br>400 | 250<br>250       |             | ns    |

| Mode Hold Time                                                                                | t <sub>mh</sub>                                          | 7218A, B                                                                                      | -          | 150              |             | ns    |

| Mode Pulse Width                                                                              | t <sub>m</sub>                                           | 7218A, B                                                                                      | 500        |                  |             | ns    |

| Data Set Up Time                                                                              | t <sub>ds</sub>                                          |                                                                                               | 500        |                  |             | ns    |

| Data Hold Time                                                                                | t <sub>dh</sub>                                          |                                                                                               | 25         |                  |             | ns    |

| Digit Address Set Up Time<br>Digit Address Hold Time                                          | t <sub>das</sub><br>t <sub>dah</sub>                     | ICM7218C, D<br>ICM7218C, D                                                                    | 500<br>100 |                  |             | ns    |

| Data Input Impedance                                                                          | Z <sub>IN</sub>                                          | 5-10pF Gate Capacitance                                                                       |            | 10 <sup>10</sup> |             | Ohms  |

- Note 1: Due to the SCR structure inherent in the CMOS process used to fabricate these devices, connecting any terminal to a voltage greater than V\* or less than GROUND may cause destructive device latchup. For this reason it is recommended that no inputs from sources operating on a different power supply be applied to the device before its own supply is established, and when using multiple supply systems the supply to the ICM7218 should be turned on first.

- Note 2: These limits refer to the package and will not be obtained during normal operation. Derate above 50° C by 25mW per °C.

Note 3: In the ICM7218C and D (random access versions) the Hexa/Code B/Shutdown Input (Pin 9) has internal biasing resistors to hold it at V\*/2 when Pin 9 is open circuited. These resistors consume power and result in a Quiescent Supply Current (I<sub>Q</sub>) of typically 50µA. The ICM7218A and B devices do not have these biasing resistors and thus are not subject to this condition.

The electrical characteristics above are a reproduction of a portion of Intersil's copyrighted (1983, 1984) data book. This information does not constitute any representation by Maxim that Intersil's products will perform in accordance with these specifications. The Electrical Characteristics Table along with the descriptive excepts from manufacturer's data sheet have been included in this data sheet solely for comparative purposes.

# **IVIIXIIVI ADVANTAGE™**8 Digit LED Display Driver

- ♦ 200ns Write Pulse Width

- ♦ Zero Hold Time Mode, Data and Address

- ♦ Single Digit Update Mode ICM7218A, B

- ♦ Guaranteed Interdigit Blanking Time

- ♦ Increased LED Display Drive Current

- ♦ Improved ESD Protection (Note 4)

- ♦ Maxim Quality and Reliability

# ABSOLUTE MAXIMUM RATINGS: This device conforms to the Absolute Maximum Ratings on adjacent page. ELECTRICAL CHARACTERISTICS

$(V^{+} = 5V \pm 10\%, T_{A} = 25^{\circ}C)$

| PARAMETER                               | SYMBOL                                                   | CONDITIONS                                                                                                                                | MIN               | TYP                      | MAX               | UNITS                                        |

|-----------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|-------------------|----------------------------------------------|

| Supply Voltage                          | V <sup>+</sup>                                           | $-20^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ +85° C Operating Data Retention                                                              | 4 2               |                          | 6<br>6            | V                                            |

| Shutdown Supply Current                 | I <sub>o</sub>                                           | ICM7218A, B<br>ICM7218C, D (3 level input open)                                                                                           |                   | 5<br>25                  | 300<br>300        | μΑ                                           |

| Operating Supply Current                | I <sub>OP</sub>                                          | Decoding all 8's, display open No Decode, display outputs open Display blank, driving display Decoding all 8's and D.P.s, driving display |                   | 200<br>200<br>200<br>240 | 450<br>450<br>450 | μ <b>Α</b><br>μ <b>Α</b><br>μ <b>Α</b><br>mA |

| Digit Drive Current                     | I <sub>DIG</sub>                                         | Common Anode V <sub>OUT</sub> = V <sup>+</sup> - 2.0V<br>Common Cathode V <sub>OUT</sub> = 1.0V                                           | <b>-200</b><br>50 | <b>-300</b><br>70        |                   | mA<br>mA                                     |

| Digit Leakage Current                   | I <sub>DLK</sub>                                         | Shutdown, V <sup>+</sup> = 5V<br>Common Anode, V <sub>OUT</sub> = 0V<br>Common Cathode, V <sub>OUT</sub> = 5V                             |                   | -10<br>10                | -100<br>100       | μΑ<br>μΑ                                     |

| Peak Segment Drive Current              | I <sub>SEG</sub>                                         | Common Anode $V_{OUT} = 1.5V$<br>Common Cathode $V_{OUT} = V^{+} - 2.0V$                                                                  | 20<br>-10         | 30<br>-20                |                   | mA                                           |

| Segment Leakage Current                 | I <sub>SLK</sub>                                         | Shutdown, V* = 5V<br>Common Anode, V <sub>OUT</sub> = 5V<br>Common Cathode, V <sub>OUT</sub> = 0V                                         |                   | -1<br>1                  | -50<br>50         | μA<br>μA                                     |

| Input Leakage Current                   | I <sub>IL</sub>                                          | All inputs except pin 9 of ICM7218C, D V = 5V, -20°C $\leq$ T $_{A} \leq$ +85°C $V_{IN}$ = 0V $V_{IN}$ = 5V                               |                   | -0.01<br>0.01            | -1<br>1           | μ <b>Α</b><br>μ <b>Α</b>                     |

| Display Scan Rate                       | f <sub>MUX</sub>                                         | V <sup>+</sup> = 5V                                                                                                                       | 75                | 250                      |                   | Hz                                           |

| Interdigit Blanking Time                | t <sub>idb</sub>                                         | V <sup>+</sup> = 5V                                                                                                                       | 2                 | 10                       |                   | μs                                           |

| Three Level Input                       | V <sub>INH</sub><br>V <sub>INF</sub><br>V <sub>INL</sub> | Pin 9, ICM7218 C, D only, V* = 5V<br>Input "high" voltage<br>Floating input<br>Input "low" voltage                                        | 4.2<br>2.0        |                          | 3.0<br>0.8        | V<br>V                                       |

| Three Level Input Impedance             | Z <sub>IN</sub>                                          | Pin 9, ICM7218C, D only                                                                                                                   | 50                | 100                      |                   | kΩ                                           |

| Input High Voltage<br>Input Low Voltage | V <sub>IH</sub>                                          | All inputs except pin 9 of ICM7218C, D $-20^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +85^{\circ}\text{C}$                            | 2.0               |                          | 0.8               | V                                            |

| Write Pulse Width (Low)                 | t <sub>wi</sub>                                          |                                                                                                                                           | 200               | 100                      |                   | ns                                           |

| Write Pulse Width (High)                | t <sub>wh</sub>                                          |                                                                                                                                           | 1.0               |                          |                   | μs                                           |

| Input Setup Time                        | t <sub>ids</sub>                                         | All inputs except pin 9 of ICM7218C, D (Note 5)                                                                                           | 250               | 150                      |                   | ns                                           |

| Input Hold Time                         | t <sub>idh</sub>                                         | All inputs except pin 9 of ICM7218C, D (Note 5)                                                                                           | 0                 | -20                      |                   | ns                                           |

Note 4: All pins are designed to withstand electrostatic discharge (ESD) levels in excess of 2000V (Mil Std 883B Method 3015.1 Test Circuit).

Note 5: This specification replaces the original manufacturer's separate specifications for data, address, and mode inputs,

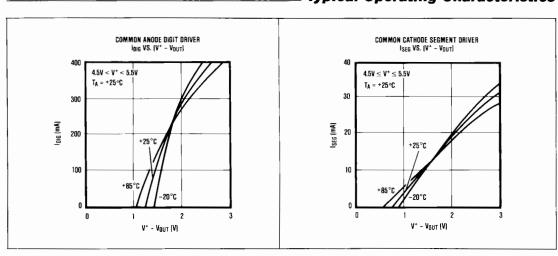

## **Typical Operating Characteristics**

#### **ICM7218 BLOCK DIAGRAMS**

Table 1. Input Definitions, ICM7218A and ICM7218B

Note: Pin Configurations for the ICM7218A/B are shown on last page.

| INPUT                                | PIN        | STATE       | FUNCTION                                                      |  |

|--------------------------------------|------------|-------------|---------------------------------------------------------------|--|

| WRITE                                | 8          | High<br>Low | Input Not Loaded Into Memory Input Loaded Into Memory         |  |

| MODE                                 | 9          | High<br>Low | Loads Control Word on WR<br>Loads Input Data on WR            |  |

| ID0-ID2,<br>DIGIT ADDRESS            | 12, 11, 13 | High<br>Low | Loads "one"<br>Loads "zero"                                   |  |

| ID3, BANK SELECT                     | 14         | High<br>Low | Select RAM Bank A (Hex or Code B Select RAM Bank B Data only) |  |

| ID4, SHUTDOWN<br>(MODE High)         | 10         | High<br>Low | Normal Operation<br>Shutdown                                  |  |

| ID5, DECODE/NO DECODE<br>(MODE High) | 6          | High<br>Low | No Decode<br>Decode                                           |  |

| ID6, HEX/CODE B<br>(MODE High)       | 5          | High<br>Low | Hexadecimal Decoding Code B Decoding                          |  |

| ID7, DATA COMING<br>(MODE High)      | 7          | High<br>Low | Data Coming (control word) No Data Coming (control word)      |  |

| ID0-ID7, INPUT DATA<br>(MODE Low)    | 5-7, 10-14 | High<br>Low | Loads "one" (Note 1)<br>Loads "zero" (Note 1)                 |  |

Note 1: A "zero" or low level on ID7 turns ON the decimal point. In the NO DECODE mode, a "one" or high input turns ON the corresponding segment, except for the decimal point which is turned OFF by a high level on ID7.

#### \_ Detailed Description Input Data Formats

The ICM7218A and ICM7218B have three possible data formats: Hexadecimal, Code B, and No Decode. Figure 7 lists the character sets for the decode modes.

The data format of the ICM7218A/B is selected by writing to bits ID4, ID5, and ID6 of the control register (See Table 1, Input Definitions). Hexadecimal and Code B data is entered via ID0-ID3 while ID7 controls the decimal point.

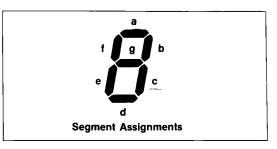

The No Decode mode of the ICM7218A and ICM7218B allows the direct segment-by-segment control of all 64 segments driven by the ICM7218. In the No Decode mode, the inputs directly control the outputs as follows:

| Data Input            | ID7              | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |

|-----------------------|------------------|-----|-----|-----|-----|-----|-----|-----|

| Controlled<br>Segment | Decimal<br>Point | Α   | В   | С   | Ε   | G   | F   | D   |

An input high level turns on the respective segment, except for the decimal point, which is turned on by an input low level on ID7.

The ICM7218C and ICM7218D have only Hexadecimal and Code B formats. The MODE input, pin 9, a three level input, selects the Hexadecimal format when driven high, the Code B format when floating or

driven to mid-supply, and the shutdown mode when driven low

#### Shutdown and Display Blanking

When shutdown, the ICM7218 enters a low power standby mode which typically uses only  $10\mu A$  of supply current. In this mode the ICM7218 turns off the multiplex scan oscillator as well as the digit and segment drivers, however input data can still be entered when in the shutdown mode. Data is retained in memory even with the supply voltage as low as 2V. The ICM7218A/B is shutdown by writing a control word with Shutdown (ID4) low. The ICM7218C/D is put into shutdown mode by driving MODE low.

The ICM7218 operating current with the display blanked is  $200\mu\text{A}$ . All versions of the ICM7218 can be blanked by writing Hex FF to all digits and selecting Code B format. The ICM7218A and ICM7218B can also be blanked by selecting No Decode mode and writing Hex 80 to all digits.

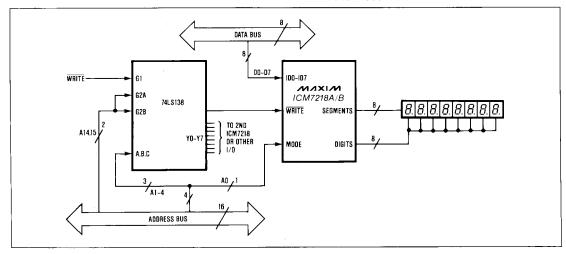

#### Microprocessor Interface, ICM7218A and ICM7218B

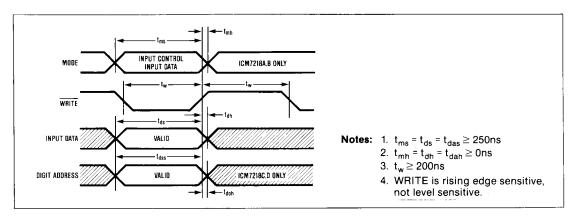

All Maxim ICM7218A/B inputs, including MODE, feature a 250ns minimum data setup and 0ns hold time. With a 200ns minimum write pulse, the ICM7218 can directly interface to most microprocessor buses. Input logic levels are TTL and CMOS compatible. Figure 8 shows a typical method of driving the ICM7218A/B

Table 2. Input Definitions, ICM7218C and ICM7218D

Note: Pin Configurations for the ICM7218C/D are shown on last page.

| INPUT                             | PIN        | STATE                | FUNCTION                                                 |

|-----------------------------------|------------|----------------------|----------------------------------------------------------|

| WRITE                             | 8          | High<br>Low          | Input Not Loaded Into Memory<br>Input Loaded Into Memory |

| MODE<br>(Note 1)                  | 9          | High<br>Float<br>Low | Hexadecimal Decode<br>Code B Decode<br>Shutdown          |

| DA0-DA2,<br>DIGIT ADDRESS         | 5, 6, 10   | High<br>Low          | Loads "ones"<br>Loads "zeros"                            |

| ID0-ID3, INPUT DATA and ID7, D.P. | 11-14<br>7 | High<br>Low          | Loads "ones"<br>Loads "zeros"                            |

Note 1: Pin 9 of the ICM7218C and ICM7218D controls the selection of Hex, Code B, and Shutdown modes and is independent of the WRITE pulse.

Note 2: A "zero" or low level on ID7 turns ON the decimal point segment.

from a microprocessor bus. The MODE input is driven by A0 and writing to an odd address updates the control register.

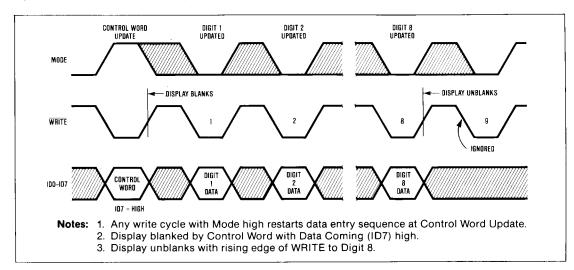

The ICM7218A/B has three data entry modes: control word update without data update, 8 digit data update, and single digit data update. In all three modes the control register is first updated by pulsing the WRITE input while the MODE input is high, thereby latching data into the control register. The control register selects Shutdown, Decode/No Decode, and Hex/Code B operation as shown in Table 1. A unique feature of the Maxim ICM7218A/B is that there are two banks of internal RAM in the Hexadecimal and Code B display formats. ID3 selects which bank of the internal RAM is displayed.

The logic state of DATA COMING (ID7) is also latched during a control register update. If the latched value of DATA COMING (ID7) is high, the display is blanked and an 8 digit data update is initiated. The next 8 write pulses latch data into the 8 bytes of RAM onboard the ICM7218A/B, starting with digit 1 and ending with digit 8. After the eighth write pulse, the display unblanks and the new data is displayed. Additional write pulses after the eighth pulse are ignored. All 8 digits are displayed in the data format (Hex/Code B/No Decode) specified by the control word that preceded the 8 digit update.

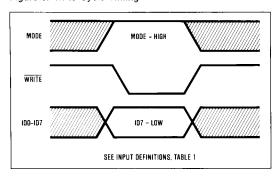

The control register can be rewritten without updating all 8 digits by writing to the ICM7218A/B with MODE high and DATA COMING low. No further action is necessary.

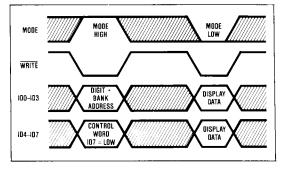

#### Single Digit Update Mode

The Maxim ICM7218A/B has a "single digit update" mode which allows one digit to be changed without updating the entire display. First the control register

is updated with MODE high, DATA COMING (ID7) low, the desired data format on ID4 and ID6, and the address of the digit to be updated on data lines ID0-ID2 (See Table 3). A second write to the ICM7218, this time with MODE low, transfers the data from ID0-ID7 into the selected digit's RAM location. The data format (Hex/Code B/No Decode) can be specified independently for each digit when in the single digit update mode.

#### Compatibility with the Intersil ICM7218A and ICM7218B

The Maxim ICM7218A/B is upwardly compatible with the Intersil ICM7218A/B. The Maxim ICM7218A/B adds two functions: bank select and single digit update.

ID0-ID3 are "don't care" when writing a control word to the Intersil ICM7218A/B. When writing a control word to the Maxim ICM7218A/B, ID0-ID2 select the address for a single digit update, while ID3 selects either bank A or bank B for Hex and Code B data. ID3 is a "don't care" for No Decode data. The bank select feature is upwardly compatible with the Intersil ICM7218A/B; software written for the Intersil ICM7218A/B will work with the Maxim ICM7218A/B provided all control word updates have the same value for ID3, either high or low.

The single digit update is upwardly compatible; it is an invalid operation with the Intersil ICM7218A/B and is unlikely to occur in software originally written for the Intersil ICM7218A/B.

Figure 3. Write Cycle Timing

Figure 4. Control Word Update Timing—ICM7218A/B

Figure 5. Single Digit Update Timing—ICM7218A/B

Figure 6. 8 Digit Update Timing—ICM7218A/B

| ID3 | ID2 | ID1 | ID0 | HEXADECIMAL | CODE B  |

|-----|-----|-----|-----|-------------|---------|

| 0   | 0   | 0   | 0   | 0           | 0       |

| 0   | 0   | 0   | 1   | 1           | 1       |

| 0   | 0   | 1   | 0   | 2           | 2       |

| 0   | 0   | 1   | 1   | 3           | 3       |

| 0   | 1   | 0   | 0   | 4           | 4       |

| 0   | 1   | 0   | 1   | 5           | 5       |

| 0   | 1   | 1   | 0   | 6           | 6       |

| 0   | 1   | 1   | 1   | 7           | 7       |

| 1   | 0   | 0   | 0   | 8           | 8       |

| 1   | 0   | 0   | 1   | 9           | 9       |

| 1   | 0   | 1   | 0   | А           | -       |

| 1   | 0   | 1   | 1   | р           | E       |

| 1   | 1   | 0   | 0   | С           | н       |

| 1   | 1   | 0   | 1   | d           | L       |

| 1   | 1   | 1   | 0   | E           | Р       |

| 1   | 1   | 1   | 1   | F           | (Blank) |

Figure 7. Display Font

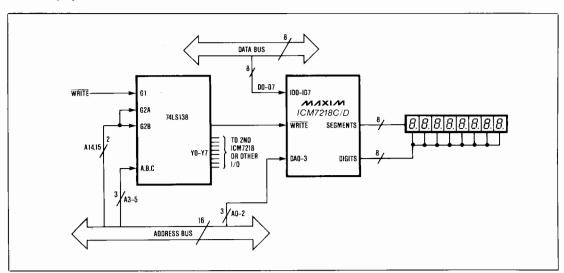

#### Microprocessor Interface, ICM7218C and ICM7218D

All Maxim ICM7218C and IMC7218D inputs are TTL and CMOS compatible with the exception of the three-level input, HEX/CODE B/SHUTDOWN (Pin 9). All other data and address inputs have identical 250ns setup and 0ns hold times. The minimum write pulse width is 200ns, allowing direct interface to most microprocessor buses. Figure 9 shows a typical ICM7218C/D bus interface. The 8 digits of the ICM7218C/D are addressed as 8 contiguous bytes of RAM

The interface to the ICM7218C and ICM7218D is similar to that of a RAM. Select the digit to be updated with the address lines DA0-DA2, place the data to be written on ID0-ID3 and ID7, then pulse the WRITE input low.

Since the ICM7218C/D does not have a control register, Hexadecimal or Code B font selection and shutdown mode are directly controlled through the three-level input at Pin 9. The ICM7218C/D does not have a No Decode mode.

Figure 8. ICM7218A/B μP Bus Interface

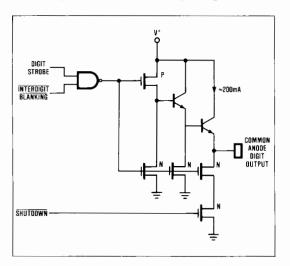

# Applications Information Common Anode Display Interface, ICM7218A and ICM7218C

The common anode digit and segment driver output schematics are shown in Figures 10 and 11. The common anode digit driver output impedance is approximately 4 ohms. This provides a nearly constant voltage to the display digits. The N-channel segment driver output impedance of  $50\Omega$  limits the segment current to approximately 30mA peak current per segment. Segment current limiting resistors are NOT required. Both the segment and digit outputs can directly drive the display.

Each segment's current is not significantly affected by whether other segments are on or off. This is because the segment driver output impedance is much higher than that of the digit driver. This feature is important in bar graph applications, where each bar graph element should be the same brightness, independent of the number of elements turned on.

#### Common Cathode Display Interface, ICM7218B and ICM7218D

The common cathode digit and segment driver output schematics are shown in Figures 12 and 13. The N-channel digit drivers have an output impedance of approximately 15Ω. The NPN segment drivers have an output impedance of approximately 75 ohms. The common cathode display driver output currents are only 1/4 the common anode display driver currents. Therefore, the ICM7218A and ICM7218C common anode display drivers are recommended for those

Table 3. Digit Addressing

|     | DATA LINE |     | Selected |

|-----|-----------|-----|----------|

| ID2 | ID1       | ID0 | Digit    |

| 0   | 0         | 0   | D1       |

| 0   | 0         | 1   | D2       |

| 0   | 1         | 0   | D3       |

| 0   | 1         | 1   | D4       |

| 1   | 0         | 0   | D5       |

| 1   | 0         | 1   | D6       |

| 1   | 1         | 0   | D7       |

| 1   | 1         | 1   | D8       |

applications where high brightness is desired. The ICM7218B and ICM7218D common cathode display drivers are suitable for driving bubble-lensed monolithic 7 segment displays. They can also drive individual LED displays up to 0.3" height when high brightness is not required.

#### **Display Multiplexing**

Each digit of the ICM7218 is on for approximately  $500\mu$ s, with a multiplexing frequency of approximately 250Hz. The interdigit blanking time is  $10\mu$ s typical,  $2\mu$ s minimum. The Maxim ICM7218 turns off both the digit drivers and the segment drivers during the interdigit blanking period. The digit multiplexing sequence is: D1, D7, D8, D6, D4, D3, D2, and D5.

Figure 9. ICM7218C/D  $\mu P$  Bus Interface

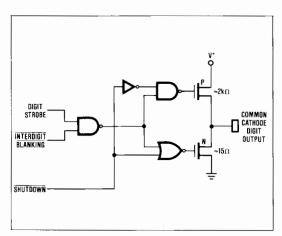

Figure 10. Common Anode Digit Driver

Figure 12. Common Cathode Digit Driver

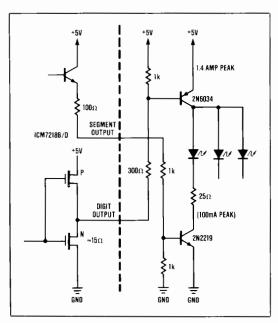

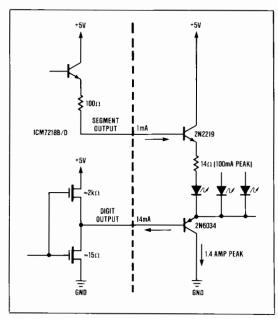

#### **Driving Larger Displays**

If very high display brightness is desired, the ICM7218 display driver outputs can be externally buffered. Figures 14 and 15 show how to drive either common anode or common cathode displays using the ICM7218B or ICM7218D. The Maxim ICM7218 has a guaranteed  $2\mu$ s interdigit blanking time. This eliminates the ghosting (faint display of the data from another digit) that would occur if the external buffer turnoff time were to overlap the beginning of the next digit period.

Another method of doubling display currents is to connect two digit outputs together and load the same

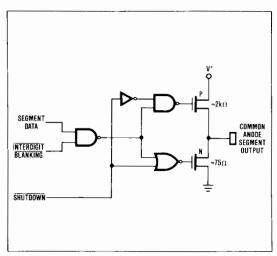

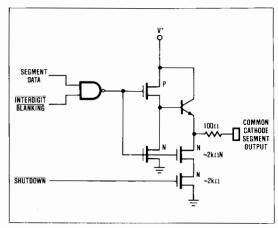

Figure 11. Common Anode Segment Driver

Figure 13. Common Cathode Segment Driver

data into both digits. This drives the display with the same peak current, but the average current doubles because each digit of the display is on for twice as long, i.e. for 1/4 duty cycle rather than 1/8.

#### Three Level Input, ICM7218C and ICM7218D.

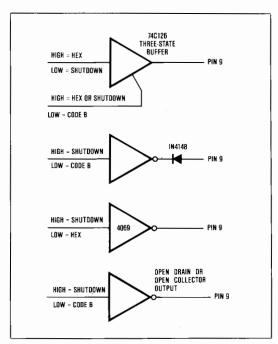

As shown in Table 1, pin 9 controls three functions: Hexadecimal display decoding, Code B display decoding, and shutdown mode. In many applications pin 9 will be permanently wired to one state. When pin 9 cannot be permanently left in one state, use the circuits illustrated in Figure 16 to drive this three level input.

Figure 14. Driving Larger Common Anode Displays with External Transistors

Figure 16. Drive Circuits for ICM7218C/D MODE Input

Figure 15. Driving Larger Common Cathode Displays with External Transistors

#### Power Supply Bypassing

Connect a minimum of  $47\mu\text{F}$  in parallel with  $0.1\mu\text{F}$  between V $^{+}$  and ground. These capacitors should be placed in close proximity to the ICM7218 to reduce the power supply ripple caused by the 200mA multiplexed LED display drive current pulses.

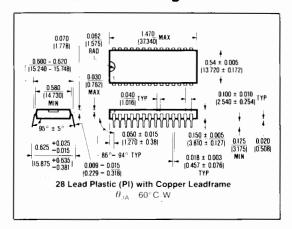

#### Package Information

#### Pin Configurations

#### \_ Ordering Information (continued)

| PART        | TEMP. RANGE    | PACKAGE           |

|-------------|----------------|-------------------|

| ICM7218AI/D | -20°C to +85°C | Dice              |

| ICM7218AIQI | -20°C to +85°C | 28 Lead Quad Pack |

| ICM7218BI/D | -20°C to +85°C | Dice              |

| ICM7218BIQI | -20°C to +85°C | 28 Lead Quad Pack |

| ICM7218CI/D | -20°C to +85°C | Dice              |

| ICM7218CIQI | -20°C to +85°C | 28 Lead Quad Pack |

| ICM7218DI/D | -20°C to +85°C | Dice              |

| ICM7218DIQI | -20°C to +85°C | 28 Lead Quad Pack |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.