Data Sheet October 19, 2005 FN9238.0

# Industry Standard Single-Ended Current Mode PWM Controller

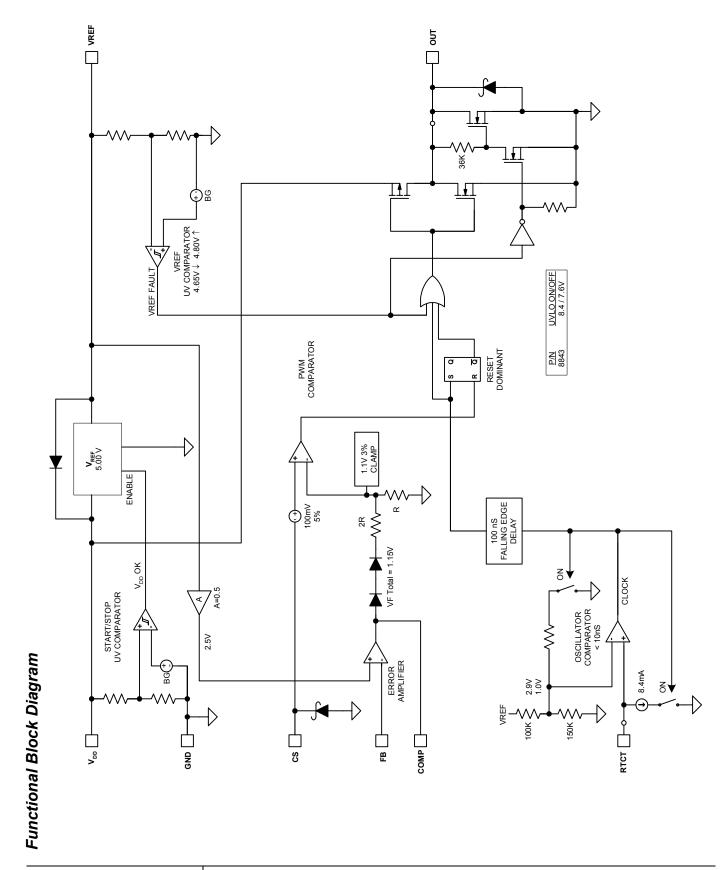

The ISL8843 is an industry standard drop-in replacement for the popular 28C43 and 18C43 PWM controllers suitable for a wide range of power conversion applications including boost, flyback, and isolated output configurations. Its fast signal propagation and output switching characteristics make this an ideal product for existing and new designs.

Features include 30V operation, low operating current,  $90\mu A$  start-up current, adjustable operating frequency to 2MHz, and high peak current drive capability with 20ns rise and fall times.

| PART NUMBER | ART NUMBER RISING UVLO MA |      |  |  |

|-------------|---------------------------|------|--|--|

| ISL8843     | 8.4V                      | 100% |  |  |

## **Ordering Information**

| PART<br>NUMBER           | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE                | PKG.<br>DWG. # |

|--------------------------|-----------------|---------------------|------------------------|----------------|

| ISL8843ABZ<br>(See Note) | 8843 ABZ        | -40 to 105          | 8 Ld SOIC<br>(Pb-free) | M8.15          |

| ISL8843AUZ<br>(See Note) | 8843Z           | -40 to 105          | 8 Ld MSOP<br>(Pb-free) | M8.118         |

| ISL8843MBZ<br>(See Note) | 8843 MBZ        | -55 to 125          | 8 Ld SOIC<br>(Pb-free) | M8.15          |

| ISL8843MUZ<br>(See Note) | 843MZ           | -55 to 125          | 8 Ld MSOP<br>(Pb-free) | M8.118         |

Add -T to part number for Tape and Reel packaging.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- · 1A MOSFET gate driver

- 90μA start-up current, 125μA maximum

- · 35ns propagation delay current sense to output

- · Fast transient response with peak current mode control

- 30V operation

- · Adjustable switching frequency to 2MHz

- · 20ns rise and fall times with 1nF output load

- Trimmed timing capacitor discharge current for accurate deadtime/maximum duty cycle control

- · 1.5MHz bandwidth error amplifier

- Tight tolerance voltage reference over line, load, and temperature

- · ±3% current limit threshold

- Pb-free plus anneal available and ELV, WEEE, RoHS Compliant

## **Applications**

- · Telecom and datacom power

- · Wireless base station power

- · File server power

- · Industrial power systems

- · PC power supplies

- · Isolated buck and flyback regulators

- · Boost regulators

#### Pinout

ISL8843

(8 LD SOIC, MSOP)

TOP VIEW

COMP 1 8 VREF

FB 2 7 VDD

CS 3 6 OUT

RTCT 4 5 GND

+ C16 +3.3v ☐ RETURN **∆** +1.8v ₩₩ R20 C14 R17 R16 U2 C19 R13 SR 🔻 2 % 2 % R21 <u>′</u>8 CS VDD FB OUT RTCT GND ISL8843 Ξ R27 **★** 4 CR2 \$ £ R22 74 C<sub>R</sub>6 န 2 8 4 4 82 2 g R6 رالا ۱۳۰۸ Ů N× 36-75V

## **Absolute Maximum Ratings**

| V |

|---|

| V |

| V |

| Α |

|   |

| V |

| V |

| V |

|   |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | $\theta_{JA}$ (°C/W) |

|------------------------------------------|----------------------|

| SOIC Package                             | 100                  |

| MSOP Package                             |                      |

| Maximum Junction Temperature             |                      |

| Maximum Storage Temperature Range65      | s°C to 150°C         |

| Maximum Lead Temperature (Soldering 10s) | 300°C                |

| (SOIC, MSOP - Lead Tips Only)            |                      |

## **Operating Conditions**

| Temperature Range              |               |

|--------------------------------|---------------|

| ISL8843AxZ                     | 40°C to 105°C |

| ISL8843MxZ                     | 55°C to 125°C |

| Supply Voltage Range (Typical) |               |

| ISL8843                        |               |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES

- 1. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 2. All voltages are with respect to GND.

## **Electrical Specifications**

**ISL8843A** - Recommended operating conditions unless otherwise noted. Refer to Block Diagram and Typical Application schematic.  $V_{DD}$  = 15V, RT = 10kΩ, CT = 3.3nF,  $T_A$  = -40 to 105°C (Note 3) Typical values are at  $T_A$  = 25°C

| PARAMETER                                        | TEST CONDITIONS                                             | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|-------|

| UNDERVOLTAGE LOCKOUT                             |                                                             |       |       | •     |       |

| START Threshold                                  |                                                             | 8.0   | 8.4   | 9.0   | V     |

| STOP Threshold                                   |                                                             | 7.3   | 7.6   | 8.0   | V     |

| Hysteresis                                       |                                                             | -     | 0.8   | -     | V     |

| Startup Current, I <sub>DD</sub>                 | V <sub>DD</sub> < START Threshold                           | -     | 90    | 125   | μΑ    |

| Operating Current, I <sub>DD</sub>               | (Note 4)                                                    | -     | 2.9   | 4.0   | mA    |

| Operating Supply Current, ID                     | Includes 1nF GATE loading                                   | -     | 4.75  | 5.5   | mA    |

| REFERENCE VOLTAGE                                |                                                             |       |       | •     | •     |

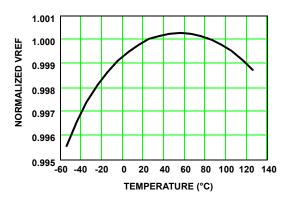

| Overall Accuracy                                 | Over line (V <sub>DD</sub> = 12V to 18V), load, temperature | 4.925 | 5.000 | 5.050 | V     |

| Long Term Stability                              | T <sub>A</sub> = 125°C, 1000 hours (Note 5)                 | -     | 5     | -     | mV    |

| Current Limit, Sourcing                          |                                                             | -20   | -     | -     | mA    |

| Current Limit, Sinking                           |                                                             | 5     | -     | -     | mA    |

| CURRENT SENSE                                    |                                                             |       |       |       |       |

| Input Bias Current                               | V <sub>CS</sub> = 1V                                        | -1.0  | -     | 1.0   | μА    |

| CS Offset Voltage                                | V <sub>CS</sub> = 0V (Note 5)                               | 95    | 100   | 105   | mV    |

| COMP to PWM Comparator Offset Voltage            | V <sub>CS</sub> = 0V (Note 5)                               | 0.80  | 1.15  | 1.30  | V     |

| Input Signal, Maximum                            |                                                             | 0.97  | 1.00  | 1.03  | V     |

| Gain, $A_{CS} = \Delta V_{COMP} / \Delta V_{CS}$ | 0 < V <sub>CS</sub> < 910mV, V <sub>FB</sub> = 0V           | 2.5   | 3.0   | 3.5   | V/V   |

| CS to OUT Delay                                  |                                                             | -     | 35    | 55    | ns    |

| ERROR AMPLIFIER                                  |                                                             |       |       |       |       |

| Open Loop Voltage Gain                           | (Note 5)                                                    | 60    | 90    | -     | dB    |

| Unity Gain Bandwidth                             | (Note 5)                                                    | 1.0   | 1.5   | -     | MHz   |

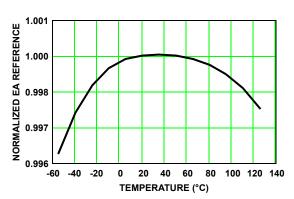

| Reference Voltage                                | V <sub>FB</sub> = V <sub>COMP</sub>                         | 2.475 | 2.500 | 2.530 | V     |

FN9238.0 October 19, 2005

## **Electrical Specifications**

**ISL8843A** - Recommended operating conditions unless otherwise noted. Refer to Block Diagram and Typical Application schematic.  $V_{DD}$  = 15V, RT = 10k $\Omega$ , CT = 3.3nF,  $T_A$  = -40 to 105°C (Note 3) Typical values are at  $T_A$  = 25°C (Continued)

| PARAMETER                                | PARAMETER TEST CONDITIONS                                                     |      | TYP  | MAX  | UNITS |

|------------------------------------------|-------------------------------------------------------------------------------|------|------|------|-------|

| FB Input Bias Current                    | V <sub>FB</sub> = 0V                                                          | -1.0 | -0.2 | 1.0  | μΑ    |

| COMP Sink Current                        | V <sub>COMP</sub> = 1.5V, V <sub>FB</sub> = 2.7V                              | 1.0  | -    | -    | mA    |

| COMP Source Current                      | V <sub>COMP</sub> = 1.5V, V <sub>FB</sub> = 2.3V                              | -0.4 | -    | -    | mA    |

| COMP VOH                                 | V <sub>FB</sub> = 2.3V                                                        | 4.80 | -    | VREF | V     |

| COMP VOL                                 | V <sub>FB</sub> = 2.7V                                                        | 0.4  | -    | 1.0  | V     |

| PSRR                                     | Frequency = 120Hz, V <sub>DD</sub> = 12V to 18V (Note 5)                      | 60   | 80   | -    | dB    |

| OSCILLATOR                               |                                                                               |      | •    | 1    | •     |

| Frequency Accuracy                       | Initial, T <sub>A</sub> = 25°C                                                | 48   | 51   | 53   | kHz   |

| Frequency Variation with V <sub>DD</sub> | T <sub>A</sub> = 25°C, (F <sub>30V</sub> - F <sub>9V</sub> )/F <sub>30V</sub> | -    | 0.2  | 1.0  | %     |

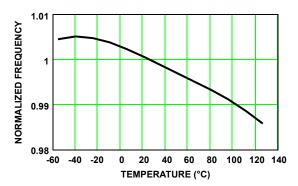

| Temperature Stability                    | (Note 5)                                                                      | -    | -    | 5    | %     |

| Amplitude, Peak to Peak                  | Static Test                                                                   | -    | 1.75 | -    | V     |

| RTCT Discharge Voltage (Valley Voltage)  | Static Test                                                                   | -    | 1.0  | -    | V     |

| Discharge Current                        | RTCT = 2.0V                                                                   | 6.5  | 7.8  | 8.5  | mA    |

| ОИТРИТ                                   |                                                                               |      |      | •    |       |

| Gate VOH                                 | V <sub>DD</sub> - OUT, I <sub>OUT</sub> = -200mA                              | -    | 1.0  | 2.0  | V     |

| Gate VOL                                 | OUT - GND, I <sub>OUT</sub> = 200mA                                           | -    | 1.0  | 2.0  | V     |

| Peak Output Current                      | C <sub>OUT</sub> = 1nF (Note 5)                                               | -    | 1.0  | -    | А     |

| Rise Time                                | C <sub>OUT</sub> = 1nF (Note 5)                                               | -    | 20   | 40   | ns    |

| Fall Time                                | C <sub>OUT</sub> = 1nF (Note 5)                                               | -    | 20   | 40   | ns    |

| GATE VOL UVLO Clamp Voltage              | VDD = 5V, I <sub>LOAD</sub> = 1mA                                             | -    | -    | 1.2  | V     |

| PWM                                      |                                                                               |      |      | •    | •     |

| Maximum Duty Cycle                       | COMP = VREF                                                                   | 93.5 | 95   | -    | %     |

| Minimum Duty Cycle                       | COMP = GND                                                                    | -    | -    | 0    | %     |

#### NOTES:

- 3. Specifications at -40°C and 105°C are guaranteed by 25°C test with margin limits.

- 4. This is the  $V_{DD}$  current consumed when the device is active but not switching. Does not include gate drive current.

- 5. Guaranteed by design, not 100% tested in production.

## **Electrical Specifications**

**ISL8843M** - Recommended operating conditions unless otherwise noted. Refer to Block Diagram and Typical Application schematic.  $V_{DD}$  = 15V, RT = 10k $\Omega$ , CT = 3.3nF,  $T_A$  = -55 to 125°C (Note 6), Typical values are at  $T_A$  = 25°C

| PARAMETER                                | TEST CONDITIONS                                             | MIN   | TYP   | MAX   | UNITS |  |  |

|------------------------------------------|-------------------------------------------------------------|-------|-------|-------|-------|--|--|

| UNDERVOLTAGE LOCKOUT                     |                                                             |       |       |       |       |  |  |

| START Threshold                          |                                                             | 8.0   | 8.4   | 9.0   | V     |  |  |

| STOP Threshold                           |                                                             | 7.3   | 7.6   | 8.0   | V     |  |  |

| Hysteresis                               |                                                             | -     | 0.8   | -     | V     |  |  |

| Startup Current, I <sub>DD</sub>         | V <sub>DD</sub> < START Threshold                           | -     | 90    | 125   | μΑ    |  |  |

| Operating Current, I <sub>DD</sub>       | (Note 7)                                                    | -     | 2.9   | 4.0   | mA    |  |  |

| Operating Supply Current, I <sub>D</sub> | Includes 1nF GATE loading                                   | -     | 4.75  | 5.5   | mA    |  |  |

| REFERENCE VOLTAGE                        |                                                             |       |       |       |       |  |  |

| Overall Accuracy                         | Over line (V <sub>DD</sub> = 12V to 18V), load, temperature | 4.900 | 5.000 | 5.050 | V     |  |  |

## **Electrical Specifications**

**ISL8843M** - Recommended operating conditions unless otherwise noted. Refer to Block Diagram and Typical Application schematic.  $V_{DD}$  = 15V, RT = 10k $\Omega$ , CT = 3.3nF,  $T_A$  = -55 to 125°C (Note 6), Typical values are at  $T_A$  = 25°C (Continued)

| PARAMETER                                        | TEST CONDITIONS                                                               | MIN   | TYP   | MAX   | UNITS |  |

|--------------------------------------------------|-------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Long Term Stability                              | T <sub>A</sub> = 125°C, 1000 hours (Note 8)                                   | -     | 5     | -     | mV    |  |

| Current Limit, Sourcing                          |                                                                               | -20   | -     | -     | mA    |  |

| Current Limit, Sinking                           |                                                                               | 5     | -     | -     | mA    |  |

| CURRENT SENSE                                    |                                                                               |       |       |       |       |  |

| Input Bias Current                               | V <sub>CS</sub> = 1V                                                          | -1.0  | -     | 1.0   | μА    |  |

| CS Offset Voltage                                | V <sub>CS</sub> = 0V (Note 8)                                                 | 95    | 100   | 105   | mV    |  |

| COMP to PWM Comparator Offset Voltage            | V <sub>CS</sub> = 0V (Note 8)                                                 | 0.80  | 1.15  | 1.30  | V     |  |

| Input Signal, Maximum                            |                                                                               | 0.97  | 1.00  | 1.03  | V     |  |

| Gain, $A_{CS} = \Delta V_{COMP} / \Delta V_{CS}$ | 0 < V <sub>CS</sub> < 910mV, V <sub>FB</sub> = 0V                             | 2.5   | 3.0   | 3.5   | V/V   |  |

| CS to OUT Delay                                  |                                                                               | -     | 35    | 60    | ns    |  |

| ERROR AMPLIFIER                                  | ·                                                                             |       |       |       | •     |  |

| Open Loop Voltage Gain                           | (Note 8)                                                                      | 60    | 90    | -     | dB    |  |

| Unity Gain Bandwidth                             | (Note 8)                                                                      | 1.0   | 1.5   | -     | MHz   |  |

| Reference Voltage                                | V <sub>FB</sub> = V <sub>COMP</sub>                                           | 2.460 | 2.500 | 2.535 | V     |  |

| FB Input Bias Current                            | V <sub>FB</sub> = 0V                                                          | -1.0  | -0.2  | 1.0   | μА    |  |

| COMP Sink Current                                | V <sub>COMP</sub> = 1.5V, V <sub>FB</sub> = 2.7V                              | 1.0   | -     | -     | mA    |  |

| COMP Source Current                              | V <sub>COMP</sub> = 1.5V, V <sub>FB</sub> = 2.3V                              | -0.4  | -     | -     | mA    |  |

| COMP VOH                                         | V <sub>FB</sub> = 2.3V                                                        | 4.80  | -     | VREF  | V     |  |

| COMP VOL                                         | V <sub>FB</sub> = 2.7V                                                        | 0.4   | -     | 1.0   | V     |  |

| PSRR                                             | Frequency = 120Hz, V <sub>DD</sub> = 12V to 18V (Note 8)                      | 60    | 80    | -     | dB    |  |

| OSCILLATOR                                       | ·                                                                             |       |       |       |       |  |

| Frequency Accuracy                               | Initial, T <sub>A</sub> = 25°C                                                | 48    | 51    | 53    | kHz   |  |

| Frequency Variation with V <sub>DD</sub>         | T <sub>A</sub> = 25°C, (F <sub>30V</sub> - F <sub>9V</sub> )/F <sub>30V</sub> | -     | 0.2   | 1.0   | %     |  |

| Temperature Stability                            | (Note 8)                                                                      | -     | -     | 5     | %     |  |

| Amplitude, Peak to Peak                          | Static Test                                                                   | -     | 1.75  | -     | V     |  |

| RTCT Discharge Voltage (Valley Voltage)          | Static Test                                                                   | -     | 1.0   | -     | V     |  |

| Discharge Current                                | RTCT = 2.0V                                                                   | 6.2   | 8.0   | 8.5   | mA    |  |

| ОИТРИТ                                           |                                                                               |       | !     | !     |       |  |

| Gate VOH                                         | V <sub>DD</sub> - OUT, I <sub>OUT</sub> = -200mA                              | -     | 1.0   | 2.0   | V     |  |

| Gate VOL                                         | OUT - GND, I <sub>OUT</sub> = 200mA                                           | -     | 1.0   | 2.0   | V     |  |

| Peak Output Current                              | C <sub>OUT</sub> = 1nF (Note 8)                                               | -     | 1.0   | -     | А     |  |

| Rise Time                                        | C <sub>OUT</sub> = 1nF (Note 8)                                               | -     | 20    | 40    | ns    |  |

| Fall Time                                        | C <sub>OUT</sub> = 1nF (Note 8)                                               | -     | 20    | 40    | ns    |  |

| GATE VOL UVLO Clamp Voltage                      | VDD = 5V, I <sub>LOAD</sub> = 1mA                                             | -     | -     | 1.2   | V     |  |

| PWM                                              | -                                                                             |       | ı     | 1     | 1     |  |

| Maximum Duty Cycle                               | COMP = VREF                                                                   | 93.5  | 95    | -     | %     |  |

| Minimum Duty Cycle                               | COMP = GND                                                                    | -     | -     | 0     | %     |  |

|                                                  |                                                                               |       |       |       | +     |  |

#### NOTES:

- 6. Specifications at -55°C and 125°C are guaranteed by 25°C test with margin limits.

- 7. This is the V<sub>DD</sub> current consumed when the device is active but not switching. Does not include gate drive current.

- 8. Guaranteed by design, not 100% tested in production.

## **Typical Performance Curves**

FIGURE 1. FREQUENCY vs TEMPERATURE

FIGURE 3. EA REFERENCE vs TEMPERATURE

## Pin Descriptions

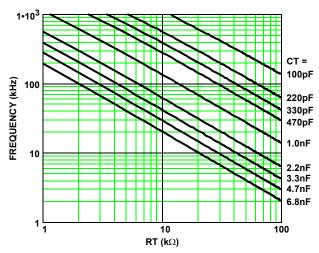

**RTCT** - This is the oscillator timing control pin. The operational frequency and maximum duty cycle are set by connecting a resistor, RT, between VREF and this pin and a timing capacitor, CT, from this pin to GND. The oscillator produces a sawtooth waveform with a programmable frequency range up to 2.0MHz. The charge time,  $T_C$ , the discharge time,  $T_D$ , the switching frequency, f, and the maximum duty cycle, Dmax, can be approximated from the following equations:

$$T_{C} \approx 0.533 \bullet RT \bullet CT$$

(EQ. 1)

$$T_{D} \approx -RT \bullet CT \bullet In \left( \frac{0.008 \bullet RT - 3.83}{0.008 \bullet RT - 1.71} \right)$$

(EQ. 2)

$$f = 1/(T_C + T_D)$$

(EQ. 3)

$$D = T_{C} \bullet f \tag{EQ. 4}$$

FIGURE 2. REFERENCE VOLTAGE vs TEMPERATURE

FIGURE 4. RTCT vs FREQUENCY

The formulae have increased error at higher frequencies due to propagation delays. Figure 4 may be used as a guideline in selecting the capacitor and resistor values required for a given frequency.

**COMP** - COMP is the output of the error amplifier and the input of the PWM comparator. The control loop frequency compensation network is connected between the COMP and FB pins.

**FB** - The output voltage feedback is connected to the inverting input of the error amplifier through this pin. The non-inverting input of the error amplifier is internally tied to a reference voltage.

**CS** - This is the current sense input to the PWM comparator. The range of the input signal is nominally 0 to 1.0V and has an internal offset of 100mV.

**GND -** GND is the power and small signal reference ground for all functions.

${\bf OUT}$  - This is the drive output to the power switching device. It is a high current output capable of driving the gate of a power MOSFET with peak currents of 1.0A. This GATE output is actively held low when  ${\bf V}_{DD}$  is below the UVLO threshold.

${

m V_{DD}}$  -  ${

m V_{DD}}$  is the power connection for the device. The total supply current will depend on the load applied to OUT. Total  ${

m I_{DD}}$  current is the sum of the operating current and the average output current. Knowing the operating frequency, f, and the MOSFET gate charge, Qg, the average output current can be calculated from:

$$I_{OUT} = Qg \times f$$

(EQ. 5)

To optimize noise immunity, bypass  $V_{DD}$  to GND with a ceramic capacitor as close to the  $V_{DD}$  and GND pins as possible.

**VREF** - The 5.00V reference voltage output. +1.0/-1.5% tolerance over line, load and operating temperature. Bypass to GND with a  $0.1\mu F$  to  $3.3\mu F$  capacitor to filter this output as needed.

## Functional Description

#### **Features**

The ISL8843 current mode PWM makes an ideal choice for low-cost flyback and forward topology applications. With its greatly improved performance over industry standard parts, it is the obvious choice for new designs or existing designs which require updating.

#### Oscillator

The ISL8843 has a sawtooth oscillator with a programmable frequency range to 2MHz, which can be programmed with a resistor from VREF and a capacitor to GND on the RTCT pin. (Please refer to Figure 4 for the resistor and capacitance required for a given frequency.)

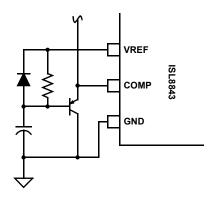

#### Soft-Start Operation

Soft-start must be implemented externally. One method, illustrated below, clamps the voltage on COMP.

FIGURE 5. SOFT-START

#### Gate Drive

The ISL8843 is capable of sourcing and sinking 1A peak current. To limit the peak current through the IC, an optional external resistor may be placed between the totem-pole output of the IC (OUT pin) and the gate of the MOSFET. This small series resistor also damps any oscillations caused by the resonant tank of the parasitic inductances in the traces of the board and the FET's input capacitance.

#### Slope Compensation

For applications where the maximum duty cycle is less than 50%, slope compensation may be used to improve noise immunity, particularly at lighter loads. The amount of slope compensation required for noise immunity is determined empirically, but is generally about 10% of the full scale current feedback signal. For applications where the duty cycle is greater than 50%, slope compensation is required to prevent instability.

Slope compensation may be accomplished by summing an external ramp with the current feedback signal or by subtracting the external ramp from the voltage feedback error signal. Adding the external ramp to the current feedback signal is the more popular method.

From the small signal current-mode model [1] it can be shown that the naturally-sampled modulator gain, Fm, without slope compensation, is

$$Fm = \frac{1}{SnTsw}$$

(EQ. 6)

where Sn is the slope of the sawtooth signal and Tsw is the duration of the half-cycle. When an external ramp is added, the modulator gain becomes

$$Fm = \frac{1}{(Sn + Se)Tsw} = \frac{1}{m_cSnTsw}$$

(EQ. 7)

where Se is slope of the external ramp and

$$m_{c} = 1 + \frac{Se}{Sn}$$

(EQ. 8)

The criteria for determining the correct amount of external ramp can be determined by appropriately setting the damping factor of the double-pole located at the switching frequency. The double-pole will be critically damped if the Q-factor is set to 1, over-damped for Q < 1, and under-damped for Q > 1. An under-damped condition may result in current loop instability.

$$Q = \frac{1}{\pi(m_c(1-D)-0.5)}$$

(EQ. 9)

where D is the percent of on time during a switching cycle. Setting Q = 1 and solving for Se yields

$$S_e = S_n \left( \left( \frac{1}{\pi} + 0.5 \right) \frac{1}{1 - D} - 1 \right)$$

(EQ. 10)

Since Sn and Se are the on time slopes of the current ramp and the external ramp, respectively, they can be multiplied by Ton to obtain the voltage change that occurs during Ton.

$$V_e = V_n \left( \left( \frac{1}{\pi} + 0.5 \right) \frac{1}{1 - D} - 1 \right)$$

(EQ. 11)

where Vn is the change in the current feedback signal ( $\Delta I$ ) during the on time and Ve is the voltage that must be added by the external ramp.

For a flyback converter, Vn can be solved for in terms of input voltage, current transducer components, and primary inductance, yielding

$$V_{e} \, = \, \frac{D \cdot T_{SW} \cdot V_{IN} \cdot R_{CS}}{L_{p}} \bigg( \bigg( \frac{1}{\pi} + 0.5 \bigg) \frac{1}{1-D} - 1 \bigg) \hspace{1cm} V \hspace{1cm} \text{(EQ. 12)}$$

where  $R_{CS}$  is the current sense resistor,  $T_{SW}$  is the switching frequency,  $L_p$  is the primary inductance,  $V_{IN}$  is the minimum input voltage, and D is the maximum duty cycle.

The current sense signal at the end of the ON time for CCM operation is:

$$V_{CS} = \frac{N_S \cdot R_{CS}}{N_p} \left( I_O + \frac{(1 \cdot D) \cdot V_O \cdot T_{SW}}{2L_S} \right) \qquad V$$

(EQ. 13)

where  $V_{CS}$  is the voltage across the current sense resistor,  $L_s$  is the secondary winding inductance, and  $I_O$  is the output current at current limit. Equation 13 assumes the voltage drop across the output rectifier is negligible.

Since the peak current limit threshold is 1.00V, the total current feedback signal plus the external ramp voltage must sum to this value when the output load is at the current limit threshold.

$$V_{e} + V_{CS} = 1$$

(EQ. 14)

Substituting Equations and 13 into Equation 14 and solving for  $R_{CS}$  yields

$$R_{CS} = \frac{1}{\frac{D \cdot T_{sw} \cdot V_{IN}}{L_p} \cdot \left(\frac{\frac{1}{\pi} + 0.5}{1 - D} - 1\right) + \frac{N_s}{N_p} \cdot \left(I_O + \frac{(1 - D) \cdot V_O \cdot T_{sw}}{2L_s}\right)}$$

(EQ. 15)

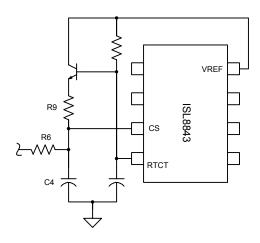

Adding slope compensation is accomplished in the ISL8843 using an external buffer transistor and the RTCT signal. A typical application sums the buffered RTCT signal with the current sense feedback and applies the result to the CS pin as shown in Figure 6.

9

FIGURE 6. SLOPE COMPENSATION

Assuming the designer has selected values for the RC filter (R6 and C4) placed on the CS pin, the value of R9 required to add the appropriate external ramp can be found by superposition.

$$V_{e} = \frac{1.9D \cdot R6}{R6 + R9} \qquad V \tag{EQ. 16}$$

Rearranging to solve for R9 yields

$$R9 = \frac{(1.9D - V_e) \cdot R6}{V_e} \qquad \Omega$$

(EQ. 17)

The value of  $R_{CS}$  determined in Equation 15 must be rescaled so that the current sense signal presented at the CS pin is that predicted by Equation 13. The divider created by R6 and R9 makes this necessary.

$$R'_{CS} = \frac{R6 + R9}{R9} \cdot R_{CS}$$

(EQ. 18)

Example:

V<sub>IN</sub> = 12V

$V_O = 48V$

$L_{s} = 800 \mu H$

Ns/Np = 10

$Lp = 8.0 \mu H$

$I_{O} = 200 \text{mA}$

Switching Frequency, Fsw = 200kHz

Duty Cycle, D = 28.6%

$R6 = 499\Omega$

Solve for the current sense resistor,  $R_{\mbox{\footnotesize{CS}}}$ , using Equation 15

$R_{CS} = 295 m\Omega$ .

Determine the amount of voltage, Ve, that must be added to the current feedback signal using Equation 12.

Ve = 92.4mV

Using Equation 17, solve for the summing resistor, R9, from CT to CS.

$R9 = 2.43k\Omega$

Determine the new value of  $R_{CS}$ ,  $R'_{CS}$ , using Equation 18.

$R'_{CS} = 356m\Omega$

Additional slope compensation may be considered for design margin. The above discussion determines the minimum external ramp that is required. The buffer transistor used to create the external ramp from RTCT should have a sufficiently high gain (>200) so as to minimize the required base current. Whatever base current is required reduces the charging current into RTCT and will reduce the oscillator frequency.

#### **Fault Conditions**

A Fault condition occurs if VREF falls below 4.65V. When a Fault is detected OUT is disabled. When VREF exceeds 4.80V, the Fault condition clears, and OUT is enabled.

### **Ground Plane Requirements**

Careful layout is essential for satisfactory operation of the device. A good ground plane must be employed. A unique section of the ground plane must be designated for high di/dt currents associated with the output stage. V<sub>DD</sub> should be bypassed directly to GND with good high frequency capacitors.

### References

[1] Ridley, R., "A New Continuous-Time Model for Current Mode Control", IEEE Transactions on Power Electronics, Vol. 6, No. 2, April 1991.

intersil

FN9238.0

October 19, 2005

10

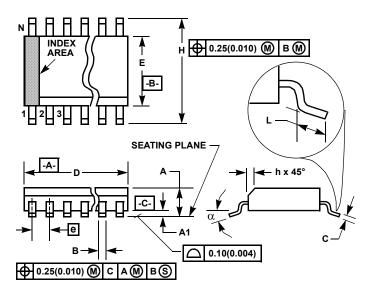

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M8.15 (JEDEC MS-012-AA ISSUE C) 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC    | INCHES |      | MILLIMETERS |       |

|--------|--------|--------|------|-------------|-------|

| SYMBOL | MIN    | MAX    | MIN  | MAX         | NOTES |

| Α      | 0.0532 | 0.0688 | 1.35 | 1.75        | -     |

| A1     | 0.0040 | 0.0098 | 0.10 | 0.25        | -     |

| В      | 0.013  | 0.020  | 0.33 | 0.51        | 9     |

| С      | 0.0075 | 0.0098 | 0.19 | 0.25        | -     |

| D      | 0.1890 | 0.1968 | 4.80 | 5.00        | 3     |

| Е      | 0.1497 | 0.1574 | 3.80 | 4.00        | 4     |

| е      | 0.050  | BSC    | 1.27 | BSC         | -     |

| Н      | 0.2284 | 0.2440 | 5.80 | 6.20        | -     |

| h      | 0.0099 | 0.0196 | 0.25 | 0.50        | 5     |

| L      | 0.016  | 0.050  | 0.40 | 1.27        | 6     |

| N      | 8      | 3      | 8    |             | 7     |

| α      | 0°     | 8°     | 0°   | 8°          | -     |

Rev. 1 6/05

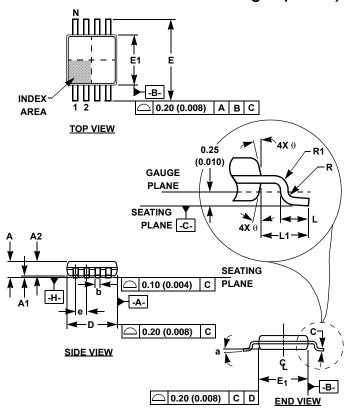

## Mini Small Outline Plastic Packages (MSOP)

## M8.118 (JEDEC MO-187AA) 8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE

|        | INC            | INCHES          |                | MILLIMETERS     |       |  |

|--------|----------------|-----------------|----------------|-----------------|-------|--|

| SYMBOL | MIN            | MAX             | MIN            | MAX             | NOTES |  |

| Α      | 0.037          | 0.043           | 0.94           | 1.10            | -     |  |

| A1     | 0.002          | 0.006           | 0.05           | 0.15            | -     |  |

| A2     | 0.030          | 0.037           | 0.75           | 0.95            | -     |  |

| b      | 0.010          | 0.014           | 0.25           | 0.36            | 9     |  |

| С      | 0.004          | 0.008           | 0.09           | 0.20            | -     |  |

| D      | 0.116          | 0.120           | 2.95           | 3.05            | 3     |  |

| E1     | 0.116          | 0.120           | 2.95           | 3.05            | 4     |  |

| е      | 0.026          | 0.026 BSC       |                | BSC             | -     |  |

| E      | 0.187          | 0.199           | 4.75           | 5.05            | -     |  |

| L      | 0.016          | 0.028           | 0.40           | 0.70            | 6     |  |

| L1     | 0.037 REF      |                 | 0.95           | REF             | -     |  |

| N      | 8              | 8               |                | 3               | 7     |  |

| R      | 0.003          | -               | 0.07           | -               | -     |  |

| R1     | 0.003          | -               | 0.07           | -               | -     |  |

| 0      | 5 <sup>0</sup> | 15 <sup>0</sup> | 5 <sup>0</sup> | 15 <sup>0</sup> | -     |  |

| α      | 0°             | 6 <sup>0</sup>  | 0°             | 6 <sup>0</sup>  | -     |  |

Rev. 2 01/03

#### NOTES:

- These package dimensions are within allowable dimensions of JEDEC MO-187BA.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- Dimension "D" does not include mold flash, protrusions or gate burrs and are measured at Datum Plane. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E1" does not include interlead flash or protrusions and are measured at Datum Plane. - H- Interlead flash and protrusions shall not exceed 0.15mm (0.006 inch) per side.

- 5. Formed leads shall be planar with respect to one another within 0.10mm (0.004) at seating Plane.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm (0.003 inch) total in excess of "b" dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm (0.0027 inch).

- 10. Datums -A and -B to be determined at Datum plane -H .

- Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

## Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com