## W163

# Spread Aware™, Zero Delay Buffer

#### **Features**

- Spread Aware™—designed to work with SSFTG reference signals

- Outputs may be three-stated

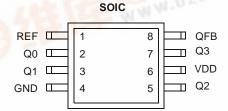

- Available in 8-pin SOIC package

- Extra strength output drive available (-15 version)

- Internal feedback maximized the number of outputs available in 8-pin package

## **Key Specifications**

| Operating Voltage:     | 3.3V±10%                        |

|------------------------|---------------------------------|

| Operating Range:       | 10 < f <sub>OUT</sub> < 133 MHz |

| Cycle-to-Cycle Jitter: | 200 ps                          |

| Output-to-Output Skew: | 250 ps                          |

| Device-to-Device Skew: | 700 ps                          |

| Propagation Delay:     | 350 ps                          |

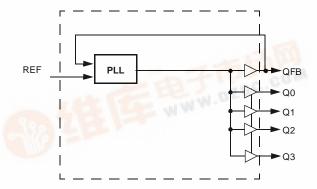

## **Block Diagram**

## **Pin Configuration**

Spread Aware is a trademark of Cypress Semiconductor Corporation.

#### **Pin Definitions**

| Pin Name | Pin No.    | Pin<br>Type | Pin Description                                                                                                                                                         |

|----------|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF      | 1          | I           | Reference Input: The output signals Q0:3 will be synchronized to this signal unless the device is programmed to bypass the PLL.                                         |

| Q0:3     | 2, 3, 5, 7 | 0           | Outputs: These signals will be synchronous and of equal frequency to the signal input at pin 1.                                                                         |

| QFB      | 8          | 0           | <b>Feedback Output:</b> This output signal does not vary from signals Q0:3 in function, but is noted as the signal used to establish the propagation delay of nearly 0. |

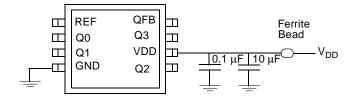

| VDD      | 6          | Р           | <b>Power Connections:</b> Connect to 3.3V. Use ferrite beads to help reduce noise for optimal jitter performance.                                                       |

| GND      | 4          | Р           | <b>Ground Connections:</b> Connect all grounds to the common system ground plane.                                                                                       |

#### Overview

The W163 products are five-output zero delay buffers. A Phase-Locked Loop (PLL) is used to take a time-varying signal and provide five copies of that same signal out. The internal feedback to the PLL provides outputs in phase with the reference inputs.

### **Spread Aware**

Many systems being designed now utilize a technology called Spread Spectrum Frequency Timing Generation. Cypress has been one of the pioneers of SSFTG development, and we designed this product so as not to filter off the Spread Spectrum feature of the Reference input, assuming it exists. When a zero delay buffer is not designed to pass the SS feature through,

the result is a significant amount of tracking skew which may cause problems in systems requiring synchronization.

For more details on Spread Spectrum timing technology, please see the Cypress Application note titled, "EMI Suppression Techniques with Spread Spectrum Frequency Timing Generator (SSFTG) ICs."

#### **Schematic**

## **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                         | Description                            | Rating       | Unit |

|-----------------------------------|----------------------------------------|--------------|------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>                  | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>                    | Operating Temperature                  | 0 to +70     | °C   |

| T <sub>B</sub>                    | Ambient Temperature under Bias         | -55 to +125  | °C   |

| P <sub>D</sub>                    | Power Dissipation                      | 0.5          | W    |

## DC Electrical Characteristics: T<sub>A</sub> =0°C to 70°C, V<sub>DD</sub> = 3.3V ±10%

| Parameter       | Description         | Test Condition                                                 | Min | Тур | Max | Unit |

|-----------------|---------------------|----------------------------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub> | Supply Current      | Unloaded, 100 MHz                                              |     |     | 40  | mA   |

| V <sub>IL</sub> | Input Low Voltage   |                                                                |     |     | 0.8 | V    |

| V <sub>IH</sub> | Input High Voltage  |                                                                | 2.0 |     |     | V    |

| V <sub>OL</sub> | Output Low Voltage  | $I_{OL} = 12 \text{ mA (-15)}$<br>$I_{OL} = 8 \text{ mA (-5)}$ |     |     | 0.4 | V    |

| V <sub>OH</sub> | Output High Voltage | I <sub>OL</sub> = 12 mA (-15)<br>I <sub>OL</sub> = 8 mA (-5)   | 2.4 |     |     | V    |

| I <sub>IL</sub> | Input Low Current   | $V_{IN} = 0V$                                                  |     |     | 50  | μΑ   |

| I <sub>IH</sub> | Input High Current  | $V_{IN} = V_{DD}$                                              |     |     | 100 | μΑ   |

## AC Electrical Characteristics: $T_A = 0$ °C to +70°C, $V_{DD} = 3.3 V \pm 10\%$

| Parameter          | Description                           | Test Condition                               | Min  | Тур | Max | Unit |

|--------------------|---------------------------------------|----------------------------------------------|------|-----|-----|------|

| f <sub>IN</sub>    | Input Frequency                       |                                              | 10   |     | 133 | MHz  |

| f <sub>OUT</sub>   | Output Frequency                      | 15-pF load <sup>[5]</sup>                    | 10   |     | 133 | MHz  |

| t <sub>R</sub>     | Output Rise Time (-05) <sup>[1]</sup> | 2.0 to 0.8V, 15-pF load                      |      |     | 2.5 | ns   |

|                    | Output Rise Time (-15) <sup>[1]</sup> | 2.0 to 0.8V, 20-pF load                      |      |     | 1.5 | ns   |

| t <sub>F</sub>     | Output Fall Time (-05) <sup>[1]</sup> | 2.0 to 0.8V, 15-pF load                      |      |     | 2.5 | ns   |

|                    | Output Rise Time (-15) <sup>[1]</sup> | 2.0 to 0.8V, 20-pF load                      |      |     | 1.5 | ns   |

| t <sub>ICLKR</sub> | Input Clock Rise Time <sup>[1]</sup>  |                                              |      |     | ?   | ns   |

| t <sub>ICLKF</sub> | Input Clock Fall Time <sup>[1]</sup>  |                                              |      |     | ?   | ns   |

| t <sub>PD</sub>    | FBIN to REF Skew <sup>[2, 3]</sup>    | Measured at V <sub>DD</sub> /2               | -350 | 0   | 350 | ps   |

| t <sub>SK</sub>    | Output to Output Skew                 | All outputs loaded equally                   | -250 | 0   | 250 | ps   |

| t <sub>SKDD</sub>  | Device to Device Skew                 | Measured at FBIN pins,<br>V <sub>DD</sub> /2 | -700 | 0   | 700 | ps   |

| t <sub>D</sub>     | Duty Cycle                            | 15-pF load <sup>[4]</sup>                    | 45   | 50  | 55  | %    |

| t <sub>LOCK</sub>  | PLL Lock Time                         | Power supply stable and                      |      |     | 1.0 | ms   |

| t <sub>JC</sub>    | Jitter, Cycle-to-Cycle                |                                              |      |     | 200 | ps   |

#### Notes:

- Longer input rise and fall time will degrade skew and jitter performance.

- All AC specifications are measured with a  $50\Omega$  transmission line, load terminated with  $50\Omega$  to 1.4V. Skew is measured at 1.4V on rising edges. Duty cycle is measured at 1.4V. For the higher drive -15, the load is 20 pF.

### **Ordering Information**

| Ordering Code | Option   | Package<br>Name | Package Type                 |

|---------------|----------|-----------------|------------------------------|

| W163          | -05, -15 | G               | 8-pin Plastic SOIC (150-mil) |

Document #: 38-00787-\*A

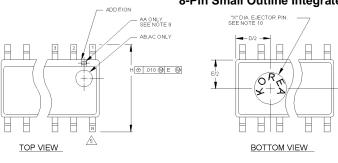

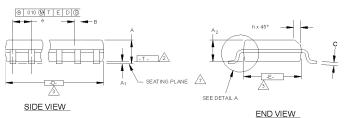

## Package Diagram

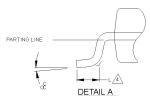

#### 8-Pin Small Outline Integrated Circuit (SOIC, 150-mil)

- NOTES:

- 小 MAXIMUM DIE THICKNESS ALLOWABLE IS .015.

- 2 DIMENSIONING & TOLERANCES PER ANSI.Y14.5M 1982.

- 3. "T" IS A REFERENCE DATUM.

- 4 "D" & "E" ARE REFERENCE DATUMS AND DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS, BUT

DOES INCLUDE MOLD MISMATCH AND ARE MEASURED

AT THE MOLD PARTING LINE. MOLD FLASH OR

PROTRUSIONS SHALL NOT EXCEED 0.006 INCHES PER SIDE.

- 5 "L" IS THE LENGTH OF TERMINAL FOR SOLDERING TO A SUBSTRATE

- 6. "N" IS THE NUMBER OF TERMINAL POSITIONS.

- TERMINAL POSITIONS ARE SHOWN FOR REFERENCE ONLY.

- 8 FORMED LEADS SHALL BE PLANAR WITH RESPECT TO ONE ANOTHER WITHIN .003 INCHES AT SEATING PLANE.

- 9. THE APPEARANCE OF PIN #1 I.D ON THE 8 LD IS OPTIONAL,

ROUND TYPE ON SINGLE LEADFRAME AND RECTANGULAR

TYPE ON MATRIX LEADFRAME.

10. COUNTRY OF ORIGIN LOCATION AND EJECTOR

PIN ON PACKAGE BOTTOM IS OPTIONAL AND

DEPEND ON ASSEMBLY LOCATION.

- 11, CONTROLLING DIMENSION: INCHES.

#### THIS TABLE IN INCHES

| S      | COMMON         |            |       |                | NOTE   |      | 3    |      | 5  |

|--------|----------------|------------|-------|----------------|--------|------|------|------|----|

| M<br>B | D              | DIMENSIONS |       | N <sub>O</sub> | VARI-  | D    |      |      | N  |

| °L     | MIN.           | NOM.       | MAX.  | T <sub>E</sub> | ATIONS | MIN. | NOM. | MAX. |    |

| A      | .061           | .064       | .068  |                | AA     | .189 | .194 | .196 | 8  |

| A,     | .004           | .006       | .0098 |                | AB     | .337 | .342 | .344 | 14 |

| $A_2$  | .055           | .058       | .061  |                | AC     | .386 | .391 | .393 | 16 |

| В      | .0138          | .016       | .0192 |                |        |      |      |      |    |

| С      | .0075          | .008       | .0098 |                |        |      |      |      |    |

|        | SEE VARIATIONS |            | 3     |                |        |      |      |      |    |

| E      | .150           | .155       | .157  |                |        |      |      |      |    |

| е      |                | .050 BSC   |       |                |        |      |      |      |    |

| Н      | .230           | .236       | .244  |                |        |      |      |      |    |

| h      | .010           | .013       | .016  |                |        |      |      |      |    |

| L      | .016           | .025       | .035  |                |        |      |      |      |    |

| Ŋ      | SEE VARIATIONS |            | 5     |                |        |      |      |      |    |

| oκ     | 0°             | 5°         | 8°    |                |        |      |      |      |    |

| Χ      | .085           | .093       | .100  |                |        |      |      |      |    |

#### THIS TABLE IN MILLIMETERS

| S      |                | COMMON     |      |                | NOTE    |      | 3    |      | 5  |

|--------|----------------|------------|------|----------------|---------|------|------|------|----|

| M<br>B | D              | DIMENSIONS |      | N O            | VARI- D |      |      |      | N  |

| 2      | MIN.           | NOM.       | MAX. | T <sub>E</sub> | ATIONS  | MIN. | NOM. | MAX. |    |

| Α      | 1.55           | 1.63       | 1.73 |                | AA      | 4.80 | 4.93 | 4.98 | 8  |

| A.     | 0.127          | 0.15       | 0.25 |                | AB      | 8.58 | 8.69 | 8.74 | 14 |

| $A_2$  | 1.40           | 1.47       | 1.55 |                | AC      | 9.80 | 9.93 | 9.98 | 16 |

| В      | 0.35           | 0.41       | 0.49 |                |         |      |      |      |    |

| С      | 0.19           | 0.20       | 0.25 |                |         |      |      |      |    |

| D      | SEE VARIATIONS |            | 3    |                |         |      |      |      |    |

| E      | 3.81           | 3.94       | 3.99 |                |         |      |      |      |    |

| е      |                | 1.27 BSC   |      |                |         |      |      |      |    |

| H      | 5.84           | 5.99       | 6.20 |                |         |      |      |      |    |

| h      | 0.25           | 0.33       | 0.41 |                |         |      |      |      |    |

| L      | 0.41           | 0.64       | 0.89 |                |         |      |      |      |    |

| N<br>& | SEE VARIATIONS |            | 5    |                |         |      |      |      |    |

| œ      | 0°             | 5°         | 8°   |                |         |      |      |      |    |

| X      | 2 16           | 2.36       | 2.54 |                |         |      |      |      |    |